生产后的中度复杂的印刷电路板(PCB)传统上使用在线测试(ICT)和功能测试来进行检测。其它的测试方法,例如昂贵的光学和X光检查,经常是必须的,以来验证BGA被正确地放置。然而,JTAG边界扫描可以取代ICT,以作为功能测试的自然配对物,并且使光学与X光检查不再必要。

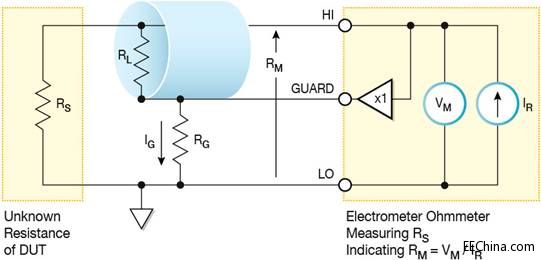

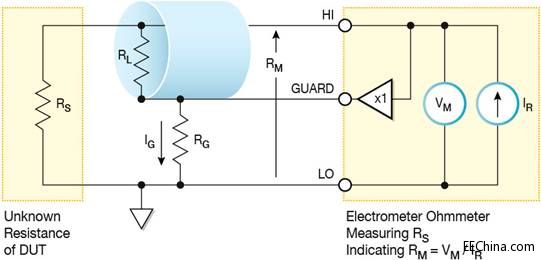

ICT是一个隔离测试每个部件或者连接的方法。其使用例如用于简单模拟部件的保护技术等技术。通过针床或者飞针对被测设备表面节点的访问,被用来验证与这些节点相连的已安装的部件的正确性。

图1.使用保护技术测量电阻

尽管这类测试验证了每个单一部件的正确性,它却不能够验证一个板卡,当通电时,是否能作为一个整体正常运行。想要做到这点就必须进行功能测试。

尽管新测试方法在繁衍,功能测试依然是认定电子系统和板卡正常运行的支柱。从概念上来讲,这类测试非常简单-它在于检测一个被测单元是否真正做到它所被设计的那样。一个针床装置也被融合进来以提供测试访问。这个测试方法的中心单独来讲是有些局限的,因为我们只能确认每个系统运行正常,而不是被隔离的单独部件

图2,一个典型的功能测试装置

功能测试的一个特征是它可能需要集成许多仪器到测试平台上。假设,例如,您需要测试一个被设计用来处理和无线通讯的板卡。为了执行功能测试,您需要使用其它与测试装置有关的仪器例如电源,数字和模拟I/O,RF分析仪器(频谱和矢量分析器,收发器,等等),与快速采集设备(示波器和数字转换器)来激发和读取单个信号。

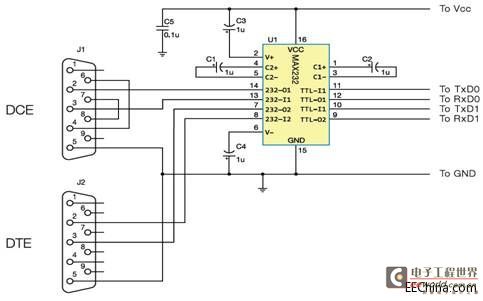

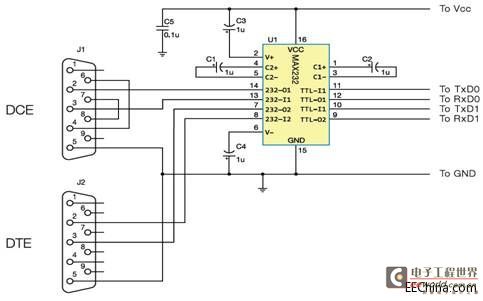

或许一个例子最能揭示ICT与功能测试的区别。考虑一个串联接口的MAX202驱动(见图3)。ICT可能与检查充电泵里电容的值有关,从而确认每个部件在隔离下运转正常,而功能测试则可能会检查发送和接收整个数据包。

图3.MAX232驱动典型的连接图

直到最近,ICT才允许在执行功能测试之前,容易地验证所有部件的正确安装。然而,近来可达到部件密度的增长意味着PCB设计会经常不允许布置足够数量的测试点。尤其是BGA部件的针脚在被焊接下后,完全不能被ICT访问。其结果是ICT性价比越来越差,越来越不可持续,并且增加产品交货期。这个问题最有革新的方案是边界扫描。

JTAG边界扫描

JTAG边界扫描是一个电子测试方法,被设计用来克服通常与复杂的、高密度板卡所相关的测试访问问题。边界扫描,按照IEEE 1149.x标准,提供了芯片中一个可以使综合数字测试协议在板卡层面就可适用的的电子线路。

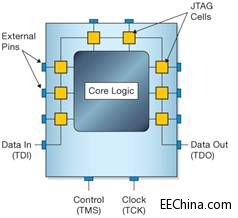

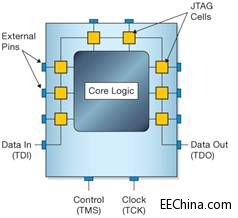

这个线路把用在ICT中的物理探点用边界扫描单元来替代。它们存在于器件核心逻辑与外部针脚之间,可以在芯片上每个输入与输出处捕获或者驱入信号。

边界扫描单元可以在一个物理探头不能达到的地方提供虚拟探点,例如BGA下的焊点连接。一些细间距引线器件不能用物理探头可靠地检测,不过边界扫描再一次可以为这些针脚提供数字测试访问。

在器件的正常运作下,边界扫描单元如透明一般。它们可以捕获通过它们的数值,使可以观测数据流,而不改变通过它们的信号成为可能。当一序列正确的指令 被送到控制针脚(测试模式选择,TMS)上时,边界扫描单元还可以通过与它们相连的针脚驱动出数值,像一个物理探点或者探针一样激发电路。这允许工程师们, 用之前ICT测试同样的方式,来验证所有部件适当的互连(轨迹间短路的缺乏与连续性的验证),以及这些器件的正确行为。[page]

图4.边界扫描部件的简化图

边界扫描单元形成了一个串联的扫描路径,称为边界扫描寄存器。一序列需要写入的数值可以通过TDI针脚被同步入这个寄存器中,而且一旦数据被边界扫描单元捕获,它可以通过TDO针脚被同步出去。JTAG器件可以被连接起来形成一个JTAG链。链中一个器件上的TDO针脚与另一个器件上的TDI针脚相连形成一个单一的寄存器。控制和时钟信号(TMS和TCK)为链中的每个器件所共有。

正因为如此,ICT可以在一定程度上或者完全被侵入性更小的边界扫描测试所取代,使用边界扫描单元来代替物理探针。每个JTAG链都需要一个适当的测试访问端口(TAP),包含四个针脚(TDI,TDO,TMS与TCK,以及一个可选的第五个TRST针脚)在一个外部连接器上。这与一个JTAG控制器相连,通常是一个伴有边界扫描软件套装的小型USB硬件。

虽然JTAG边界扫描被发现可以提高整体测试访问,因而覆盖率,但是它是一个数字协议,所以并不能直接测试模拟部分。边界扫描访问仅限于带有至少一个JTAG器件的网(及与之相连的部件)。许多主导的JTAG边界扫描系统含有“可测试设计”工具。它可以在设计阶段显示一个板卡的测试覆盖率,突出显示板卡上没有足够JTAG访问的区域。在这个阶段,或许可以将一个不支持JTAG的器件用一个支持的替换,以增加测试覆盖率。

新方法:使边界扫描与功能测试相结合

想要全面地测试一个系统,边界扫描测试必须与功能测试一起运行。边界扫描与ICT一样,只能验证每个部件放置正确以及运行正常。它不会验证整个电路像设计的一样工作。

当把ICT与功能测试(生产结束时最常见的)相结合时,工程师几乎总会发现它们在两个不同的工作台上测试。因为对于每个JTAG链只需要一个单一连接器上的4个针脚,把边界扫描融入到一个功能测试装置上非常容易,并且能节约宝贵的时间与精力。事实上一些电子测试专家已经开始开发可以把功能和边界扫描集成到一个工作台的装置和测试台,以提供具有竞争力的总体成本以及开发时间的、更完全的设备。

图5(左)已将被测设备插入的集成功能测试与边界扫描测试装置

图6(右)装置内部,功能测试设备与边界扫描测试接口相集成的地方。

最大效率

集合功能与边界扫描测试于一个系统带来大量的和重要的好处。两个方法相互补充,在于弥补每个技术可能的缺陷,以带来更高的可靠性与有效性。两个一起使用可能创造其它方式不可能取得的、良好的测试条件。

例如,通过用于功能测试的探针的激发,可能生成能被边界扫描链所验证的模式,然后可以激活电路中可以被功能测试所验证的部分。集成方法的有效性意味着您不仅可以从一个设备中运行两种测试类型,还意味着这些测试为板卡的设计与生产提供了更大的把握。

这些益处可以从一个测试直接与FPGA相连的DAC的简单例子中看到。使用边界扫描可以恰当地驱动FPGA的I/O来为DAC的模拟输出编程,从而可以通过功能测试被捕获板测量到。另一方面,如果我们考虑一个与FPGA直接相交互的ADC,在功能测试中可以使用一个生成卡来激活前者,然后使用边界扫描来检测被ADC读数所编译的位元。

以上的集成方法允许工程师们达到:

目前有可用的强大的工具来允许您拥有交互的硬件以及执行测试序列的开发环境,以用于集成测试系统的开发。只要简单地把PXI JTAG模块装进PXI架里,它就能允许与边界扫描链的交互。它可以和适用于具体应用的功能测试的几个硬件装备在一起。

尽管边界扫描测试序列的开发应该用专业的工具(一个JTAG开发环境)来进行,生成的序列不仅可以与为功能测试所开发的序列相关联,您还可以共同管理序列中提供两类测试交互的部分。这样,一旦功能和边界扫描序列开发完成,并且集成一起,操作员接口将会被独特地定制。

通过选择一个可以允许不同类型硬件容易的结合模块测试系统,包括第三方所开发的,您就有一个可以轻松升级与配置的、集成功能和边界扫描测试的单一工作台,不仅可以提供测试的可靠性,而且减少他们的成本与时间。

什么是边界扫描?

硅设计方面的进步,例如增加器件密度和最近的BGA封装,使传统测试方法的功效大打折扣。为了克服这些问题,一些世界领先的硅生产商联合起来成立了联合测试小组。

这个小组的研究发现和建议被用来作为IEEE 1149.1标准,即标准测试访问端口和边界扫描结构的基础。这个标准保留了和这个小组的联系并且以缩写JTAG被大家所俗知。

JTAG边界扫描是一项被设计用来克服通常与复杂的、高密度的板相关联之类的测试访问问题的测试技术。通过激发位于例如FPGA与CPLD部件上的边界扫描单元,工程师们可以用一个JTAG控制器对电路进行数码地测试,并且使用强大的软件套装来精确地找到故障的位置与原因。

因为不再需要测试点,与ITC和功能测试相关的物理访问问题不再是一个问题。测试系统与边界扫描单元只通过一个4-5线测试总线相连。这必须在板卡设计中被考虑进来以确保可测性。许多领先的JTAG边界扫描系统销售商提供可测性设计指南来鼓励设计工程师们去这样做。

它是如何工作的?

所有器件核心逻辑与针脚间的信号都被一个称为边界扫描寄存器(Boundary Scan Register --- BSR)的串联扫描路径所截获。在正常工作模式下,边界扫描单元是隐形的,而在测试模式下,这些单元可以被用来设置和/或读取数值。在边界扫描过程中,一系列4-5个不同的信号被用来回报电路的性能。

关键字:JTAG 边界扫描 功能测试

引用地址:使JTAG边界扫描与功能测试相结合

ICT是一个隔离测试每个部件或者连接的方法。其使用例如用于简单模拟部件的保护技术等技术。通过针床或者飞针对被测设备表面节点的访问,被用来验证与这些节点相连的已安装的部件的正确性。

图1.使用保护技术测量电阻

尽管这类测试验证了每个单一部件的正确性,它却不能够验证一个板卡,当通电时,是否能作为一个整体正常运行。想要做到这点就必须进行功能测试。

尽管新测试方法在繁衍,功能测试依然是认定电子系统和板卡正常运行的支柱。从概念上来讲,这类测试非常简单-它在于检测一个被测单元是否真正做到它所被设计的那样。一个针床装置也被融合进来以提供测试访问。这个测试方法的中心单独来讲是有些局限的,因为我们只能确认每个系统运行正常,而不是被隔离的单独部件

图2,一个典型的功能测试装置

功能测试的一个特征是它可能需要集成许多仪器到测试平台上。假设,例如,您需要测试一个被设计用来处理和无线通讯的板卡。为了执行功能测试,您需要使用其它与测试装置有关的仪器例如电源,数字和模拟I/O,RF分析仪器(频谱和矢量分析器,收发器,等等),与快速采集设备(示波器和数字转换器)来激发和读取单个信号。

或许一个例子最能揭示ICT与功能测试的区别。考虑一个串联接口的MAX202驱动(见图3)。ICT可能与检查充电泵里电容的值有关,从而确认每个部件在隔离下运转正常,而功能测试则可能会检查发送和接收整个数据包。

图3.MAX232驱动典型的连接图

直到最近,ICT才允许在执行功能测试之前,容易地验证所有部件的正确安装。然而,近来可达到部件密度的增长意味着PCB设计会经常不允许布置足够数量的测试点。尤其是BGA部件的针脚在被焊接下后,完全不能被ICT访问。其结果是ICT性价比越来越差,越来越不可持续,并且增加产品交货期。这个问题最有革新的方案是边界扫描。

JTAG边界扫描

JTAG边界扫描是一个电子测试方法,被设计用来克服通常与复杂的、高密度板卡所相关的测试访问问题。边界扫描,按照IEEE 1149.x标准,提供了芯片中一个可以使综合数字测试协议在板卡层面就可适用的的电子线路。

这个线路把用在ICT中的物理探点用边界扫描单元来替代。它们存在于器件核心逻辑与外部针脚之间,可以在芯片上每个输入与输出处捕获或者驱入信号。

边界扫描单元可以在一个物理探头不能达到的地方提供虚拟探点,例如BGA下的焊点连接。一些细间距引线器件不能用物理探头可靠地检测,不过边界扫描再一次可以为这些针脚提供数字测试访问。

在器件的正常运作下,边界扫描单元如透明一般。它们可以捕获通过它们的数值,使可以观测数据流,而不改变通过它们的信号成为可能。当一序列正确的指令 被送到控制针脚(测试模式选择,TMS)上时,边界扫描单元还可以通过与它们相连的针脚驱动出数值,像一个物理探点或者探针一样激发电路。这允许工程师们, 用之前ICT测试同样的方式,来验证所有部件适当的互连(轨迹间短路的缺乏与连续性的验证),以及这些器件的正确行为。[page]

图4.边界扫描部件的简化图

边界扫描单元形成了一个串联的扫描路径,称为边界扫描寄存器。一序列需要写入的数值可以通过TDI针脚被同步入这个寄存器中,而且一旦数据被边界扫描单元捕获,它可以通过TDO针脚被同步出去。JTAG器件可以被连接起来形成一个JTAG链。链中一个器件上的TDO针脚与另一个器件上的TDI针脚相连形成一个单一的寄存器。控制和时钟信号(TMS和TCK)为链中的每个器件所共有。

正因为如此,ICT可以在一定程度上或者完全被侵入性更小的边界扫描测试所取代,使用边界扫描单元来代替物理探针。每个JTAG链都需要一个适当的测试访问端口(TAP),包含四个针脚(TDI,TDO,TMS与TCK,以及一个可选的第五个TRST针脚)在一个外部连接器上。这与一个JTAG控制器相连,通常是一个伴有边界扫描软件套装的小型USB硬件。

虽然JTAG边界扫描被发现可以提高整体测试访问,因而覆盖率,但是它是一个数字协议,所以并不能直接测试模拟部分。边界扫描访问仅限于带有至少一个JTAG器件的网(及与之相连的部件)。许多主导的JTAG边界扫描系统含有“可测试设计”工具。它可以在设计阶段显示一个板卡的测试覆盖率,突出显示板卡上没有足够JTAG访问的区域。在这个阶段,或许可以将一个不支持JTAG的器件用一个支持的替换,以增加测试覆盖率。

新方法:使边界扫描与功能测试相结合

想要全面地测试一个系统,边界扫描测试必须与功能测试一起运行。边界扫描与ICT一样,只能验证每个部件放置正确以及运行正常。它不会验证整个电路像设计的一样工作。

当把ICT与功能测试(生产结束时最常见的)相结合时,工程师几乎总会发现它们在两个不同的工作台上测试。因为对于每个JTAG链只需要一个单一连接器上的4个针脚,把边界扫描融入到一个功能测试装置上非常容易,并且能节约宝贵的时间与精力。事实上一些电子测试专家已经开始开发可以把功能和边界扫描集成到一个工作台的装置和测试台,以提供具有竞争力的总体成本以及开发时间的、更完全的设备。

图5(左)已将被测设备插入的集成功能测试与边界扫描测试装置

图6(右)装置内部,功能测试设备与边界扫描测试接口相集成的地方。

最大效率

集合功能与边界扫描测试于一个系统带来大量的和重要的好处。两个方法相互补充,在于弥补每个技术可能的缺陷,以带来更高的可靠性与有效性。两个一起使用可能创造其它方式不可能取得的、良好的测试条件。

例如,通过用于功能测试的探针的激发,可能生成能被边界扫描链所验证的模式,然后可以激活电路中可以被功能测试所验证的部分。集成方法的有效性意味着您不仅可以从一个设备中运行两种测试类型,还意味着这些测试为板卡的设计与生产提供了更大的把握。

这些益处可以从一个测试直接与FPGA相连的DAC的简单例子中看到。使用边界扫描可以恰当地驱动FPGA的I/O来为DAC的模拟输出编程,从而可以通过功能测试被捕获板测量到。另一方面,如果我们考虑一个与FPGA直接相交互的ADC,在功能测试中可以使用一个生成卡来激活前者,然后使用边界扫描来检测被ADC读数所编译的位元。

以上的集成方法允许工程师们达到:

- 被测设备(模拟与数字)上和所有网的所有电路全部或者接近全部的覆盖率

- 更短的测试时间-除了边界扫描与功能测试序列被并行执行的事实,考虑在测试台上装载与卸载被测试设备的时间也是必须。很明显它在使用两个工作台的时候是双倍的

- 高性能在线烧录

- 更快,更准确的故障诊断

目前有可用的强大的工具来允许您拥有交互的硬件以及执行测试序列的开发环境,以用于集成测试系统的开发。只要简单地把PXI JTAG模块装进PXI架里,它就能允许与边界扫描链的交互。它可以和适用于具体应用的功能测试的几个硬件装备在一起。

尽管边界扫描测试序列的开发应该用专业的工具(一个JTAG开发环境)来进行,生成的序列不仅可以与为功能测试所开发的序列相关联,您还可以共同管理序列中提供两类测试交互的部分。这样,一旦功能和边界扫描序列开发完成,并且集成一起,操作员接口将会被独特地定制。

通过选择一个可以允许不同类型硬件容易的结合模块测试系统,包括第三方所开发的,您就有一个可以轻松升级与配置的、集成功能和边界扫描测试的单一工作台,不仅可以提供测试的可靠性,而且减少他们的成本与时间。

什么是边界扫描?

硅设计方面的进步,例如增加器件密度和最近的BGA封装,使传统测试方法的功效大打折扣。为了克服这些问题,一些世界领先的硅生产商联合起来成立了联合测试小组。

这个小组的研究发现和建议被用来作为IEEE 1149.1标准,即标准测试访问端口和边界扫描结构的基础。这个标准保留了和这个小组的联系并且以缩写JTAG被大家所俗知。

JTAG边界扫描是一项被设计用来克服通常与复杂的、高密度的板相关联之类的测试访问问题的测试技术。通过激发位于例如FPGA与CPLD部件上的边界扫描单元,工程师们可以用一个JTAG控制器对电路进行数码地测试,并且使用强大的软件套装来精确地找到故障的位置与原因。

因为不再需要测试点,与ITC和功能测试相关的物理访问问题不再是一个问题。测试系统与边界扫描单元只通过一个4-5线测试总线相连。这必须在板卡设计中被考虑进来以确保可测性。许多领先的JTAG边界扫描系统销售商提供可测性设计指南来鼓励设计工程师们去这样做。

它是如何工作的?

所有器件核心逻辑与针脚间的信号都被一个称为边界扫描寄存器(Boundary Scan Register --- BSR)的串联扫描路径所截获。在正常工作模式下,边界扫描单元是隐形的,而在测试模式下,这些单元可以被用来设置和/或读取数值。在边界扫描过程中,一系列4-5个不同的信号被用来回报电路的性能。

上一篇:感测的内容是什么? 用于电容感测的有源屏蔽

下一篇:物联网那么大,如何将测试进行到底

推荐阅读最新更新时间:2024-03-30 22:59

模块电源功能性参数指标及测试方法

模块电源的电气性能是通过一系列测试来呈现的,下列为一般的功能性测试项目,详细说明如下: 电源调整率(Line Regulation) 负载调整率(Load Regulation) 综合调整率(Conmine Regulation) 输出涟波及杂讯(Ripple & Noise) 输入功率及效率(Input Power, Efficiency) 动态负载或暂态负载(Dynamic or Transient Response) 起动(Set-Up)及保持(Hold-Up)时间 常规功能(Functions)测试 1. 电源调整率 电源调整率的定义为电源供应器于输入电压变化时提供其稳定输出电压的能力。测试步骤如下:于

[电源管理]

SWD和JTAG都给关了,程序下载不进去,解决办法

我们有时候会碰到各种问题导致STM32或者STM8的程序突然就下载不进去板子了。可以按照以下步骤来解决。 一、下载方法步骤: 1、将板子供电全部断开,这里包括3.3V电源供电和JLINK等所有能给开发板供上电的设备全断开。 2、找到BOOT0引脚,将BOOT0拉高。 方法:在板子上找一个高电平引脚,手动用导线将BOOT0连接到该引脚上即可。 (注意:我的STM32板子供电是3.3V的,所以我找了一个3.3V的引脚,用导线连接到了BOOT0上,千万别弄错了,电平接高了不小心可是要烧坏板子的!) 3、BOOT0拉高以后,保持这个姿势不要动,打开电源,重新给板子上电。 4、插上JLink或者STLink

[单片机]

基于JTAG的互连测试技术

一、引言 随着微电子技术进入超大规模集成电路(VLSI)时代,VLSI电路的高度复杂性及多层印制板、表面贴装(SMT)、圆片规模集成(WSI)和多芯片模块(MCM)技术在电路系统中的运用,使得电路节点的物理可访问性正逐步削减以至于消失,电路和系统的可测试性急剧下降,测试费用在电路和系统总费用中所占的比例不断上升,常规测试方法正面临着日趋严重的困难。 测试算法的研究和测试实践证明了一个基本的事实:要对一个不具有可观测性的电路进行测试是徒劳的,只有提高电路的可测性设计(design for testability,DFT),才能使电路的测试问题得到简化并最终得到解决。而近年来飞速发展的JTAG边界扫描技术很好的解决了这个

[测试测量]

STM32F103禁用JTAG和SWD接口

查阅数据手册是个好习惯,从数据手册上可知,PA13 PA14 PA15的主功能均是JTAG的接口,其中PA13和PA14还是SWD接口 另外还有PB3和PB4是JTAG接口 当要使用JTAG占用的IO口但还要使用SWD时,也就是要使用PB3、4和PA15当做IO口,但还要使用SWD下载或者调试时,就需要禁用JTAG 标准库使用以下方法: RCC_APB2PeriphClockCmd(RCC_APB2Periph_AFIO, ENABLE); //开启AFIO时钟 GPIO_PinRemapConfig(GPIO_Remap_SWJ_JTAGDisable, ENABLE);//使能JTAGDisable,即禁用JTAG

[单片机]

泰克为PCI Express 3.0测试解决方案增添新功能

泰克公司日前宣布,TLA7SA08 和 TLA7SA16 逻辑协议分析仪模块新增了软件功能,支持下一代PCIe规范,即PCI Express 3.0规范。新的功能包括创新的鸟瞰图(BEV),帮助工程师洞察和分析复杂的流控制问题,并且只需一键式校准和自动配置,从而使PCIe系统调试和分析变得更迅速,更容易。 PCIe 3.0规范支持两倍于上代规范的数据率和更高的I/O带宽,给物理层和协议层带来了新的复杂性和测试挑战。而且,PCIe适用于广泛的应用,这给测试仪器跟踪动态链路宽度变化、动态速度变化、通道(lane)排序、极性变化和多个省电模式等特征带来了压力。凭借这些新功能,泰克逻辑协议分析仪有助于工程师与PCIe 3.0规范保持与时

[测试测量]

氧化锌避雷器测试仪的功能都有哪些

TKBL氧化锌避雷器特性测试仪又称避雷器特性测试仪及氧化锌避雷器特性检测仪,氧化锌避雷器特性测试仪用于氧化锌[MOA]泄漏电流的测量分析,氧化锌避雷器特性测试仪主要是用于测量阻性电流,从而分析氧化锌老化和受潮的程度,既可以现场带电测试也可用于实验室做出厂和验收试验。 TKBL氧化锌避雷器特性测试仪测试功能和条件适用于氧化锌[MOA] 泄漏电流的测量分析,符合中华人民共和国电力行业标准《DL474.5—92现场绝缘试验实施导则—避雷器试验》的要术, 氧化锌避雷器特性测试仪主要是用于测量阻性电流,从而分析氧化锌老化和受潮的程度,既可以现场带电测试也可用于实验室做出厂和验收试验。 氧化锌避雷器特性测试仪测试内部采用双重保护隔离技

[测试测量]

手持式综合布线测试仪的测试功能与标准

手持式综合布线测试仪的主要功能与特点是满足于现场工作的实际需要。在价格,性能和应用等方面会有很大的差别。在综合布线的测试与维护领域,依据它们所进行的测试功能,可以分成三个大类:验证测试,鉴定测试和认证测试。虽然这三个类别的综合布线测试仪在某些功能上可能有重叠,但每个类别的仪器都有其特定的使用目的。 验证综合布线测试仪可以解决的问题是:“线缆连接是否正确?”验证测试仪通常被网络工程师当作解决线缆故障的首选仪器。 鉴定综合布线测试仪可以解决的问题是:“布线系统能支持所选用的网络技术么?例如100Base-Tx,千兆以太网等)”鉴定测试仪功能更全,使得网络工程师可在其帮助下诊断现有布线系统和对交换机端口进行维护

[模拟电子]

多核环境中的高效率调试方法

毫无疑问,多核多线程是未来处理器的发展方向。回首处理器的发展历程,并行技术从指令级的超标量发展到线程级的超线程或者并发多线程,再到今天处理 器级的多内核,总的趋势都没有改变。英特尔、Sun和IBM等大公司目前已经投身到多核或者多线程技术的浪潮之中。当今的网络应用日趋复杂,对性能的要求 不断提高,无论是需求推动技术,还是技术激发了新的需求,并行技术都将是未来信息基础设施建设的必然选择。 对于嵌入式装置而言,多核技术可以提供更高的处理器性能、更有效的电源利用率,并且占用更少的物理空间,因而具有许多单核处理器无法具备的优势。与多核解决方案如影随形的,就是多处理器技术,也就是在同一块电路板或同一个集成系统中包含多个处理器。

[工业控制]

小广播

热门活动

换一批

更多

最新测试测量文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

- EEWorld Datasheet 伴你同行!快来领取200芯积分福利啦~

- 下载有好礼!罗姆带您学习电源设计应用小技巧(功率器件篇)

- 购买TI store MSP432P401R LaunchPad 晒单就送礼!

- 看是德科技利用校准降低仪器测量不确定度、提高测试精度 直播享好礼!

- EEWorld 2018年度最具影响力网友评选

- 下载资料有好礼:超凡富士通存储器FRAM,安全、易写入、低功耗

- 再续点评Vishay视频 抢楼拿奖进行到底

- “玄铁杯”第三届RISC-V应用创新大赛—国产高性能RISC-V Linux开发板LicheePi 4A报名专场,万元奖金,邀您奔赴开源设计盛宴

- 你们想要的XMC4800 Relax EtherCAT Kit来了,速度来申请!

- 3.5\"嵌入式主板给力开团 仅售599元包邮!

厂商技术中心

深度学习轻松学:核心算法与视觉实践 (冯超)

深度学习轻松学:核心算法与视觉实践 (冯超) 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号