逻辑分析仪我也DIY(四)—神秘蓝点

今晚把各个显示的字符都DIY上去了,不过在某些蓝色字符附近出现了许多意外的神秘蓝点,如下:

上面一共四个Ch字符中,只有Ch2是完全没有问题的,特权同学就感觉很纳闷了,为什么同样的16个Ch字符,就这几个出现这些神秘的蓝点。家中的LCD专家还特地给分析了,这个Cha前面的点那是四个像素的蓝点在一起,觉得不是坏点,那一定是认为打上去的。换我的话说,那是FPGA给送上去的点。所以回头来显示走读代码找问题,一通找,最后还是没发现什么不对的地方。因为时序约束后还都有较大的余量,所以这个原因排除,而这个字模是存储在M4K配置的ROM里的,所以问题很可能和它有关系,ROM的配置后又一个可选的输出数据是否要让输入时钟打一拍,默认是打一拍,我一直以为这里的打一拍不打一拍问题不是很大,不打一拍,送完地址的第二个时钟周期出数据,而打一拍应该是送完地址的第三个时钟周期出数据,所以也没太在意。

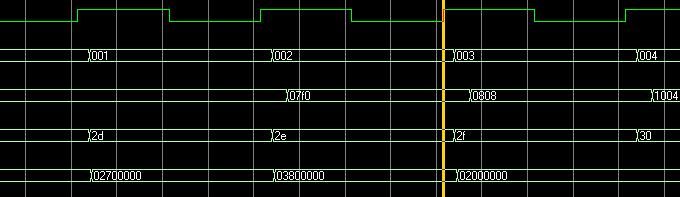

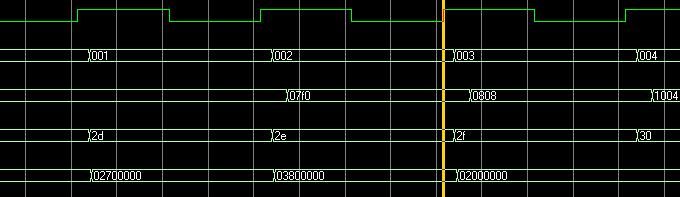

无奈之下只能重新让ModelSim里帮忙找问题,再次进行后仿真,这次就抓住出问题的地方,本想找扫描到的点位置送出来的数据是否正确。结果由于这个时间也太长了,咱等不起,索性就认真的就ROM的时序做起了文章,这一看可不要紧,问题浮出水面。

第1条是ROM的输入时钟;

第2条是ROM1的地址(输出数据没有用时钟打一拍);

第3条是ROM1的输出数据;

第4条是ROM2的地址(输出数据打了一拍);

第5条是ROM2的输出数据。

ROM1里,地址001的数据是0710,地址002的数据是0808;ROM2里地址2d的数据是02000000。我想问题就出来了,对于ROM1在第一个时钟上升沿送完地址后(延时一点到达),第二个时钟上升沿虽然数据出现了,但是我们的时钟是采不到的,它是在第二个时钟上升沿的建立保持时间后才出现在总线上的,所以真正意思上读出数据的时间应该是时钟的第三个上升沿。ROM2也类似,由于内部时钟打了一拍,所以它比ROM1要再慢一个时钟周期。这就是我的问题所在,换句话说,字模数据显示位置整个右移了一个坐标。

随后,地址再早一个时钟周期置位,问题解决了。

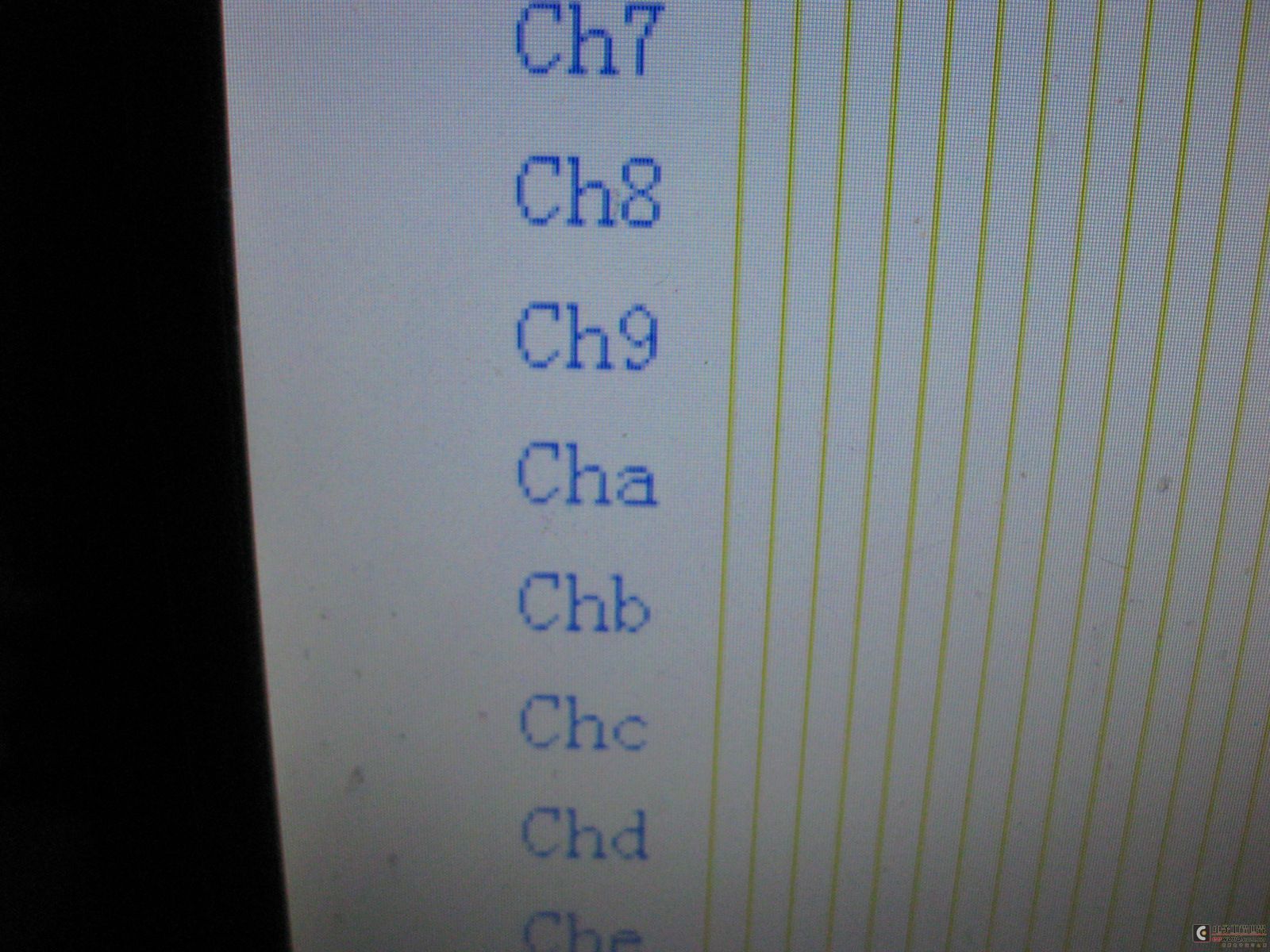

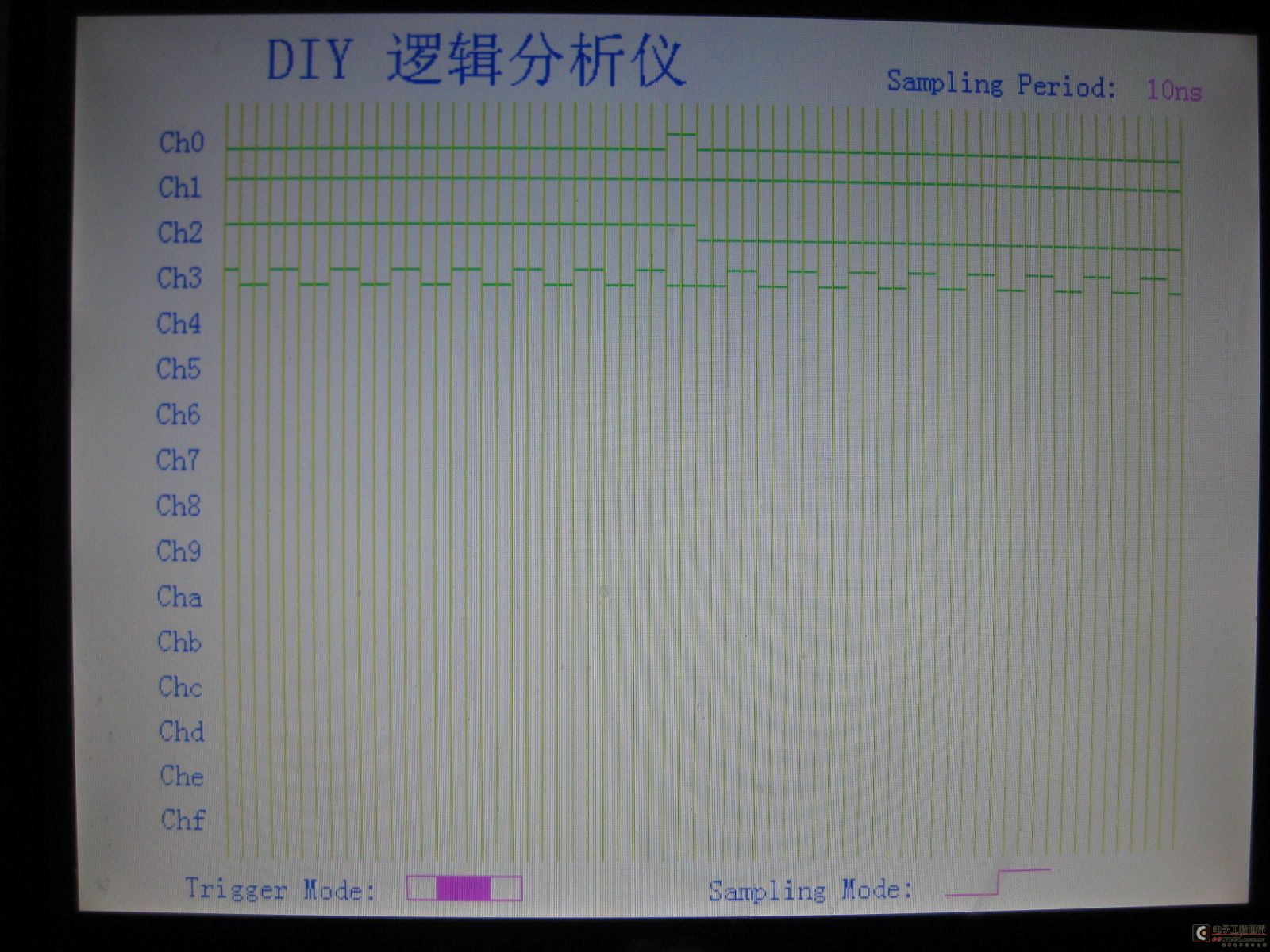

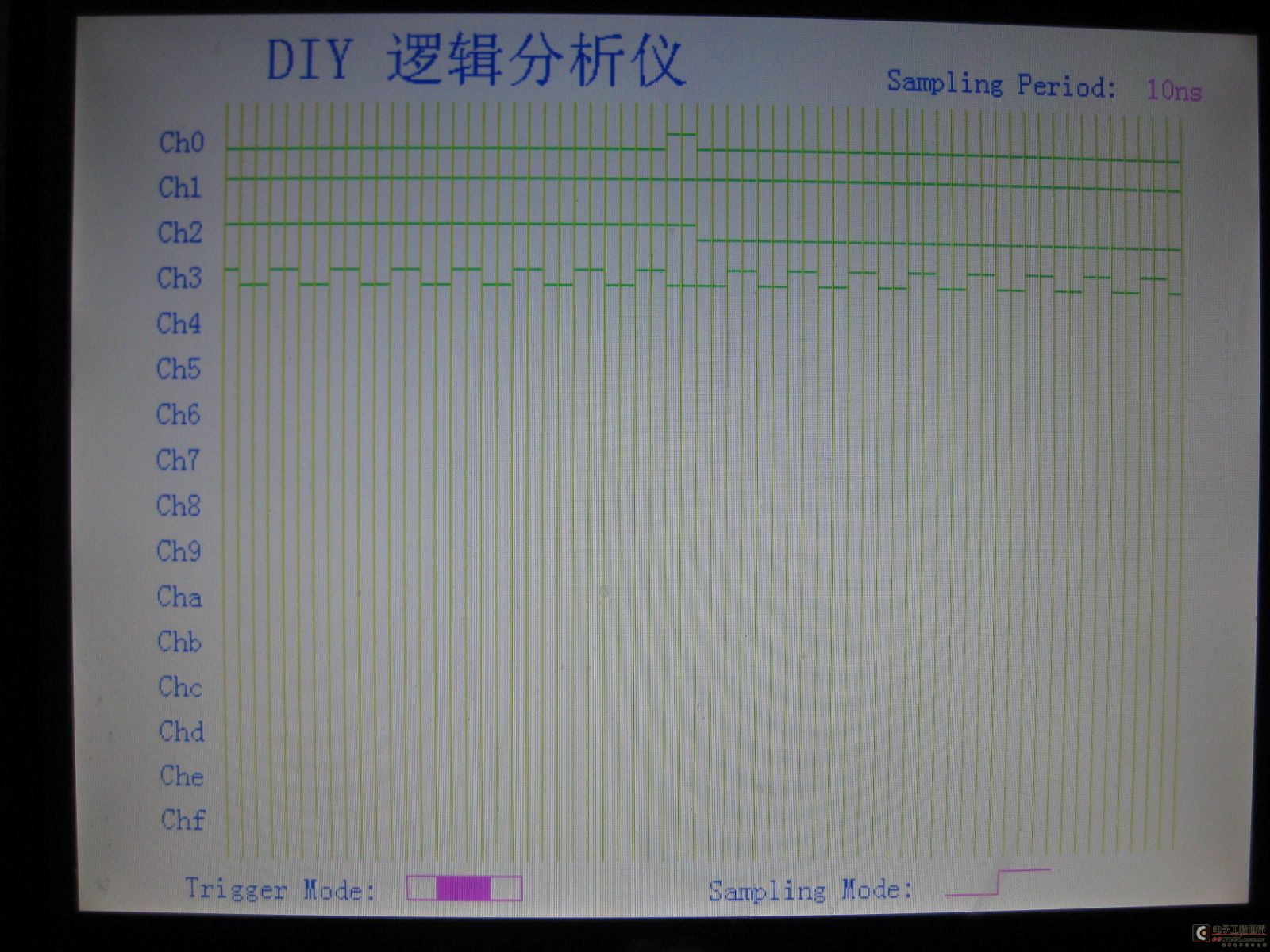

今晚过后,整个就下面的一个效果。

采样模式显示。

采样周期可调,从10ns到100us可调。

三种采样模式显示。

关键字:逻辑分析仪 神秘蓝点

引用地址:逻辑分析仪我也DIY(四)—神秘蓝点

今晚把各个显示的字符都DIY上去了,不过在某些蓝色字符附近出现了许多意外的神秘蓝点,如下:

上面一共四个Ch字符中,只有Ch2是完全没有问题的,特权同学就感觉很纳闷了,为什么同样的16个Ch字符,就这几个出现这些神秘的蓝点。家中的LCD专家还特地给分析了,这个Cha前面的点那是四个像素的蓝点在一起,觉得不是坏点,那一定是认为打上去的。换我的话说,那是FPGA给送上去的点。所以回头来显示走读代码找问题,一通找,最后还是没发现什么不对的地方。因为时序约束后还都有较大的余量,所以这个原因排除,而这个字模是存储在M4K配置的ROM里的,所以问题很可能和它有关系,ROM的配置后又一个可选的输出数据是否要让输入时钟打一拍,默认是打一拍,我一直以为这里的打一拍不打一拍问题不是很大,不打一拍,送完地址的第二个时钟周期出数据,而打一拍应该是送完地址的第三个时钟周期出数据,所以也没太在意。

无奈之下只能重新让ModelSim里帮忙找问题,再次进行后仿真,这次就抓住出问题的地方,本想找扫描到的点位置送出来的数据是否正确。结果由于这个时间也太长了,咱等不起,索性就认真的就ROM的时序做起了文章,这一看可不要紧,问题浮出水面。

第1条是ROM的输入时钟;

第2条是ROM1的地址(输出数据没有用时钟打一拍);

第3条是ROM1的输出数据;

第4条是ROM2的地址(输出数据打了一拍);

第5条是ROM2的输出数据。

ROM1里,地址001的数据是0710,地址002的数据是0808;ROM2里地址2d的数据是02000000。我想问题就出来了,对于ROM1在第一个时钟上升沿送完地址后(延时一点到达),第二个时钟上升沿虽然数据出现了,但是我们的时钟是采不到的,它是在第二个时钟上升沿的建立保持时间后才出现在总线上的,所以真正意思上读出数据的时间应该是时钟的第三个上升沿。ROM2也类似,由于内部时钟打了一拍,所以它比ROM1要再慢一个时钟周期。这就是我的问题所在,换句话说,字模数据显示位置整个右移了一个坐标。

随后,地址再早一个时钟周期置位,问题解决了。

今晚过后,整个就下面的一个效果。

采样模式显示。

采样周期可调,从10ns到100us可调。

三种采样模式显示。

上一篇:“虚拟”逻辑分析仪SignalTap II

下一篇:逻辑分析仪我也DIY(三)—PLL后复位问题

推荐阅读最新更新时间:2024-03-30 23:01

USB2.0虚拟逻辑分析仪的设计与实现

引言 传统的逻辑分析仪体积庞大、价格昂贵、通道数目有限,并且在数据采集、传输、存储、显示等方面存在诸多限制,在很大程度上影响了其在实际中的应用。选用高性能的FPGA芯片进行数据处理,充分利用PC的强大处理功能,配合LabView图形化语言开发的虚拟逻辑分析仪,其数据处理和传输速率大大提高,适用性极大增强,其显示、操作界面和低廉的成本较之传统的逻辑分析仪具有极大的优势和发展前景。 工作原理 本设计选用Altera公司的Cyclone系列FPGA器件EP1C3进行数据采集和处理,外接SRAM,用于数据的存储。系统通过高性能的PIC单片机PIC18F6620完成与PC的通信,接收PC发出的触发、配置信息并控制系统将

[测试测量]

SD卡中逻辑分析仪的应用

1.引言 SD卡以大容量,低功耗,小巧轻便,热插拔,价格便宜等特点,在如今的移动存储中占有重要的地位。 今天我们就以广州致远电子出品的 逻辑分析仪 系列产品LAB7504为例,介绍其在SD卡设计中的应用。 2.SD卡简介 SD卡共支持三种传输模式:SPI模式(独立序列输入和序列输出),1位SD模式(独立指令和数据通道,独有的传输格式),4位SD模式(支持四位宽的并行传输)。表1介绍了数据率与模式的关系。 SD模式的总线拓扑结构为: 一个主机(如微控制器)、多个从机(卡)和同步的星形拓扑结构。 所有卡共用时钟CLK、电源和地信号。而命令线(CMD)和数据线(DAT0~DAT3)则

[模拟电子]

逻辑分析仪的触发

逻辑分析仪主要是用于定位系统运行出错时的特定波形数据,通过观察该波形数据来推 断该系统出错的原因,从而有针对性地找出解决该错误的方案。 运用逻辑分析仪定位出错波形数据的方法主要有两种方式,一种是通过抓取运行过程中 大量的数据,然后在这些数据中通过其他方法来查找出错误点的位置,该方法费时费力,而且受制于逻辑分析仪存储容量,并不一定每次都可以捕捉到目标波形数据;另一种是通过触发的方式在特定波形数据到来时开始捕捉数据,从而精准地定位目标波形数据。 触发的概念最初出现在模拟示波器上,示波器在设置的特定波形的信号到来时停 止采集,并将波形绘制在屏幕上。逻辑分析仪用于分析数字系统时沿用了该概念。 数字系统在运行过程中,大多数情况下数据是

[测试测量]

逻辑分析仪应用于ADC及相关领域

TWLA500在ADC及相关领域的应用 FAE:现场技术支持。给客户提供你所销售产品应用上的技术支持,并对客户提出的质量问题进行处理。FAE与客户直接接触,在产品的应用和市场方向上有信息上的优势,很多时候FAE的表现决定了定单的成败。这个工作的重要性可见一斑。 在IC,通信等领域,新产品,新技术如雨后春笋般亮相在世人面前,如何让客户了解并掌握新技术和新产品的应用也就成了FAE的重要任务,一个完美的演示或许就能获得大批的定单,为自己带来巨大的经济效益。而FAE给客户演示必需的东西有一个就是演示板。 随着市场需求的增长,电子技术的发展,AD/DA的技术也得到了长足的进步。其应用范围也是越来越广泛,比比皆是,遍地开花。所以其品质

[测试测量]

逻辑分析仪测量数字电路的优势

示波器是专业测量模拟信号的,而测量分析数字信号, 逻辑分析仪 比示波器强大许多,主要有以下几个方面。 1、测量数字信号时,示波器通常可以用来观察有没有信号或者是信号的质量如何,逻辑分析仪主要用来分析信号高低电平时序时间,以及通信的是什么数据。 2、逻辑分析仪通道数通常比示波器多。示波器常见有单通道、双通道和四通道。而逻辑分析仪常见有8通道、16通道、32通道或者更多,测量多个信号运行状态,尤其是并行数据,通道最够多才能把所有的通道测量分析出来。 3、具有延迟能力,可以保存更长时间的数据。示波器是实时显示的,实际上他只能显示其中一小段数据,可以实现快速刷新,带来的缺点就是存储深度很低。而逻辑分析仪有较

[测试测量]

什么是逻辑分析仪?逻辑分析仪的参数、使用步骤和优势

由于电路的发展是从模拟发展到数字这样的过程,因此测量工具的发展也遵循了这个顺序。现在提到测量,首先我们想到的是示波器,尤其是一些老工程师,他们对示波器的认知度非常高。而逻辑分析仪是一种新型测量工具,是随着单片机技术发展而发展起来的,非常适合单片机这类数字系统的测量分析,而通信方面的分析中,比示波器要更加方便和强大。 一个待测信号使用10MHZ采样率的逻辑分析仪去采集的话,假如阈值电压是1.5V,那么在测量的时候,逻辑分析仪就会每100ns采集一个样点,并且超过1.5V认为是高电平(逻辑1),低于1.5V认为是低电平(逻辑0)。而后呢,逻辑分析仪会用描点法将波形连起来,工程师就可以在这个连续的波形中查看到逻辑分析仪还原的

[测试测量]

如何正确选择逻辑分析仪

逻辑分析仪是一种类似于示波器的波形测试设备,它是用于监测硬件电路工作时的逻辑电平,并加以存储,用图形的方式直观地表达出来,便于用户检测、分析电路设计(硬件设计和软件设计)中的错误。逻辑分析仪是设计特别是数字设计中不可缺少的设备,通过它,可以迅速地定位错误,解决问题,达到事半功倍的效果。 自1973年,第一台针对数字系统多个信号之间逻辑关系及时间关系测试的仪器—逻辑分析仪(Logic Analyzer)在数据域测试仪器中崭露头角以来,用户开始接受这种数据域测试仪器并作为终解决数字电路测试的手段。 近年来,逻辑分析仪的基本趋向在计算机与仪器的不断融合中寻求发展方向,依托不断进步的计算机技术,虚拟逻辑分析仪吸收融合了诸如逻辑笔、

[测试测量]

小广播

热门活动

换一批

更多

最新测试测量文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

- 【已结束】 电感应用知识分享|MPS 有奖直播

- 物联网、汽车、AI全覆盖——世平集团恩智浦解决方案大秀场

- 看视频赢京东卡 PI汽车专用解决方案学习中心正式上线

- 轻松注册世健eSHOP,百份奖品大派送!惊喜不断,好礼无限!ipad air2等你拿!

- 新用户限时福利:e络盟商城迎新季,全场包邮+打折~买一只电阻也包邮!

- 一大波MCU开发板正在靠近,速来——瑞萨电子设计大赛(2015)

- 【XILINX 主题分享月】 信号处理资料大搜集!!!

- 有奖直播|安森美高能效产品在 EV-Charger 市场的应用

- TE助力数据中心设计,缩短你与奥运的距离,猜猜它属于哪个“奥运场馆”赢大礼!

- 免费测评|ESP32-S2-Kaluga-1新型多媒体开发板,灵活拆装,满足多种需求

11月22日历史上的今天

厂商技术中心

电子电气工程师必知必会(第3版)

电子电气工程师必知必会(第3版) 实例解读51单片机完全学习与应用

实例解读51单片机完全学习与应用 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号