逻辑分析仪我也DIY(三)—PLL后复位问题

关于M4K的问题还没有结束。主要问题在于想利用M4K来存储要显示到VGA屏幕上的字模数据,而昨天为了方便开了一个很大位宽的M4K,结果就照成了M4K的利用率大大下降,原来不到8K的数据居然占用了7个M4K块,感觉不爽。所以今天绞尽脑汁是想出了解决办法,同时也为其他字符的显示方法开了绿灯。

具体方法不在此讨论,不过现在原来占用7个M4K的字模改成了32位宽*224,规规矩矩的占用了2个M4K块。此外把常用的8*16的ASCII字符字模数据都存到了M4K初始化ROM里了,这全都是体力活,耗费了不少精力。主要问题是字模软件和altera提供的标准ROM初始化文件的格式没法搞成一致。400多个字数据都是手工编号,小指头现在还隐隐作痛。不过显示的技术难点解决了,感觉还是蛮开心的。

其次,对于采样频率(采样周期)做了细化,不再是原来单一的只能为100MHz的采样率,现在可以有10档可调的采样频率。因为采样率设置后的显示还没有继续搞定,所以暂时不做进一步的测试。

因为这个工程里的两个时钟都是用的PLL产生的,所以有必要探讨一下使用了PLL输出时钟作为系统工作时钟时的复位逻辑设计。特权同学的一点愚见,愿抛砖引玉,期待高手指点。

以前的很多博文里都谈过异步复位、同步释放等等的问题,那么在系统复位后PLL时钟输出前,即系统工作时钟不确定的情况下,怎么考虑这个复位的问题呢?

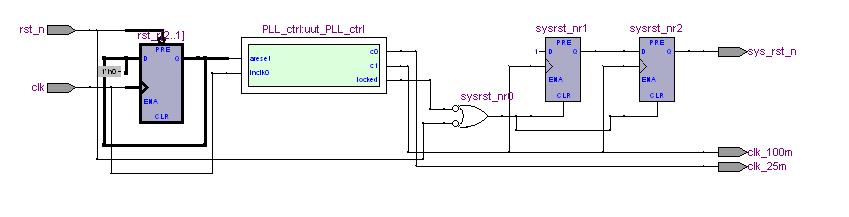

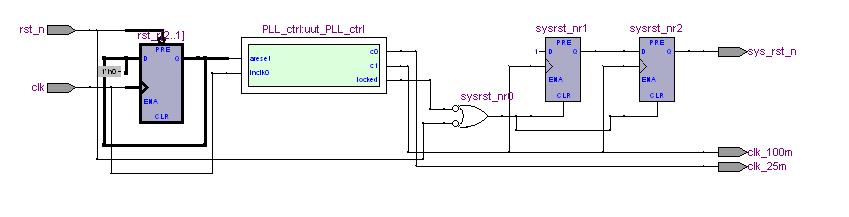

上图是特权同学的这个工程里的复位设计,先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n异步复位、同步释放处理一下,然后这个复位信号输入PLL,同时clk也输入PLL。我的设计初衷是在PLL输出时钟有效前,系统的其它部分都保持复位状态。PLL的输出locked信号在PLL有效输出之前一直是低电平,PLL输出稳定有效之后才会拉高该信号。所以这里就把前面提到的FPGA外部输入复位信号rst_n和这个locked信号相与作为整个系统的复位信号,当然了,这个复位信号也是需要让合适的PLL输出时钟异步复位、同步释放处理一下。

关键字:逻辑分析仪 PLL 复位问题

引用地址:逻辑分析仪我也DIY(三)—PLL后复位问题

关于M4K的问题还没有结束。主要问题在于想利用M4K来存储要显示到VGA屏幕上的字模数据,而昨天为了方便开了一个很大位宽的M4K,结果就照成了M4K的利用率大大下降,原来不到8K的数据居然占用了7个M4K块,感觉不爽。所以今天绞尽脑汁是想出了解决办法,同时也为其他字符的显示方法开了绿灯。

具体方法不在此讨论,不过现在原来占用7个M4K的字模改成了32位宽*224,规规矩矩的占用了2个M4K块。此外把常用的8*16的ASCII字符字模数据都存到了M4K初始化ROM里了,这全都是体力活,耗费了不少精力。主要问题是字模软件和altera提供的标准ROM初始化文件的格式没法搞成一致。400多个字数据都是手工编号,小指头现在还隐隐作痛。不过显示的技术难点解决了,感觉还是蛮开心的。

其次,对于采样频率(采样周期)做了细化,不再是原来单一的只能为100MHz的采样率,现在可以有10档可调的采样频率。因为采样率设置后的显示还没有继续搞定,所以暂时不做进一步的测试。

因为这个工程里的两个时钟都是用的PLL产生的,所以有必要探讨一下使用了PLL输出时钟作为系统工作时钟时的复位逻辑设计。特权同学的一点愚见,愿抛砖引玉,期待高手指点。

以前的很多博文里都谈过异步复位、同步释放等等的问题,那么在系统复位后PLL时钟输出前,即系统工作时钟不确定的情况下,怎么考虑这个复位的问题呢?

上图是特权同学的这个工程里的复位设计,先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n异步复位、同步释放处理一下,然后这个复位信号输入PLL,同时clk也输入PLL。我的设计初衷是在PLL输出时钟有效前,系统的其它部分都保持复位状态。PLL的输出locked信号在PLL有效输出之前一直是低电平,PLL输出稳定有效之后才会拉高该信号。所以这里就把前面提到的FPGA外部输入复位信号rst_n和这个locked信号相与作为整个系统的复位信号,当然了,这个复位信号也是需要让合适的PLL输出时钟异步复位、同步释放处理一下。

上一篇:逻辑分析仪我也DIY(四)—神秘蓝点

下一篇:逻辑分析仪我也DIY(二)

推荐阅读最新更新时间:2024-03-30 23:01

PLL陷波滤波器可以用于阻拦不需要的频率

经常有要阻挡某些频率信号的情况,其中最常见的是50Hz或60Hz的电力线工频。图1中的PLL陷波滤波器可以用于阻拦不需要的频率。IC1 LM567C是一只音调解码器。C1、R1A和R1B等元件决定了IC1探测的频率F:F=1/ 。当把频率F加到IC1的Pin 3时,输出端Pin 8变为低,因为IC1中的输出晶体管饱和。 图1 一只音调解码器和一只开关可阻拦不需要的频率 LM567C解码器包含一个同相和正交探测器,由一只VCO(压控振荡器)驱动。VCO决定了解码器的中心频率。解码器的带宽为1070√V/(C2F),其中V是rms(均方根)的输入电压,C2是微法级的电容。带宽是频率的一个百分比。 音

[模拟电子]

使用逻辑分析仪快速发现数字系统的问题

目前,数字设计正在发生翻天覆地的发展和变化,亟需采用创新的方法来进行设计、仿真、测量和调试。一方面的变化是更多地采用串行总线,另一方面的变化是使用系统级芯片(SoC)集成电路或具有SoC功能的先进FPGA。虽然数字设计面临着这些变化,不过传统的并行总线仍然有很大的用武之地,设计人员需要对这些总线进行测量。本文将讨论并行总线测量的基础知识,包括功能与计时验证和调试,以及如何跟踪系统崩溃情况并探究其根本原因。 逻辑分析仪中的同步和异步捕获比较 在讨论具体的测量实例之前,我们首先来探讨一下同步和异步捕获的差别,以及各自的优点和局限性。 同步(状态模式)捕获是指当出现一个相关的有效时钟信号时,例如在系统时钟线路上出现上升沿,逻辑

[测试测量]

单片机欠压复位问题的解决

欠压复位(以下称为BOR)是单片机可靠性的一项重要功能,通常用于解决电源问题,下面将介绍欠压复位的另一个问题。 单片机的“电量不足”是电源电压不足或暂时降低,低于可靠运行所需的水平。许多单片机具有保护电路,该电路可检测电源电压何时低于此水平,并将设备置于复位状态,以确保在电源恢复时正确启动。此操作也称为“欠压复位”,英文缩写为“BOR”。类似的功能称为低电压检测(LVD),它更复杂,增加了对多个电压电平的检测,可以在触发复位之前产生中断。 BOR通常由控制寄存器中的某个位使能。通常,当BOR引起复位时,状态位会置1。该状态位在复位后仍然有效,并允许程序检测到问题并执行其他恢复或记录事件。 如果BOR被禁用会怎样

[单片机]

信号完整性分析基础系列之二十二—— 自定义二阶PLL

概述 本文介绍了自定义二阶PLL,说明了它如何正确应用于串行数据测量中以提高眼图和抖动测量精度。 抖动定义的是边沿的时序不确定性。为了确定串行数据信号边沿的时序不确定性,边沿需要和一个参考的时钟边沿进行比较。 对于大多数高速串行数据标准,参考时钟是内嵌在串行数据信号里的,在测试时需要从被测信号中恢复该时钟。恢复时钟的方法将直接影响到测量眼图的形状和抖动值大小。 当前一些串行数据标准不仅定义了测量抖动的标准方法,而且也定义了时钟恢复的标准方法。 低频信号边沿的变化可以通过PLL来进行跟踪,最终并没有反应在测量出的抖动上,因为它们被PLL有效地去除掉了。反之,那些没有被PLL去除的低频信号边沿变化就会被测量为抖动。因此,时钟恢复方

[测试测量]

STM32意外复位问题调试

最近在使用STM32座项目时遇到一个奇怪的问题。系统一开始运行很正常但是在长时间运行之后会随机的出现STM2单片机无故产生复位的问题。因为在调试的过程中收获颇多,所以打算记录一下这一次的调试过程。 首先做问题分析,既然单片机在运行一段时间之后会产生复位。那具体是什么原因引起的单片机复位呢?拍脑子一想会不会是没有及时喂狗导致看门狗溢出引起的复位。为了证明这一点我们查询了stm32的数据手册有关于复位源的介绍 由上面的描述我们可以知道在RCC_CSR中记录了单片机复位的类型。因此我们只要在单片机启动时去读取该寄存器中的对应状态位即可判断出单片机上一次是因为何种原因产生复位的。注意:RCC_CSR寄存器是需要软件清除的。如

[单片机]

逻辑分析仪的功能

逻辑分析仪的功能 逻辑分析仪是分析数字逻辑关系的一种分析仪器,将被测信号通过比较器进行判定,高于参考电压者为High,低于参考电压者为Low,在High与 Low之间形成数字波形。逻辑分析仪具体的用途是什么呢?下面小编就来具体介绍一下逻辑分析仪的功能,希望可以帮助到大家。 逻辑分析仪的功能 定时分析 定时分析仪是逻辑分析仪中类似示波器的部分,它与示波器显示信息的方式相同,水平轴代表时间,垂直轴代表电压幅度。定时分析仪首先对输入波形的采样,然后使用用户定义的电压阈值,确定信号的高低电平。定时分析仪只能确定波形是高还是低,不存在中间电平。所以定时分析仪就像一台只有 1 位垂直分辨率的数字示波器。但是,定时分析仪并不能用于测试参量,

[测试测量]

PLL电路设计原理及制作

在通信机等所使用的振荡电路,其所要求的频率范围要广,且频率的稳定度要高。 无论多好的LC振荡电路,其频率的稳定度,都无法与晶体振荡电路比较。但是,晶体振荡器除了可以使用数字电路分频以外,其频率几乎无法改变。 如果采用PLL(相位锁栓回路,PhaseLockedLoop)技术,除了可以得到较广的振荡频率范围以外,其频率的稳定度也很高。此一技术常使用于收音机,电视机的调谐电路上,以及CD唱盘上的电路。 一 PLL电路的基本构成 PLL电路的概要 图1所示的为PLL电路的基本方块图。此所使用的基准信号为稳定度很高的晶体振荡电路信号。 此一电路的中心为相位此较器。相位比较器可以将基准信号与VCO (Voltage Contro

[模拟电子]

逻辑分析仪的分类有哪些

逻辑分析仪 是利用时钟从测试设备上采集和显示数字信号的仪器,最主要作用在于时序判定。由于 逻辑分析仪 不像示波器那样有许多电压等级,通常只显示两个电压(逻辑1和0),因此设定了参考电压后, 逻辑分析仪 将被测信号通过比较器进行判定,高于参考电压者为High,低于参考电压者为Low,在High与 Low之间形成数字波形。 逻辑分析仪 分为两大类:逻辑状态分析仪(Logic State Analyzer,简称LSA)和逻辑定时分析仪(Logic Timing Analyzer)。这两类分析仪的基本结构是相似的,主要区别表现在显示方式和定时方式上。 逻辑状态分析仪用字符0、1或助记符显示被检测的逻辑状态,显示直观,可以从大量数码中迅

[测试测量]

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著)

高频电路设计与制作 (市川裕一,青木胜,卓圣鹏 著) 锁相环PLL原理与应用.pp

锁相环PLL原理与应用.pp 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号