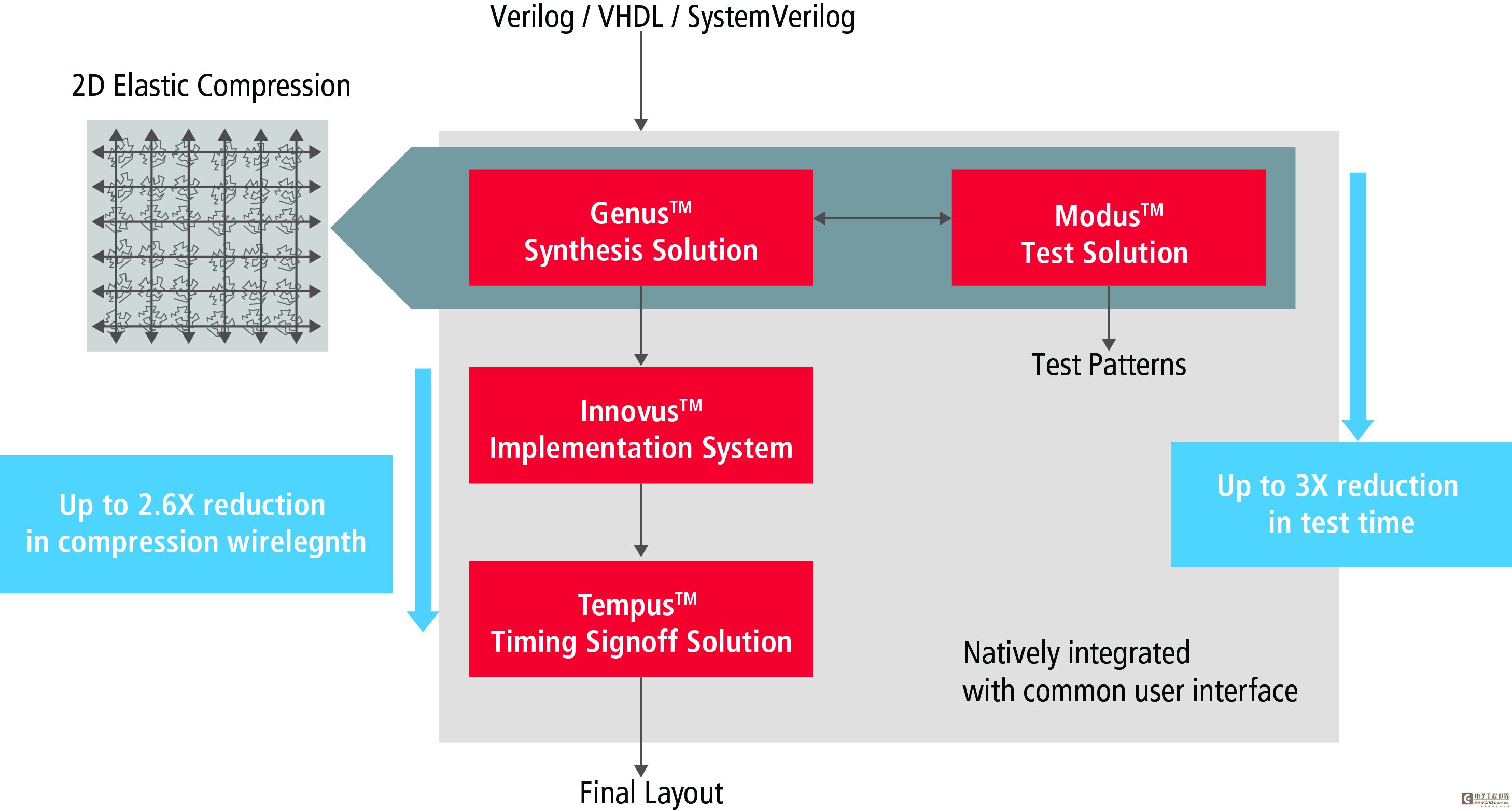

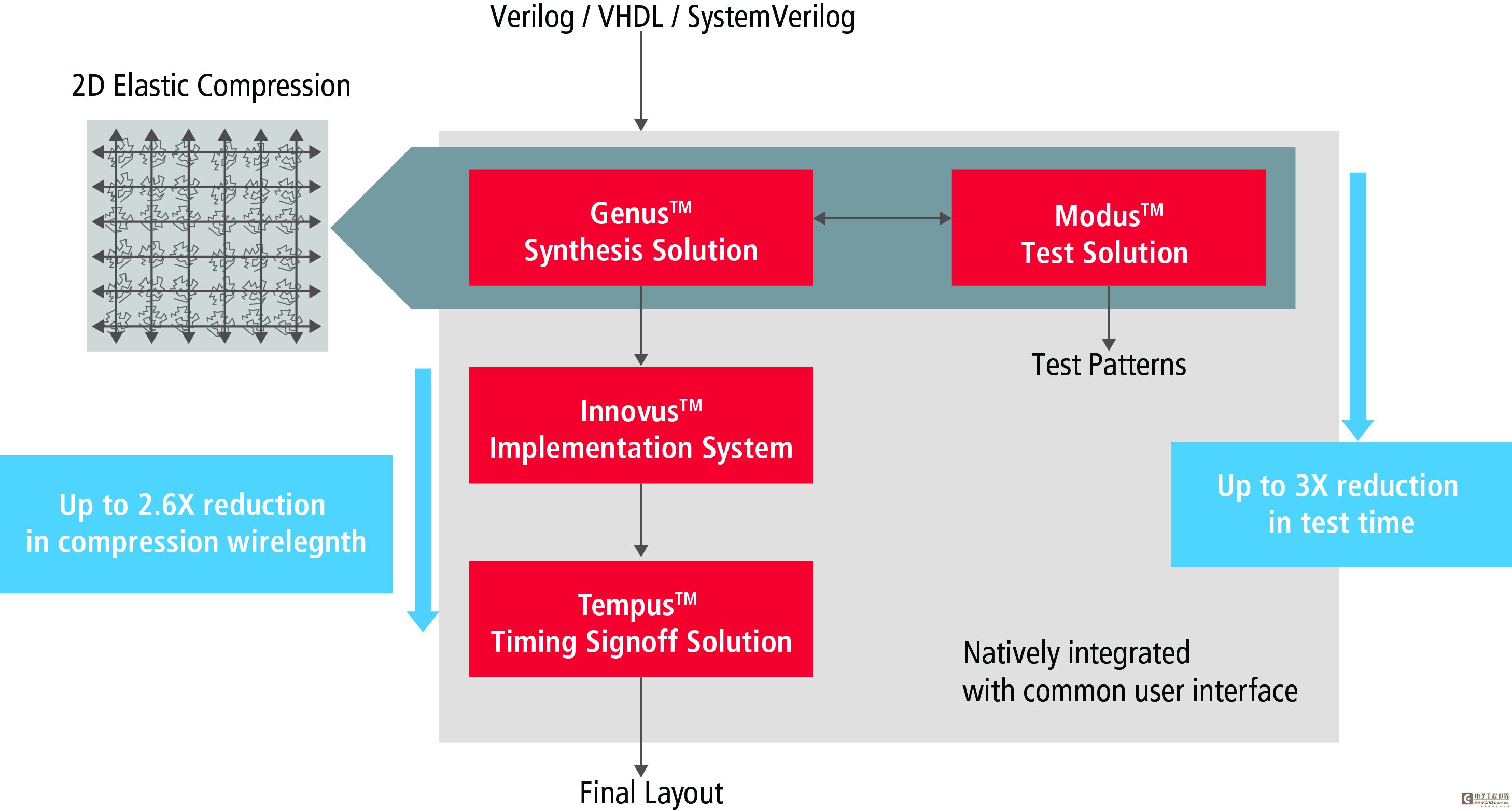

日前,Cadence Design System, Inc.(现已正式更名为楷登电子)宣布推出全新Modus™测试解决方案。该方案助设计工程师将产品测试时间缩短最高三倍,从而降低生产测试成本,进一步提高硅产品利润率。新一代测试解决方案采用物理感知2D弹性压缩架构,在不影响设计尺寸及布线的前提下使压缩比高达400余倍。目前,此项技术专利正在申请中。

关键字:Cadence Modus测试解决方案

引用地址:Cadence Design System, Inc.宣布推出全新Modus™测试解决方案

针对测试设计过程中的挑战,Cadence® Modus测试解决方案采用以下创新功能:

2D压缩:扫描压缩逻辑可在晶片平面布局上构成二维物理感知网格,从而提高压缩比并缩短线长。在压缩比为100倍的情况下,2D压缩线长最高可比业内现行扫描压缩架构缩短2.6倍。

弹性压缩:在自动测试模式生成(ATPG)期间,通过嵌入在解压逻辑中的寄存器,按序控制多个扫描周期的关注数据位,确保压缩比提高至400倍以上时,仍可保持满意的故障覆盖率。

嵌入式存储器总线支撑:插入共享测试访问总线,同一IP核中的多个嵌入式存储器可全速执行可编程存储器内建自测试(PMBIST)。该功能还包括针对鳍式场效应晶体静态随机存储器(FinFET SRAM)和汽车安全应用的全新可编程软件测试算法。

强大的通用脚本和集成调试环境:可测性设计(DFT)逻辑插入及ATPG功能采用全新、且标准统一的TCL脚本语言和调试环境,兼容Cadence Genus™ 综合解决方案、Innovus™ 设计实现系统及Tempus™ 时序签核解决方案。

“Cadence新一代Modus测试解决方案采用全新的创新功能,可以从根本上改变设计和测试工程师解决测试问题的方式。目前,我们正在为这项技术申请专利。”Cadence数字和签核事业部高级副总裁兼总经理Anirudh Devgan博士表示:“Modus测试解决方案通过搭建物理感知的2D网格架构,并按序压缩测试模式(pattern),较传统方法显著缩短了测试时间,为Cadence客户带来又一重要的盈利优势。”

上一篇:雷泰有你 感恩回馈

下一篇:报警器红外探测器结构及特征是怎样的

推荐阅读最新更新时间:2024-03-30 23:11

Cadence: 中国IC设计发展出现良机

在经历了去年广受瞩目的收购风波之后,很长一段时间人们都对Cadence的前途感到忧心忡忡。而在Michael Fister黯然离职后,这种担心被进一步的放大了。不过,目前看来这种担心似乎是多虑了——Cadence亚太区总裁兼全球副总裁居龙不久前表示,其所属的这家公司目前财务状况良好。在岁末年初之时,他用一个“变”字来概括Cadence在2008年的表现。并表示新年Cadence的主题将是“回归本始(Back to Basics)”——作为一家高技术公司,Cadence将加大在技术与研发上的投入。此外,他还强调,中国IC设计公司正在面临一个“千载难逢”的发展机会。 2008革新求变,结构调整财务稳健 2008年的经济

[半导体设计/制造]

Cadence与三星加速开发3纳米混合信号设计

楷登电子(美国 Cadence 公司,NASDAQ:CDNS)今日宣布,与 Samsung Foundry 合作开发已经验证的 Mixed-Signal OpenAccess 工艺设计开发包(PDK)技术文件,支持从 28FDS 到基于 GAA 的 3 纳米工艺等三星制程技术。 Mixed-Signal OpenAccess PDK 可以确保 Cadence® 的定制化工具和数字设计工具在三星工艺技术环境下无缝运行,帮助双方共同客户缩短产品上市时间。Mixed-Signal OpenAccess PDK 将提高数据中心、网络、5G、移动、工业及汽车应用混合信号设计的生产效率。 与面向三星工艺技术的 Mixed-Signal Ope

[手机便携]

富士通采用Cadence Encounter Timing System进行Signoff时序分析

Cadence Encounter Timing System 可进行 90 纳米及以下设计 sign-off 验证 加州 圣荷塞, 2006 年 9 月 19 日 ——Cadence 设计系统公司( NASDAQ : CDNS )近日宣布,富士通有限公司已经采用 Cadence Encounter Timing System ( ETS )进行其设计实现流程的时序分析。 ETS 为 90 纳米及 90 纳米以下的设计提供了卓越的 sign-off 时序精确性、可用性以及功能性。 Encounter Timing Sy

[焦点新闻]

Cadence携手ARM提供多核与低功耗器件的参考方法学

美国加州圣荷塞及英国剑桥2007年12月5日 ——Cadence与ARM 今天宣布推出两种由它们联合开发的新的实现参考方法学,一种用于ARM11(TM) MPCore(TM)多核处理器,另一种用于ARM1176JZF-S(TM)处理器的低功耗实现,后者集成了ARM Intelligent Energy Manager (IEM(TM))技术。 基于ARM1176JZF-S处理器的低功耗参考方法学提供了支持IEM技术所需的增强特性,并支持IEM技术采用的动态电压(Dynamic Voltage)和频率调节(Frequency Scaling (DVFS)硬件方法。IEM技术已被证明可减少超过60%的CPU能耗。 这些参考方法学包容

[新品]

期待大陆IC设计提速-Cadence亚太区总裁

“我觉得现在IC设计产业台湾领先大陆约十年!” 日前Cadence副总裁兼亚太区总裁居龙面对电子工程世界网记者如是说。而仅仅在两年前(2005年),居龙在跟台湾记者聊天时称台湾相对于大陆还有五年的优势。一方面,中国IC设计产业高速增长,另一方面,企业核心竞争力,面对这种强烈的反差,我们不禁会问:问题究竟出在什么地方? 据悉,国内目前约有400家IC设计企业,相对于国外先进企业依然显得水平低和规模小,国内最大IC设计企业与全球最大IC设计公司年销售额之比是十几亿元人民币和300多亿元人民币的差距(截至2006年年末)。2006年国内整个设计产业收入约为20亿美金,其中一半为传统的智能卡、身份证卡等低技术含量产品,而对于中高

[焦点新闻]

Cadence讲出EDA的未来形态:无人设计芯片

集微网消息(文/春夏)“2020年中国半导体市场人才需要70万人,而现有中国半导体市场从业人员仅30万人。对于人才缺口,其实很难填补,因为中国每年新从业毕业生也就3万人。IC人才缺乏不止存在于中国,美国也存在,随着人口老龄化,这一问题更加严峻。通过培养并不能弥补人才的缺口。”在11月29日举行的中国集成电路设计业2018年会暨珠海集成电路产业创新发展高峰论坛上,Cadence公司全球副总裁石丰瑜先生如是说。 石丰瑜先生指出,电子设计工程师的工作最难填补。在这样的背景下,EDA软件也要从自动化演变为智能化就显得尤为重要。 近年来,美国DARPA提出电子复兴计划,寻求建立更加健康、安全和高度自主化的电子工业基础,以实现从通用硬

[手机便携]

四大EDA高层为本土IC设计把脉施良方

Cadence、Synopsys(新思)和Mentor Graphics三大厂商占了全球EDA行业70%的市场份额。然而,三大厂商背后是上百家各有特色的EDA公司。其中不乏佼佼者,比如SpringSoft(思源)在波形显示、查错及某些全定制板图设计应用上有一定的主导地位。因此,如果IC设计公司希望能建立先进而有竞争力的设计验证流程,采用多家工具是不可避免的。《电子工程专辑》记者在“2009年IC设计调查”期间采访了四大EDA厂商的高层,以为本土IC设计发展献策。 Cadence中国区总经理 刘国军:本土IC设计面临全球化挑战 随着经济衰退蔓延到全世界,消费者在消费电子上的花费可能会降低。与此同时,这样的市场环境对

[半导体设计/制造]

威盛获授权使用Cadence Tensilica HiFi音频/语音DSP

Cadence设计系统公司(NASDAQ:CDNS),全球电子设计创新领先公司今日宣布台湾威盛科技(VIA Technologies)已选择Cadence® Tensilica® HiFi Audio/Voice DSP(高保真音频/语音数字信号处理器)用于机顶盒、平板电脑和移动设备的系统芯片(SOC)设计。 “我们需要的是非常低功耗的音频DSP(数字信号处理器),同时也要有丰富的编解码软件包支持,所以我们选择了Cadence Tensilica HiFi/Voice Audio DSP,”威盛科技工程副总栽Michael Shiuan表示。“这种低功率的DSP很适合我们先进的SOC架构和产品线。正是由于有了完整的稳定的编

[嵌入式]

芯片设计——CMOS模拟集成电路设计与仿真实例:基于Cadence IC 617

芯片设计——CMOS模拟集成电路设计与仿真实例:基于Cadence IC 617 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号