在上一篇文章中我们介绍了直方图的概念以及如何使用直方图的方法来分析抖动(也即从统计域的角度来分析)。从抖动的直方图中我们可以看出抖动的分布特征(随机分布、双峰分布等),通过测试直方图的标准偏差、双峰之间的间距也可以估计出抖动中包含的随机抖动和固有抖动大小。但是对于周期性抖动成份却很难在直方图中观察到或者计算出来。周期性抖动一般是由于串扰等引起的,在数据抖动分类中,周期性抖动属于固有抖动的一部分。为了进一步从总体抖动中分解出周期性抖动成份,我们需要使用时域的抖动追踪功能(Jitter Track,该功能是Lecroy公司在1997年首次发明的)。

抖动追踪功能,即通过对某一测量参数(TIE抖动、周期抖动、周期间抖动、幅度测量参数)的变化情况的实时追踪来分析该参数的变化趋势,继而分析引起参数变化的原因,给电路调试提供指导。

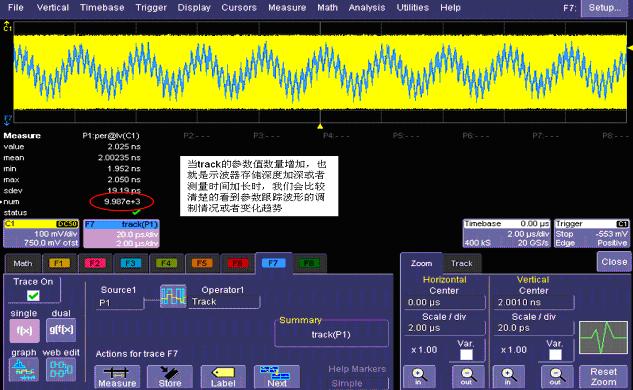

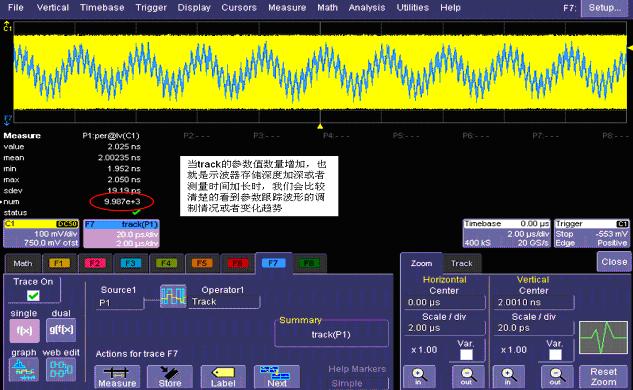

下图1为对一个时钟信号周期测量参数的跟踪示例:图1的上半部分为示波器C1通道采集到的时钟波形;下半部分为对C1通道中的时钟波形的周期测量参数的track波形,X轴为时间,Y轴为周期测量参数值,需要注意下的是每一个测量参数值(对应于Y轴上的)对应在X轴上的时间值设定为时钟的两个上升沿之间的时间差。

图1 什么是抖动追踪

抖动追踪波形不仅可以体现出参数变化的趋势,更为强大的是在Lecroy示波器上完全可以非常自如的对抖动追踪波形进行保存、测量、分析以及用于函数运算等。如下图2为用光标非常方便清晰的在周期测量抖动追踪波形上测量出某一时段的时钟周期值。

图2 用光标在时钟周期测量参数波形上测量时钟周期值

当采集波形数据的时间足够长时或者采集存储深度足够深时,我们会看到时钟信号的周期测量参数的跟踪波形呈现出明显的周期性变化趋势(有明显的正弦调制),且应该有一高频的正弦干扰和一低频的正弦干扰,如下图3所示,这说明该时钟信号受到了具备正弦特征的信号的干扰。

图3 当采集波形的memory加深后的周期参数跟踪波形

那么这个正弦干扰的频率是多高呢?(如果知道了该干扰的频率,我们调试的时候就会更加有针对性的找到干扰源所在位置!)Lecroy示波器给我们带来的另外一个惊喜是它能够对抖动追踪后的波形进行FFT分析,从而轻松的找到干扰源的频率,如下图4所示:

图4 对周期测量参数进行FFT分析

实例:通过抖动追踪、抖动追踪波形的FFT运算来分析由于电源不稳定引起的抖动参数变化,如下图5所示:

图5 由于电源供给噪声引起的时钟抖动

(通道2为时钟波形,通道3为电源电压波形,函数B为抖动追踪波形,可以清楚的看到抖动参数受到了电源供给波动的影响)

可见,使用示波器的Jitter Track以及FFT的功能,可以帮助我们分析周期性抖动的来源及其数量,如下图6所示为一DVI信号的TIE抖动track波形的频谱及其抖动数值:

图6 某一DVI信号的TIE抖动测量参数track波形的的频谱分析

关键字:信号完整性 抖动追踪 JitterTrack 抖动分析

引用地址:

信号完整性分析基础之七——JitterTrack在抖动分析中的应用

推荐阅读最新更新时间:2024-03-30 23:31

10G信号抖动测量的检定分析

由于不断追求更高性能,有效数据窗的单位间隔(UI)继续缩短。速率为1Gbps时,UI为1000 ps;5Gbps缩短为200ps;10Gbps则为100ps。对于100ps的有效数据窗,在系统没有连贯而可靠地发送和接收数据之前,只能容忍很小的Tj (总抖动)。以上述速度传输时,Tj结果需远小于100ps,而Rj (随机抖动)更是以飞秒(fs)为单位。有什么技术和工具能用来检定这些飞秒系统呢? 基本上,随着速度的提升,高速I/O设计遭遇到较以往更大的挑战。很多最新标准要求物理层的比特误码率为10–12。然而,随着UI逐渐缩小,要想保持这个数量级的误码率也越来越难。最终,这就意味着设备级抖动要继续缩短。例如,5Gbps的Su

[测试测量]

高速DSP数据采集的信号完整性问题

摘要:深入研究高速数字电路设计中的信号完整性问题;分析电路中破坏信号完整性的原因;结合一个实际的DSP数据采集系统、阐述实现信号完整性的具体方案。

关键词:信号完整性 ADSP21161 数据采集 噪声控制

引言

当前,日渐精细的半导体工艺使得晶体管尺寸越来越小,因而器件的信号跳变也就越来越快,高速数字系统的快斜率瞬变和极高的工作频率,以及很大的电路密集度,导致高速数字电路系统设计领域的信号完整性问题以及电磁兼容性问题日趋严重。破坏了信号完整性将直接导致信号失真、定时错误,以及产生不正确数据、地址和控制信号,从而千万系统误工作甚至导致系统崩溃。因此,信号完整性问题已经越来越引起高速数字电路设计人员的关注。

1 信号完整性问

[嵌入式]

时间抖动(jitter)的概念及其分析方法

随着通信系统中的时钟速率迈入GHz级,抖动这个在模拟设计中十分关键的因素,也开始在数字设计领域中日益得到人们的重视。在高速系统中,时钟或振荡器波形的时序误差会限制一个数字I/O接口的最大速率。不仅如此,它还会导致通信链路的误码率增大,甚至限制A/D转换器的动态范围。有资料表明在3GHz以上的系统中,时间抖动(jitter)会导致码间干扰(ISI),造成传输误码率上升。 在此趋势下,高速数字设备的设计师们也开始更多地关注时序因素。本文向数字设计师们介绍了抖动的基本概念,分析了它对系统性能的影响,并给出了能够将相位抖动降至最低的常用电路技术。 本文介绍了时间抖动(jitter)的概念及其分析方法。 在数字通信系统,特别是同步系

[模拟电子]

平衡电子设备静电防护和信号完整性设计

导言: 如今,电子装置有三大发展趋势:采用较小的几何尺寸,减少片上防护和适应不断变化的应用环境,这也导致静电(ESD)防护有了显著地变化。在确保可靠的ESD防护条件下,保证高信号完整性的复杂度增加,这就迫使设计者在ESD防护和所期望的信号完整性之间进行平衡。 现今,专业集成电路(ASICs)的制造工艺使几何尺寸已经减少到90nm或更小,因此引发ESD相关故障的电压或电流值也已减小。简单地说,那些更小的装置将会受到更小的电平电压或电流的损害。而减少片上ESD防护是增加ESD损害的一个因素,这种困境已被ESD目标规范产业委员会广泛地宣传。 确定哪种ESD防护装置能提供最好的防护不是一件容易的事情。今天已有各种ESD防护装置

[模拟电子]

高速电路设计和信号完整性分析

随着技术的进步,目前高速集成电路的信号切拘时间已经达到几百ps,时钟频率也可达到几百MHz如此高的边沿速率导致印刷电路板上的大量互连线产生低速电路中所没有的传输线效应,使信号产生失真,严重影响信号的正确传输。若在电路板设计时不考虑其影响,逻辑功能正确的电路在调试时往往会无法正常工作。为了解决这个问题,在设计高速电路时必须进行信号完整性分析,采用虚拟样板对系统进行透彻仿真,精确分析电路的布局布线对信号完整性的影响,并以此来指导电路的设计。这样,以往很多在调试时才能发现的问题,在设计期间就可以解决,极大地提高了设计成功率,缩短了设计周期。 要对信号进行完整性分析,首先要建立精确的器件模型。以前在电路仿真时普遍采用SPICE

[模拟电子]

智能仪器设计基础 (王祁)

智能仪器设计基础 (王祁) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号