2016年12月,由台湾厂商宏碁、联发科、研华和七大产业联盟共同发起正式宣布成立「亚洲.硅谷物联网产业大联盟」,亚洲硅谷首要的工作就是要推动物联网和创新创业两大主轴。台湾半导体协会理事长卢超群表示『半导体如果只留在IC设计,那绝对会是错的,得往前推进』。正如一些研究报告预测,物联网将大量的应用在未来的M2M,支付系统,运输,产品制造,库存管理,机械监控,装运,牲畜,节能,智能城市,智能建筑,智能能源,智能工业,智能金融和智能健康,因此,我们应该注意新的需求,学会掌握硬件可以发展的智能服务。

过去几十年里,内存发展领域衍生出两个不同的产品线:高速率和低功耗。每个产品线都有着各自特有的功能、应用和价格。然而,对采用可携式电源供电并用以执行复杂操作的高性能低功耗设备的需求正在不断增加。这种需求背后的动力来自新一代医疗设备、手持设备、消费类电子产品、通信系统以及工业控制器,而这些设备正是受物联网(IoT)所驱动。而由于晶体管容量增大,加上位单元不断缩小,内存的面积更容易受工艺变化所造成的瑕疵影响,这种瑕疵就会降低处理器芯片的总产量。因此,要成为IoT设计的优先选择,则内存的发展必须能够让客户不必在性能和功耗之间做取舍。

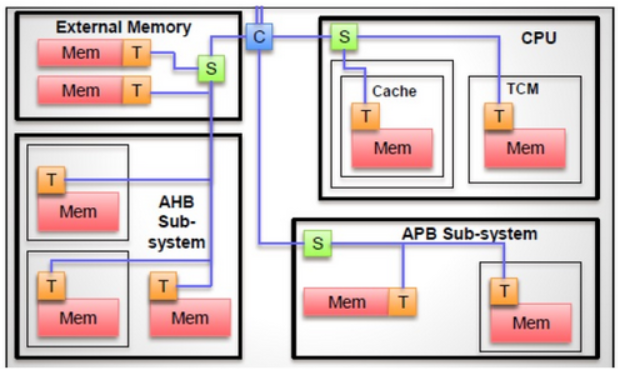

随着制程的先进以及IC设计愈来愈复杂,内存(RAM、ROM、Embedded Flash、DRAM、Embedded DRAM)在IC产品中的比重已超过百分之五十,存在的缺陷类型(Fault type)愈来愈多、对产品良率的影响也愈来愈大。基于成本以及效能考虑,内建自我测试技术(BIST; Built-In Self Test)便因此产生。传统的做法是针对单一嵌入式内存开发嵌入式测试电路,而现今大部分BIST自动化的EDA工具则局部进化为先人工做小群分块,再针对小群嵌入测试电路以节省电路面积(如图一)

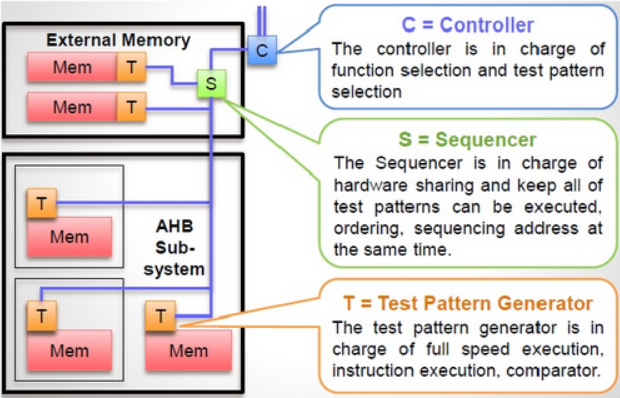

因此厚翼科技特别开发「整合性内存自我测试电路产生环境Brains」,以解决传统设计之不足(如图二图三)。

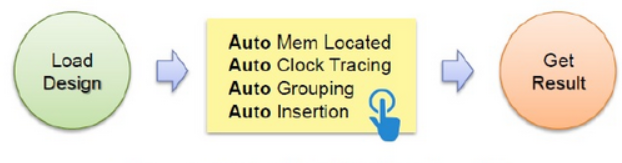

厚翼科技的内存测试整合性开发环境Brains具有快速导入、检测率高、面积小、测试时间短的优势,Brains是从整体的芯片设计切入,利用硬件架构共享的观念,可以大幅减少测试电路的门数(gate count)。Brains拥有自动化的Mem Located、Clock Tracing、Grouping 与Insertion,只要简单步骤即可完成最复杂的BIST规划(如图四所示)。另外,Brains可以自动判读内存并将其分群、同时支持数个时钟源的内存应用、根据内存的特性选择最适合且有效率的测试算法,大大提高内存测试的良率。Brains的五级到七级的弹性化管线式架构满足高速内存测试的需求。

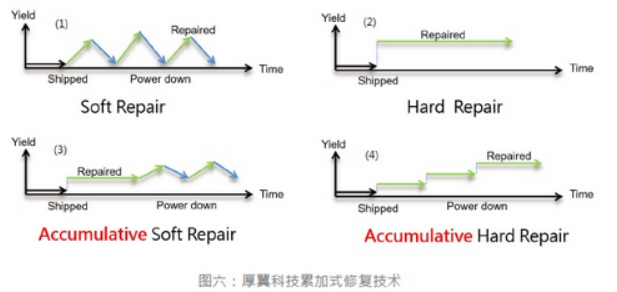

此外,厚翼科技的内存修复解决方案HEART(HEART; High Efficient Accumulative Repair Technical)即是基于Brains的检测结果,针对有缺陷的内存加以修复。透过修复的技术,可确保芯片功能的正确性,避免因内存模块错误而导致的错误动作。

HEART采用累加式修复技术,整合了传统软式修复和硬式修复的优点。透过内部储存单元和外部储存单元两者搭配使用,当芯片因长时间使用而出现新错误时,HEART解决方案可针对新出现的错误点,再加以修复。其中,更可由使用者决定写入外部储存单元的时间点,以延长芯片的使用时间及提升可靠度。当芯片启动时,从外部储存单元读取相关修复配置文件并加以修复。透过累加式的检测,来确认芯片有无新错误发生。若有新错误发生,则会记录该错误点,以便尔后可刻录至外部储存单元,藉此进行累加式修复,如图五。

(1)一次性软式修复:开机时间长,省下eFuse费用

(2)一次性硬式修复:需额外eFuse费用,但能配合更严谨的测试条件,提供修复率

(3)累加式软式修复:延伸一次性硬式修复信息,并于每次开机时又做动态修复测试

(4)累加式硬式修复:针对错误内存进行备援内存的多次性有效配置,且将配置信息

储存并重复性刻录。

那么在物联网应用中,要如何创造出『万物联网』的价值呢?首先就是要让开发物联网的硬件的价格能够低廉到让许多『创客(Maker)』可以接受,让有兴趣开发物联网智慧服务的『创客』,可以轻易拿到相关的硬设备。所以,如何降低物联网相关芯片的价格,成为物联网商务模式一个值得探讨的课题。物联网芯片的硬件架构都需要嵌入式闪存(EFlash; Embedded Flash)来储存程序(Program)。所以EFlash的测试费用也会决定物联网芯片的开发成本,在这微利时代且锱铢必较的物联网开发平台上,成本将是关键!

厚翼科技基于特有的内存测试专利开发出嵌入式闪存的测试解决方案(EFlash BIST)。

EFlash BIST将传统的BIST架构做了很大的变革,EFlash BIST充分利用硬件架构分享 (Hardware Sharing) 的设计来达到优化的面积和测试时间。EFlash BIST是一个客制化的IP,厚翼科技的研发团队,针对客户所用的EFlash与所需要的测试项目开发出专属的EFlash BIST IP。此客制化的EFlash BIST IP将可以大幅度的缩短EFlash的测试时间。

传统的EFlash测试方案可以直接使用自动化测试机台(Automation Test Equipment; ATE)或是使用EFlash的供货商提供的BIST。采用ATE做EFlash的测试,由于测试时间过长,导致测试费用太高,相当不符合物联网开发平台对于费用的要求。然而,采用EFlash供货商提供的BIST方案,对于使用者而言,非常难以在短时间内将BIST电路与EFlash做整合(图七),导致整个物联网芯片的开发时间过长。

基于以上两点使用上的不便之处,厚翼科技将传统的EFlash BIST的实现流程简化如下(图八)。

厚翼科技的EFlash BIST IP可根据客户在测试项目上的需求提供各项测试方案如CP1、CP2、CP4、FT等测试项目。此外,厚翼科技的EFlash BIST IP仅需要非常少的测试针脚(Pin),并且厚翼科技的EFlash BIST IP可以提供下列可程序化(Programmable)的功能包括Change ATE Setting、Algorithm、Program Time、Erase Time、Address Sequence、Data Background等。厚翼科技的EFlash BIST IP更可以提供诊断(Diagnosis)方案,包括Algorithm、Command、Address、Data等,让物联网芯片开发商作为芯片错误分析的依据。

物联网的来临,许多新兴应用出现。如何让『创客』可以轻易上手一个物联网的开发平台,是众多物联网硬件开发商的共同目标,除了功能性要足够之外,『价格』是另外一项决定物联网开发平台是否会被广泛使用的决定性因素。厚翼科技的EFlash BIST IP能大幅缩短EFlash的测试时间,保护客户的测试样本(Test Pattern)与缩短EFlash BIST的开发时间。因此厚翼科技的Brains、HEART与EFlash BIST IP绝对是物联网时代最完整的内存测试解决方案。

上一篇:NI:“私人定制”的测试测量解决方案

下一篇:罗德与施瓦茨公司推出一款简单易用的EMI测量软件

推荐阅读最新更新时间:2024-03-30 23:32

数字电路答疑解惑与典型题解_北京邮电大学 (吴蕾、杨平乐、王诗兵、吴婷)

数字电路答疑解惑与典型题解_北京邮电大学 (吴蕾、杨平乐、王诗兵、吴婷) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号