随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的 ADC(Analog to Digital Converter)、DAC(Digital to Analog Converter)的指标都提出了很高的要求。比如在雷达和卫星通信中,所需要的信号带宽已经达到了 2 GHz 以上,而下一代的 5G 移动通信技术在使用毫米波频段时也可能会用到 2 GHz 以上的信号带宽。虽然有些场合(比如线性调频雷达)可能采用频段拼接的方式去实现高的带宽,但是毕竟拼接的方式比较复杂,而且对于通信或其它复杂调制信号的传输也有很多限制。

根据 Nyquist 采样定律,采样率至少要是信号带宽的 2 倍以上。同时为了支持灵活的制式、相控阵或大规模 MIMO 的波束赋形,现代的收发机模块越来越普遍采用数字中频直接采样,这其实进一步提高了对于高速 ADC/DAC 芯片的性能要求。下图是一个典型的全数字雷达收发信机模块的结构。高速数字化仪和多通道数据采集解决方案 | Keysight根据 Nyquist 采样定律,采样率至少要是信号带宽的 2 倍以上。同时为了支持灵活的制式、相控阵或大规模 MIMO 的波束赋形,现代的收发机模块越来越普遍采用数字中频直接采样,这其实进一步提高了对于高速 ADC/DAC 芯片的性能要求。下图是一个典型的全数字雷达收发信机模块的结构。

高速 ADC/DAC 在现代全数字雷达中的应用

可以看到,ADC/DAC 芯片是模拟域和数字域的边界。一旦信号转换到数字域,所有的信号都可以通过软件算法进行处理和补偿,而且这个处理过程通常不会引起额外的噪声和信号失真,因此把 ADC/DAC 芯片前移、实现全数字化处理是现代通信、雷达技术的发展趋势。

在全数字化的发展过程中,ADC/DAC 芯片需要采样或者输出越来越高的频率、越来越高带宽的信号。而在模拟到数字或者数字到模拟的转换过程中造成的噪声和信号失真通常是很难补偿的,并且会对系统性能造成重大影响。所以,高速 ADC/DAC 芯片在采样或者产生高频信号时的性能对于系统指标至关重要。

目前在很多专用领域,使用的 ADC/DAC 的采样率可以达到非常高的程度。比如 Fujitsu 公司可以提供 110G~130GHz 的 IP 核,Keysight 公司在高精度示波器里用到了单片 40GHz 采样率、10bit 的 ADC 芯片,以及 Keysight 公司在高带宽任意波发生器里用到了 92GHz 采样率、8bit 的 DAC 芯片等。这些专用的芯片通常用于特殊应用,比如光通信或者高端仪表等,比较难以单独获得。

在商用领域,很多 ADC/DAC 芯片的采样率也都已经达到了 GHz 以上,比如 TI 公司的 ADC 12J4000 是 4 GHz 采样率、12bit 分辨率的高速 ADC 芯片;而 ADI 公司的 AD9129 是 5.6 GHz 采样率、14 bit 分辨率的高速 DAC 芯片。这一方面要求 ADC 有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

随着 ADC/DAC 的采样率的提高,高速 ADC/DAC 的数字侧的接口技术也在发生着比较大的变化。

低速串行接口:很多低速的 ADC/DAC 芯片采用 I2C 或 SPI 等低速串行总线把多路并行的数字信号复用到几根串行线上进行传输。由于 I2C 或 SPI 总线的传输速度大部分在10Mbps 以下,所以这种接口主要适用于MHz 以下采样率的ADC/DAC 芯片。

并行 LVCMOS 或 LVDS 接口:对于几 MHz 甚至几百 MHz 采样率的芯片来说,由于信号复用后数据速率太高,所以基本上采用并行的数据传输方式,即每位分辨率对应 1 根数据线(比如 14 位的 ADC 芯片就采用 14 根数据线),然后这些数据线共用 1 根时钟线进行信号传输。这种方法的好处是接口时序比较简单, 但是由于每 1 位分辨率就要占用 1 根数据线,所以占用芯片管脚较多。

JESD204B 串行接口:对于更高速率的 ADC/DAC 芯片来说,由于采样时钟频率更高,时序裕量更小,采用并行 LVCMOS 或 LVDS 接口的布线难度很大,而且占用的布线空间较大。为了解决这个问题,目前更高速和小型化的ADC/DAC 芯片都开始采用串行的JESD204B 接口。JESD204B 接口是把多位要传输的数据合并到一对或几对差分线上,同时采用现在成熟的 Serdes(串行-解串行)技术用数据帧的方式进行信号传输,每对差分线都有独立的 8b/10b 编码和时钟恢复电路。采用这种方法有几个好处:首先数据传输速率更高,每对差分线按现在的标准最高可以实现 12.5 Gbps 的信号传输,可以用更少的线对实现高速数据传输;其次各对线不再共用采样时钟,这样对于各对差分线间等长的要求大大放宽;借用现代 Serdes 芯片的预加重和均衡技术可以实现更远距离的信号传输,甚至可以直接把数据直接调制到光上进行远距离传输;可以灵活更换芯片,通过调整JESD204B 接口里的帧格式,同一组数字接口可以支持不同采样率或分辨率的ADC 芯片,方便了系统更新升级。

ADC 的主要性能指标分为静态和动态两部分:

主要静态指标:

Differential Non-Linearity (DNL)

Integral Non-Linearity (INL)

Offset Error

主要动态指标:

Total harmonic distortion (THD)

Signal-to-noise plus distortion (SINAD)

Effective Number of Bits (ENOB)

Signal-to-noise ratio (SNR)

Spurious free dynamic range (SFDR)

要进行 ADC 这些众多指标的验证,可用的方法很多。最常用的方法是给 ADC 的输入端提供一个理想的正弦波信号,然后对 ADC 对这个信号采样后的数据进行采集和分析。因此,ADC 的性能测试需要多台仪器的配合并用软件对测试结果进行分析。下图是最常用的进行ADC 性能测试的方法。

在测试过程中,第 1 个信号发生器用于产生正弦波被测信号,第 2 个信号发生器用于产生采样时钟,采样后的数字信号经 FFT 处理进行频谱分析和计算得到动态指标,经过直方图统计得到静态指标。

静态指标是对正弦波的采样数据进行幅度分布的直方图统计,然后间接计算得到。如下图所示,理想正想波的幅度分布应该是左面的形状,由于非线性等的影响,分布可能会变成右边的形状,通过对实际直方图和理想直方图的对比计, 可以得出静态参数的指标。

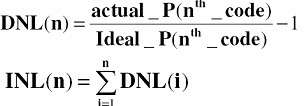

以下是 DNL 和 INL 的计算公式:

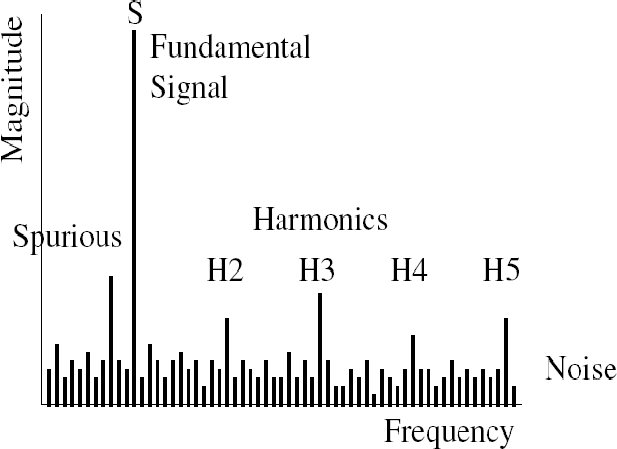

动态指标是对正弦波的采样数据进行 FFT 频谱分析,然后计算频域的失真间接得到。一个理想的正弦波经 A/D 采样,再做后频谱分析可能会变成如下图的形状。除了主信号以外,由于ADC 芯片的噪声和失真,在频谱上还额外产生了很多噪声、谐波和杂散,通过对这些分量的运算,可以得到ADC 的动态参数。

通过 FFT 频谱分析测试动态参数

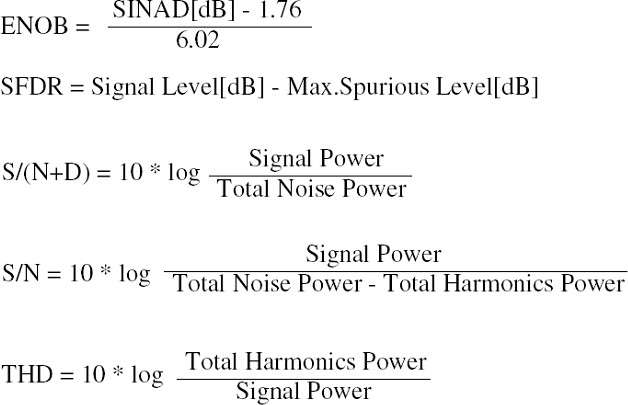

下面是动态参数的计算公式:

对于产生被测信号和采样时钟的信号发生器来说,为了得到比较理想的测试效果, 要求其时间抖动(或者相位噪声)性能要足够小,因为采样时钟的抖动会造成采样 位置的偏差,而采样位置的偏差会带来采样幅度的偏差,从而带来额外的噪声,从 而制约信噪比的测量结果。下图是时钟或者信号抖动引起信噪比恶化的示意图,以 及根据信噪比要求及输入信号频率计算信号抖动要求的公式。

上一篇:混频器噪声系数测试时,校准之后增益和噪声系数不为零?

下一篇:电阻率测量基础

推荐阅读最新更新时间:2024-11-16 22:06

- 使用 Clare OptoMOS 组件的FXO/DAA 设计,使用 TS117 进行来电显示检测

- MCP6S22DM-PICTL、PGA PICtail 演示板评估和演示 MCP6S28 可编程和 MCP6S91/2/3 增益放大器(PGA)

- OP184FSZ-REEL7 高端负载电流监控器的典型应用

- DI-113 - 用于便携式音频播放器的5W、高效率的充电器

- LT6654BHS6-2.5 升压输出电流电压基准的典型应用

- Nit6X_JTAG,适用于 BD-SL-i.MX6(以前的 SABRE Lite)和 Nitrogen6X 的 JTAG 适配器

- 使用 Analog Devices 的 LT1764AEQ-1.5 的参考设计

- LT6656BCDC-5、5V 低功率精密高压电源监视器的典型应用

- DC2838A,用于具有 150V、1.5A 开关的 LT8365 低 IQ 升压/SEPIC/反相稳压器的演示板

- Rz7899电机驱动板_开源

网络操作系统 (李治西编著)

网络操作系统 (李治西编著) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号