引言

MPEG-4视频编码技术可以在较小的带宽下传输高质量的视频数据,节省大量存储空间,但编码复杂度也较高,目前丰要有3种实现方案:在通用PC上编程实现;通过ASIC硬件实现以及使用通用DSP芯片实现。与前两者相比,通用DSP芯片实现方案具有以下优势:运算性能强;可升级性好,与PC类似,通用DSP芯片的功能仍是通过编程来实现的,能快速、方便地进行软件升级及添加新的功能,以适应技术发展和市场变化;成本低、功耗低、适应场合广泛。

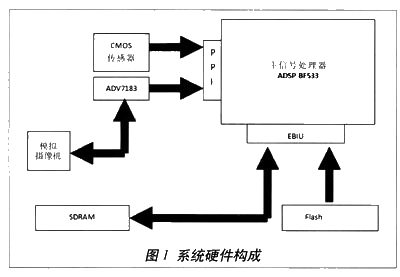

系统硬件设计

编码系统处理核心为ADSP-BF533(以下简称BF533),利用其多功能并行接口PPI采集视频数据,该PPI具有DMA功能,无需内核干预便可进行高速数据传输,传输完成后可自动向内核发出DMA中断。

视频采集部分选用0mniVision公司的CIF级彩色CMOS图像传感芯片OV6630,其最大分辨率为352×288,采集速率最高可达60fps,且片内硬件实现了原始RGB数据到4:2:2YUV格式数据的转换,用户无需自行编写复杂的RGB转YUV应用程序,大大减少了代码量,很适合用作MPEG-4编码。

设置OV6630输出为4:2:2 YUV视频数据格式,BF533的PPI即可直接接收该格式视频数据。二者可实现无缝连接,无需中间电路。

考虑到目前还有大量模拟制式的摄像机仍在广泛应用,系统中还增加了视频ADC ADV7183,该芯片可以把PAL制模拟电视信号转为ITU-R656标准4:2:2格式数字视频,同样将ADV7183输出端口与BF533的PPI相连。这样,既可以采用系统自带CMOS图像传感器采集视频,也可以外接PAL制模拟摄像机,用户可自由选择。

由于BF533片内存储空间有限,而视频采集、编码数据量巨大,选用一片Hynix公司的4MBSDRAM HY57V56162(内含4个内部子集)作为BF533片外大容量动态存储器。同时,为存放程序启动代码,利用一片容量为1MB的闪存芯片PSD4256G6V构成BF533的片外非易失性存储器。系统硬件构成如图1所示。

编码器设计实现

存储器空间分配

BF533采用统一的32位、共4GB可寻址空间,包括位于片内的L1高速SRAM,片外的同步存储器空间SDRAMSpace,以及异步存储器空间(A syn chronousMemory Space)。

片内Ll SRAM包括:64KB指令SRAM、16KB指令Cache/SRAM、32KB数据SRAM、32KB数据Cache/SRAM,以及4KB便签存储器。

L1 SRAM工作在内核时钟频率,内核可以对其进行高速带宽访问。它是所有存储器中访问速度最快的,但容量有限,因此,只应将那些最关键的代码和数据存放在L1SRAM里。同时,指令Cache和数据Cache全部使能,这样可以大大提高访问片外存储器的效率。Cache设置是通过相应的I M E M_C O N T R O L、DMEM_CONTROL,以及CPLB寄存器配置实现的。

由于BF533片内存储空间有限,而原始视频数据量较大:CIF级4:2:2格式每帧图像占用的空间为202752字节,如果采用模拟PAL制式视频输入,每帧占用空间更是高达829440字节,只能将其放至SDRAM中。同样,视频编码数据也应存放在SDRAM中。此外,系统启动完成Boot loader引导后,主要关键代码放在片内L1程序SRAM中执行,但大部分程序代码仍需从SDRAM中执行。由于SDRAM特殊的读/写方式,如果下次访问内存页与当前活动页(Active Page)不同,即出现了页错失(Page Miss),SDRAM就必须首先关闭当前页,再打开新的页,大大降低了SDRAM读写速率。而该系统中SDRAM又需存储多种数据,内核、DMA均需要频繁访问SDRAM,因此,应精心分配SDRAM空间,以使页错失现象尽量少发生。

BF533的SDRAM控制器(SDC)可以支持SDRAM每个内部子集中的一个活动页,且在这4个I-Bank中进行切换时无需任何延迟。这样,将不同的数据、代码映射至不同的I-Bank,可使页错失现象降到最少,进而改善访问SDRAM的效率。

由于需要实时编码,为保证视频采集和压缩可以同步执行,采用乒乓缓冲技术:设置了两块视频帧接收缓冲区BUF1和BUF2,采用BF533的DMA传输链方式进行传输。当某一DMA缓冲区填满后,内核对其作MPEG-4编码(同时也在构建参考帧),此时DMA开始对另一块缓冲区进行填充。由于BUF1、BUF2、程序代码以及参考帧均位于不同的I-Bank,减少了SDRAM页面切换的机会,实现了对SDRAM的高效访问。

MPEG-4程序流程

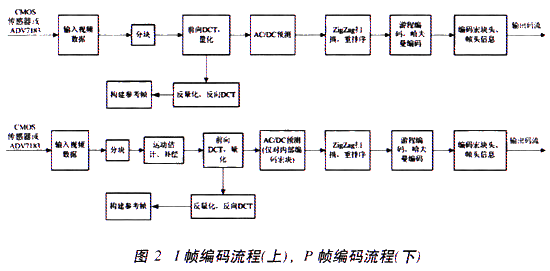

MPEG-4编码是基于宏块(Macro Block)进行的,每个宏块包含4个8×8亮度子块和2个8×8色度子块。MPEG-4编码原理主要包括对I帧和P帧的编码,P帧比I帧多出了运动估计和补偿模块,二者编码流程如图2所示。

代码编写及优化

BF533支持C/C++高级语言,但高级语言执行效率较低,为达到最大执行效率,采用全汇编语言实现MPEG-4编码。

对于I帧编码,主要的运算量是前向离散余弦变换FDCT和反向离散余弦变换IDCT,这里采用了ADI提供的优化代码,它基于chen氏快速DCT算法,大量运用了BF533特有的并行指令,完成一次8×8 DCT仅需293个时钟周期。

与I帧相比,P帧编码相对复杂,其中,运动估计是P帧编码最费时的部分,即在参考帧中搜索与当前编码宏块或子块最匹配的位置。

SAD(绝对误差和)准则具有无需乘除运算、实现简单方便等优点,选用它作为运动估计匹配准则。

运动估计搜索算法则采用菱形搜索法(又称钻石搜索法),搜索精度为半像素,菱形搜索法具有简单、鲁棒、高效的特点。

Blackfin汇编指令集中有专门用于SAD计算的指令SAA(src_reg_O,src_reg_1),一条该指令即可同时完成4个字节的SAD计算。此外,综合使用其它一些视频专用操作指

令,如BYTEPACK(_将4个字节打包至一个3 2位寄存器中)、BYTEUNPACK(与BYTEPACK功能相反)、BYTEOPl6M(对4个字节作减法处理),可以使代码运行效率得到显著改善。

BF533集成开发环境VisualDSP++中还提供了Profile功能,可以利用该功能对程序代码性能进行评估,发现程序执行的瓶颈,从而进行有针对性的优化。主要的优化方法有:1.尽量减少分支、条件判断指令,因为这些指令会破坏BF533流水线,造成额外的时钟延迟;同时,对部分较简单的子程序用宏改写,免去子程序调用过程中的堆栈操作和参数传递;

2.采用并行执行指令,BF533并非超标量结构DSP,但仍能有限地支持最多3条指令并行执行,如:saa(r1:0,r3:2)Ⅱr0=[i0++]Ⅱr2=[i1++];使用该并行指令即可在一个时钟周期内完成4个字节的SAD计算,同时完成r0、r2的数据更新,以便下次计算;

3.在DCT/IDCT的量化过程及其它一些模块中,要牵涉到除法,而BF533计算除法需要耗费大量时钟周期,因此,这里将除法变为乘以量化因子的倒数,求倒数可以通过查找表方式实现。再结合移位操作,即可在基本不损失精度的同时达到高效计算除法的目的。

经过前述的优化过程后,成功地在BF533上实现了MPEG-4 SP的CIF级实时编码。此外,对于CIF级CMOS传感器OV6630,系统可以直接对其实时编码。但如果是外接PAL制式模拟摄像头,经ADV7183作A/D转换后,其分辨率为720×576,受BF533的性能限制,尚无法对该级别分辨率做到实时编码,因此,应先使其分辨率降为352×288,然后再作:MPEG-4编码。

实验结果

BF533内核时钟(CLK)设为594MHz,系统时钟(SLK)为118.8MHz。选取CIF级标准测试序列flower(帧速率为25fps,共75帧)对系统进行验证。

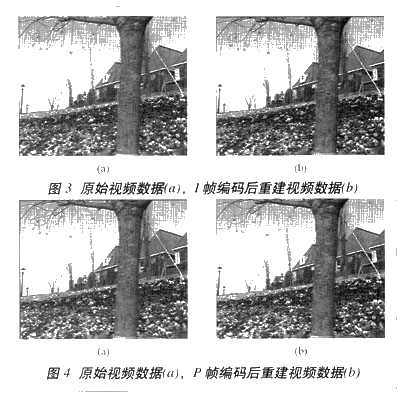

图3、图4给出了分别采用I帧编码和P帧编码后的重建图像。I帧编码压缩率为11.5:1,重建图像信噪比为33.43dB。P帧编码压缩率则达到了65.7:1,重建图像信噪比为32.65dB。经采用BF533片内实时时钟RTC精确计时,整个视频序列共75帧,编码耗费2.27s,平均编码率达到了33fps,满足实时编码要求。

结语

本文介绍了CIF级别的MPEG-4 SP实时编码在BF533 DSP;DSP片上的实现,该编码器可以灵活地选用系统自带CMOS传感器及用户自选PAL制模拟摄像机两种视频采集源。该系统可以用在IP可视电话、交通检测、超市监视、智能小区安保等领域,具有很强的实用价值。

上一篇:基于DSP的PCI高速测控系统结构的研究

下一篇:TS201在数字信号处理设计中的应用

推荐阅读最新更新时间:2024-05-13 18:36

- 宁德时代巧克力换电生态大会将举行,什么是“巧克力换电”?1.5分钟换电能实现吗?

- 新型生物材料与高端医疗器械广东研究院、远诺技术转移中心加入面向初创企业的 MathWorks

- S5PV210 Linux字符驱动之PWM蜂鸣器驱动

- 尼得科机床新增可实现高效加工的高速主轴产品线

- Gartner发布2025年影响基础设施和运营的重要趋势

- 智谱清言英特尔酷睿Ultra专享版发布,离线模型玩转AIPC

- Bourns推出全新高效能、超紧凑型气体放电管 (GDT) 浪涌保护解决方案

- S5PV210之UBOOT-2011.06启动过程解析

- 六个理由告诉您为什么应该将模拟无线麦克风更换为数字无线麦克风

- S5PV210启动过程分析

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉)

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉) 人工智能算法(卷2)-受大自然启发的算法

人工智能算法(卷2)-受大自然启发的算法 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号