摘要:文中介绍了MOTOROLA公司的嵌入式微处理器MCF5249的原理、特点和引脚功能,说明了基于该处理器和嵌入式操作系统UCLINUX的网络相机结构,给出了用MCF5249进行网络相机设计时的资源分配情况及电路设计注意事项。

关键词:MCF5249;嵌入式微处理器;JPEG

1 概述

MCF5249是motorola公司推出的32位嵌入式微处理器,该器件以ColdFire 32 位微处理机体系结构为基础,并带有96kB 的片内SRAM、8kB 指令高速缓存、两个独立UART 和16 位定时器以及一个PLL 时钟,同时还带有软件监视时钟、GPIO 线路、两个I2C接口、QSPI口、4通道DMA和一个非粘合性SDRAM 控制器。此外,该器件还集成了一个12位DAC和一个增强型累积乘法EMAC单元,可用来为音频和其它应用提供快速运算和信号处理所需的DSP 功能。MCF5249的最高工作频率为140MHz,性能可达125Dhrystone 2.1 MIPS,而功耗仅为每兆赫1.3mW。因而可广泛用于音频设备、成像、生物统计学和工业控制等领域。

2 性能特点及引脚说明

MCF5249内含V2 ColdFire 处理器核、96kB 静态SRAM、8kB 指令缓存、EMAC增强型累积乘法单元、2 个独立的通用异步收发器UARTs、2 个独立的16 位定时器、两个独立的I2C 接口、以及16-bit宽度的四通道的SDRAM控制器等模块,另外MCF5249还集成了PLL和软件看门狗Software watchdog、数字音频传输和接收口(符合IEC958音频协议)及IDE和SmartMedia接口等。图1所示是MCF5249的主要功能框图。

MCF5249能够支持CD-ROM和CD-ROM XA块编码和解码功能,并具有4个可编程选择的后台实时处理Debug模块。

图1

MCF5249芯片的内核电压为1.8V,I/O电压为3.3V,具有160脚MAPBGA(140MHz的最高频率)和144脚QFP(120MHz的最高频率)两种封装形式。其中160脚的MCF5249比144脚增加了QSPI CS1等功能管脚.

2.1 采用MCF5249构成的网络相机

基于MCF5249的上述功能,笔者设计了一种能够对采集到的图像进行实时网络传输的嵌入式相机系统。如图3所示它由图像传感器、帧存储器、网络控制器、键盘、显示模块等部分组成。其中图像传感器采用OMNIVISION公司的OV9620高分辨率CMOS图像传感器。该传感器具有1280%26;#215;1024的分辨率和1024等级的色度信息。最高拍摄速度可达每秒十五帧。OV9620的控制端口与MCF5249的I2C口直接相连。为了使输出的图像数据方便地同帧存储器相连,笔者设计时只用了高八位数据。帧存储器采用ISSI公司的18Mbit存储器IS61LPD102418A。该存储器的数据读取速率为7ns,且控制简单,易于使用。设置存储器是由于像素的速率与MCF5249的速率不匹配,而用其起缓存作用的。网络控制器选用DAVICOM公司的DM9000快速以太网控制处理器,该处理器配备有标准10M以太网接口,包括MAC和PHY。物理层支持以太网接口协议。由于数据有时是以猝发形式收到的,因此,DM9000还集成有接收缓冲区,以便在接收到数据时能把数据放到这个缓冲区中,然后由数据链路层直接从该缓冲区里取走数据。链路层通常包括操作系统中的设备驱动程序和计算机中对应的网络接口卡,它们一起处理与电缆的物理接口细节数据,它的缓冲区可用来暂时存储要发送或接收的帧。MCF5249在使用时还需辅以4M%26;#215;16位数据宽度的SDRAM和4MB的在线可擦除FLASH MX29LV160BTC。

该系统工作时,首先通过FLASH自动加载操作系统,然后由系统控制MCF5249的I2C接口以控制传感器曝光并将一帧图像写入SRAM。采集结束后,MCF5249通过GPIO口读入像素数据,并通过内部嵌入的JPEG图像压缩编码模块将其转换成易于网络传输的低数据量图像数据流,然后输出给DM9000网络控制器,最后传输至网络。

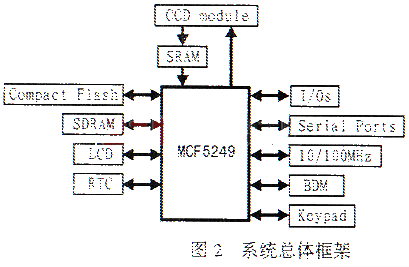

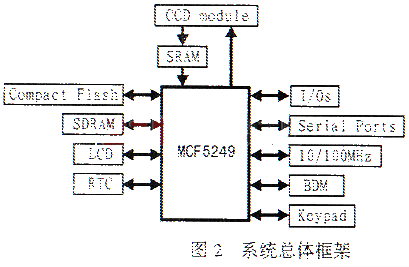

针对不同要求,可将该相机的图像分辨率分为320%26;#215;240、640%26;#215;480、1024%26;#215;769三种等级,不同等级分辨率对应的图像处理速度分别为15fps(frame per second) 、10fps、3fps。图2所示是该系统的总体框架。其中的显示模块采用6963系列128%26;#215;64的LCD,主要用来显示系统时钟、系统状态以及卡的ID号等。

4 结束语

在采用MCF5249设计网络图像传输系统时,还应注意以下几点:

(1) 合理的地层和电源层隔离

建议使用较为完整的一个PLANE 作为地层,如果存在多个“地”(例如:数字地,模拟地,保护地等),则应在同一个地层上适当分割。其电源层也应与之类似。此外,还应当注意低噪声电路部分电源和高噪声电路部分电源的隔离或滤波。

(2) 合理的去耦电容排布

在电源进线端,各个数字芯片电源引脚的附近一般都分布有适当的去耦电容。设计时应使之与核心板隔离,同时还应在各个端口使用适当的输入输出缓冲。

针对不同要求,可将该相机的图像分辨率分为320%26;#215;240、640%26;#215;480、1024%26;#215;769三种等级,不同等级分辨率对应的图像处理速度分别为15fps(frame per second) 、10fps、3fps。图2所示是该系统的总体框架。其中的显示模块采用6963系列128%26;#215;64的LCD,主要用来显示系统时钟、系统状态以及卡的ID号等。

4 结束语

在采用MCF5249设计网络图像传输系统时,还应注意以下几点:

(1) 合理的地层和电源层隔离

建议使用较为完整的一个PLANE 作为地层,如果存在多个“地”(例如:数字地,模拟地,保护地等),则应在同一个地层上适当分割。其电源层也应与之类似。此外,还应当注意低噪声电路部分电源和高噪声电路部分电源的隔离或滤波。

(2) 合理的去耦电容排布

在电源进线端,各个数字芯片电源引脚的附近一般都分布有适当的去耦电容。设计时应使之与核心板隔离,同时还应在各个端口使用适当的输入输出缓冲。

引用地址:嵌入式微处理器MCF5249及其应用

针对不同要求,可将该相机的图像分辨率分为320%26;#215;240、640%26;#215;480、1024%26;#215;769三种等级,不同等级分辨率对应的图像处理速度分别为15fps(frame per second) 、10fps、3fps。图2所示是该系统的总体框架。其中的显示模块采用6963系列128%26;#215;64的LCD,主要用来显示系统时钟、系统状态以及卡的ID号等。

4 结束语

在采用MCF5249设计网络图像传输系统时,还应注意以下几点:

(1) 合理的地层和电源层隔离

建议使用较为完整的一个PLANE 作为地层,如果存在多个“地”(例如:数字地,模拟地,保护地等),则应在同一个地层上适当分割。其电源层也应与之类似。此外,还应当注意低噪声电路部分电源和高噪声电路部分电源的隔离或滤波。

(2) 合理的去耦电容排布

在电源进线端,各个数字芯片电源引脚的附近一般都分布有适当的去耦电容。设计时应使之与核心板隔离,同时还应在各个端口使用适当的输入输出缓冲。

针对不同要求,可将该相机的图像分辨率分为320%26;#215;240、640%26;#215;480、1024%26;#215;769三种等级,不同等级分辨率对应的图像处理速度分别为15fps(frame per second) 、10fps、3fps。图2所示是该系统的总体框架。其中的显示模块采用6963系列128%26;#215;64的LCD,主要用来显示系统时钟、系统状态以及卡的ID号等。

4 结束语

在采用MCF5249设计网络图像传输系统时,还应注意以下几点:

(1) 合理的地层和电源层隔离

建议使用较为完整的一个PLANE 作为地层,如果存在多个“地”(例如:数字地,模拟地,保护地等),则应在同一个地层上适当分割。其电源层也应与之类似。此外,还应当注意低噪声电路部分电源和高噪声电路部分电源的隔离或滤波。

(2) 合理的去耦电容排布

在电源进线端,各个数字芯片电源引脚的附近一般都分布有适当的去耦电容。设计时应使之与核心板隔离,同时还应在各个端口使用适当的输入输出缓冲。

上一篇:基于Web的嵌入式设备管理

下一篇:32位RISC CPU ARM芯片的应用和选型

小广播

热门活动

换一批

更多

最新应用文章

更多精选电路图

更多热门文章

更多每日新闻

- CGD和Qorvo将共同革新电机控制解决方案

- 是德科技 FieldFox 手持式分析仪配合 VDI 扩频模块,实现毫米波分析功能

- 贸泽开售可精确测量CO2水平的 英飞凌PASCO2V15 XENSIV PAS CO2 5V传感器

- 玩法进阶,浩亭让您的PCB板端连接达到新高度!

- 长城汽车研发新篇章:固态电池技术引领未来

- 纳芯微提供全场景GaN驱动IC解决方案

- 解读华为固态电池新专利,2030 叫板宁德时代?

- 让纯电/插混车抓狂?中企推全球首款-40℃可放电增混电池,不怕冷

- 智驾域控知多少:中低端车型加速上车,行泊一体方案占主体

- Foresight推出六款先进立体传感器套件 彻底改变工业和汽车3D感知

更多往期活动

11月15日历史上的今天

厂商技术中心

控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用 LM6172MDR

LM6172MDR

京公网安备 11010802033920号

京公网安备 11010802033920号