无损探伤技术是在不损坏工件或原材料工作状态的前提下,对被检验部件的表面和内部质量进行检查的一种测试手段。超声波探伤就是利用超声能透入金属材料的深处,并由一截面进入另一截面时,在界面边缘发生反射的特点来检查零件缺陷的一种方法。当超声波束自零件表面由探头通至金属内部,遇到缺陷与零件底面时就分别发生反射波来,在荧光屏上形成脉冲波形,根据这些脉冲波形来判断缺陷位置和大小。

随着超声波探伤技术的发展,对数字信号的处理与分析已不再仅仅是辅助技术,而是一种基本技术,由此出现了各种全数字化的超声波检测设备。但早期的数字化设备仅停留在超声波检测频率较低频段的信号处理上,主要是受到高速A/D和高速存储技术的限制,由于计算机总线技术应用的瓶颈,也不能实时多通道传送波形数据到计算机去处理,声源定位信号分析等实时显示分析的功能只能由硬件输出的参数完成。

而A/D转换器和高效率微处理器的问世克服了在高频领域应用模拟电子技术受到的各种限制。数字化全波形超声波探伤设备就是由计算机作为主机,以单片机芯片为主构成的专用板卡统一控制管理超声系统。这种设备综合应用了高速数据采集技术、A/D转换技术、大容量缓冲技术、多通道切换技术、数据存储技术和数据管理软件技术等先进的数据信号处理技术,使得多通道声发射波形的采集和分析不再困难。因此,如何开发和研制更具先进性、创新性、科学性和实用性的全数字式超声波检测设备和系统,已成为一项紧迫性的任务。

本文主要介绍一种基于高速信号处理技术的超声波无损检测系统的典型设计方案,从系统的总体设计、单元电路设计和程序设计等方面阐述和分析了设计原理、电路和软件的结构与功能等,系统方案具有较高的技术含量和实用价值。

总体设计

系统的总体结构设计如图1所示。首先,由高压脉冲发生器发射高压脉冲,其经能量转换电路形成超声波信号,遇到缺陷或杂质时产生反射波,再经能量转换电路转换为电压信号,最后经放大电路放大、A/D转换后,形成数字量,写入高速数据缓存器中;然后,由PCI接口电路将缓存器中的数据适时地通过PCI总线送到本系统的微处理器进行处理,实现与外部计算机通信、显示、打印、存储和控制等功能。

图1 系统总体设计图

本系统采用转换速率为60MHz的8位高速A/D转换电路以满足数据采集的要求。为对A/D芯片输出的高速数据进行缓冲,并充分利用PCI总线带宽,采用了32KB的高速数据缓存电路;对于多通道检测的要求,设计了通道选择控制电路以实现通道之间的切换;采用高增益的高频宽带放大电路对缺陷回波信号进行整理和放大。

单元电路设计

1 放大电路设计

本系统采用带触发的直流逆变电路产生高压脉冲,采用多路模拟通道选择电路实现通道切换以满足多通道探伤的要求。模拟信号经放大、滤波后,作为A/D转换电路的输入。放大电路采用增益为80dB、带宽为15MHz、分辨率为1dB的放大器,并且以数字电位器进行放大增益的动态调整,可实现放大器的动态响应和频带范围与尖峰回波脉冲信号的匹配。

2 A/D转换电路设计

A/D转换电路通常可分为积分型和比较型。积分型A/D转换器的特点是抗干扰能力强、精度高,但速率较低,因此高速A/D转换器一般采用比较型。本系统采用ADS830,该芯片信噪比高、功耗低、非线性畸变小,广泛应用于图像处理、数字通信和视频测试系统中。它有共模和差模两种信号输入方式,输出的数字量可直接与5V或3.3V芯片接口。超声波无损检测对象基本上为钢体材料,其在钢中传播时,纵波CL的传播速度为5900m/s,横波CS的传播速度为3230m/s,缺陷回波信号通常宽度约10~100ns,因此在钢中的传播速度很快。超声波在工件中的传播时间很短,尤其对于薄壁材料检测,传播距离更短,因此,为了得到足够的分辨率,要有足够的检测和采样频率才能满足信号采集的要求。ADS830的精度为8位,最高采样频率为60MHz,可满足一般无损检测系统对数据采集精度和采样频率的要求。

3 数据缓存器设计

由于在PCI 总线控制器S5933的缓存器中只有8个32位寄存器,对于实时高速数据,可能会由于延时造成数据的丢失,因此需要进行扩展。本系统采用IDT公司的IDT72V36100作为高速数据的缓存。IDT72V36100可以提供65536×36bit的存储单元,并且具有配置灵活的特点,可以通过设置确定输入输出的数据宽度。对于宽度为8bit的输入数据,为了充分利用PCI 总线的性能,将输出数据的宽度设为32bit。此外,IDT72V36100也提供了丰富的状态信号,可以利用它们作为控制信号。IDT72V36100需要在写操作之前进行主复位,以设置一些初始状态,所以需要上电复位。本设计选用上电复位芯片MAX814T,在上电时对缓存电路进行复位。缓存电路的初始设置主要为:BM、OW、IW全为“低”,使输入输出宽度为32位;FWFT/SI为“低”表示标准IDT模式,只要REN和WEN使能,就可以读写数据;OE为“低”,表示允许输出端输出;IP为“低”表示不加校验位;PFM为“高”表示同步方式,即在时钟上升沿读写数据。高速数据缓存电路使A/D芯片可以不必工作在PCI同步时钟下,提高了A/D芯片的利用率和数据的吞吐率。高速数据缓存电路由于具有“先进先出”的特性,数据的读写都无须提供地址信号,也简化了电路的设计。

4 时序逻辑控制器设计

本设计采用了DMA传输的模式,为此需要通过相应的逻辑控制将扩展的存储空间结合为一个整体。由此采用一片XC9536的CPLD器件作为逻辑控制器。

5 PCI接口电路设计

PCI总线的最大数据传输速率为132~264Mb/s,远远超过ISA总线5Mb/s的速率,是目前使用较为广泛的一种总线。在高速信号的实时处理中,利用PCI总线将采集数据直接传送到微机系统内存,可有效解决数据的实时传输和存储,为信号的实时处理提供方便。PCI 总线执行协议比较复杂,总线的接口逻辑也非常复杂,为简化电路设计和提高可靠性,本设计采用了AMCC公司的总线控制器芯片S5933。

图2 S5933内部结构图

图2为S5933的内部结构框图。从外部看,它提供了PCI Bus、External BIOS及ADD-ON三个接口。因此,复杂的PCI接口规范完全由S5933实现,我们只需设计ADD-ON接口电路及编制可选的External BIOS即可。为便于ADD-ON接口电路设计,还提供了三组寄存器,分别用于不同的接口设计。直通数据寄存器组用于目标设备方式Burst Mode数据传输;Mailboxes寄存器组用于CPU与ADD-ON之间少量数据通信,如CPU传输命令给ADD-ON等;FIFO寄存器组用于主控设备方式Burst Mode数据传输,有同步、异步之分。此外, PCI和ADD-ON接口各提供了两组操作寄存器组,用于接口控制,分别称为PCI Bus操作寄存器组和ADD-ON Bus操作寄存器组。

程序设计

1 驱动程序设计

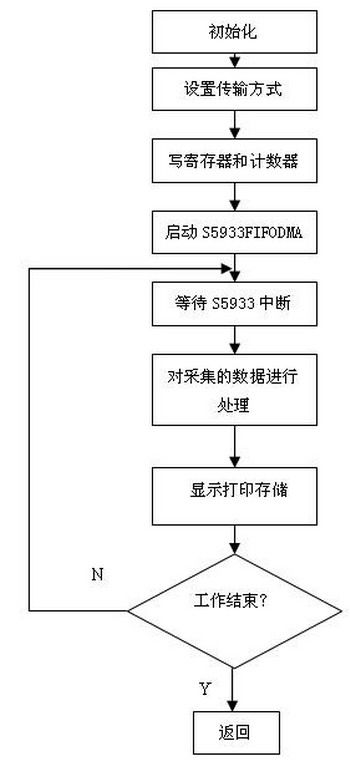

S5933驱动程序根据Windows驱动程序模型WDM设计,运行在Win2000平台上,支持即插即用,采用基于数据包的DMA传输方式,每次最大传输64KB。当应用程序请求从系统读数据时,内核I/O管理器将此请求打包成一个IRP(I/O请求包),并调用驱动程序的读例程。如果设备不忙,就启动DMA传输,否则将此IRP加入IRP队列中。启动设备DMA读时,先用数据传输的存储地址和数据长度设置写地址寄存器和写传送计数寄存器,再设置中断控制状态寄存器(INTCSR),使DMA完成时能触发中断,最后设置控制/状态寄存器(MCSR)来启动DMA读。当本次DMA传输完成时,系统产生中断,I/O管理器调用中断服务例程和DpcForIsr完成此IRP,并从IRP队列中取出下一个IRP,启动下一次DMA。下一次中断发生时同样处理,这样不断地进行DMA传输,直到IRP队列空为止。驱动程序主要采用中断方式来实现,程序流程如图3所示。

图3 驱动程序流程图

由总线控制器S5933的结构可知,设备驱动程序需要实现双字I/O操作和物理内存管理。双字I/O的操作相对简单,调用虚拟机管理器的SIMULATE_VM_IO例程即可,但物理内存管理较复杂。由于S5933发起的DMA操作需要物理内存的起始地址,因此必须涉及页面级的物理内存操作,故采用下述内存管理策略:应用程序加载驱动程序,加载成功后发送申请缓冲区的事件给驱动程序,驱动程序使用PAGEALLOCATE例程得到地址连续的适当长度的物理内存,锁定缓冲区并将物理地址逆映射为线性地址,将物理首地址填入S5933的写RAM地址寄存器,允许S5933进行主控DMA传输,传输完毕时,应用程序请求驱动程序释放上述物理内存。

2 用户应用程序设计

本系统应用程序采用结构化、模块化的设计方法,采用一片8031单片机作为CPU,各模块均完成一定的独立功能, 便于系统的功能扩充和维护。系统操作由多级中文菜单提示进行。显示模块程序设计模式多,显示内容丰富,可显示中文菜单、回波波形、报警闸门、移动标尺、测量结果等。主控模块用于控制检测流程,实现数据的采集、处理和分析,并调用相应的功能模块实现显示和打印等。通信模块程序用于CPU与外部PC的串行通信,将探伤波形及结果等相关信息传送至PC做进一步分析、处理或存档。键盘管理模块扩展了一个的小键盘,分成功能键和数字键,功能键用于选择操作类型,数字键用于参数输入,当键按下时向CPU申请中断。打印模块用于控制微型打印机打印结果和缺陷回波等。

上一篇:基于高精度时间测量技术的声速仪设计

下一篇:RIGOL DM3064试用手记—结合多普勒效应

推荐阅读最新更新时间:2024-05-13 21:01

【干货】浅谈电动汽车充电系统

【干货】浅谈电动汽车充电系统 中国汽车技术论坛-制动系统标准

中国汽车技术论坛-制动系统标准 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号