引言

E1是我国电信传输网一次群使用的传输标准,由于我国的E1资源十分丰富, 这样的传输路径非常容易获得,灵活利用现有丰富的E1信道来传输HDLC数据,可以节约大量传输成本。通常,一路HDLC数据仅通过一路E1信道传输,但是如果HDLC数据的速率很大,一路E1信号的带宽不足以传输,那么HDLC数据就要分接到M路E1信道中传输,接收端再把M路E1信号合路恢复出HDLC数据,M路E1信号如果传输路径不同,肯定会导致不同的延迟,本系统设计时,允许各路E1信号的最大延迟为64ms。

系统E1帧结构设计

本系统中的E1码流的帧结构可以参照CCITT G.732、G.704或G.706建议给出的PCM基群30/32路系统帧结构得到,但又有所不同。

信息位的组成

本系统所要传输的净负荷(信息位)是N×64Kbps的HDLC数据,标准E1中的TS16信令时隙与TS1~TS15及TS17~TS31共31个时隙可以传送净负荷。所以,N和M满足关系式N≤31×M。对于最大情况,即N=124,M=4时,净负荷占用31个时隙。当N<124,以至不能填满所有31个时隙,则固定填入无效位‘1’。

TS0时隙的设计

考虑到系统要能实现将一路N×64Kbps的HDLC数据按比特分接在M路E1信道中独立传输,并在接收端通过合路正确恢复出此数据,合路过程要求M路E1信号完全同步,而实际线路中各路之间有不同程度的延迟,这就要求系统具有延时缓冲能力。在此期间利用一个存储器对数据进行缓冲保存。而为了辨别某一路保存在SRAM中的CRC复帧应该和其它路保存在SRAM中的相应CRC复帧合路,即为了实现复帧同步,就需要对每一个CRC复帧加上标号,也就是加上复帧定位码。此外,由于HDLC数据是按比特分接在M路E1信道中传输的,当M=2,3,4时,那么在接收端就必须按照发送时分接的顺序将M路E1信道中的信息位按比特复接成HDLC数据。所以各路E1都需要一个代表分/复接顺序的路标号。为了充分利用E1信道资源 ,利用E1奇帧帧头后三个备用比特为用户提供一个12Kbps的同步数据通道,也可以作为低速的异步数据通道,如常用的2400、4800、9600bps的RS-232信号。

系统设计

硬件设计

系统的硬件部分包括一片FPGA和一块SRAM,FPGA选用Altera公司Cyclone系列EP1C6。Cyclone系列器件是低价格,中等密度的FPGA,内部有5980个逻辑单元,20个4Kbit的RAM块和2个内部锁相环。

由于系统允许各路E1信道可以有最大64ms的延时,一个复帧周期为2ms,即最大延迟为32个复帧时间。一个复帧由16个基本帧组成,32个复帧的的比特数为32×256×16=128Kbit,那么各路需要RAM的最大容量为128Kbit。由于最大路数M=4,所以系统所需的RAM最大容量为4×128Kbit= 512Kbit。而EP1C6内部只有80Kbit的RAM,所以选择使用外接RAM的方法,本系统选用Inbond公司的W24L01,其容量为1024Kbit。

通过VHDL实现系统功能

系统采用自顶向下的EDA设计流程,利用VHDL语言编程实现系统功能。

发送部分主要由锁相环模块、分路模块、成帧模块、CRC校验模块和串行扰码模块组成。在主时钟模式下,由本地晶振经有理数分频产生N×64KHz时钟和2.048MHz时钟,N×64KHz时钟作为HDLC数据的时钟产生源,N×64Kbps的HDLC先经过串/并转换,并写到M个缓存器中,然后用2.048MHz时钟读出,并将其插入到E1帧相应的时隙中,组成M路E1信号,并经过CRC-4校验,最后经过串行扰码,发送出去。在从时钟模式下,N×64KHz时钟由HDLC提供,2.048MHz时钟由锁相环模块从N×64Kbps的HDLC中提取。时钟模式的选择及M、N的数值都可以在FPGA内部通过VHDL语言编程设定。

接收部分包括锁相模块、帧头检测模块、解扰码模块、读写RAM模块以及合路模块。在接收部分,先用锁相环通过输入的E1信号锁出2.048MHz的同步时钟和N×64KHz时钟,用2.048MHz的时钟对E1信号进行帧头检测,找到帧头后,系统进入帧同步状态,然后解扰码,CRC反校验,以及提取其它各种控制信息和数据。解扰码以后的数据经串/并转换后输出FPGA,存到片外RAM中。收到控制信息后,FPGA开始从RAM中读取数据,并在N×64KHz时钟的控制下进行并/串转换,去帧头,最后合成一路N×64Kbps的HDLC输出信号。

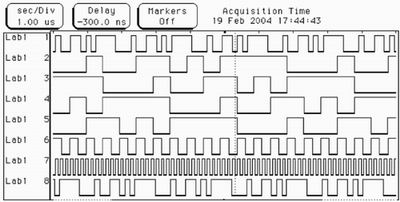

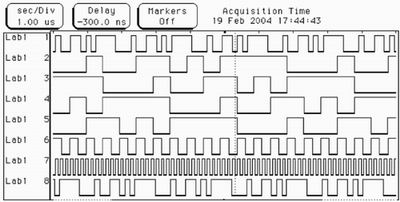

图1 仿真波形图

仿真与测试

对整个系统和每个子模块都进行了功能仿真和后仿真。功能仿真平台为ModelSim + 5.5f ,综合平台为FPGA Express 3.5,后仿真平台为Altera Quartus3.0。用逻辑分析仪HP54645D实测波形如图1所示(取M=4,N=104)。

结语

通过对FPGA进行VHDL编程,实现了将速率为N×64Kbps (N=1~124)的HDLC数据按比特分接至M路(M=1~4)E1信道中传输,并充分利用E1奇帧的TS0时隙,为用户提供12Kbps的同步数据传输通道,而且允许各路E1有64ms的时延。本文设计的HDLC转E1传输控制器也可以作为其它协议转换器的一个过渡桥梁。例如可以将10Base-T的以太网信号,先经过以太网转HDLC协议控制器(如ADMtek公司生产的ADM6993芯片),然后通过HDLC转E1传输控制器,从而实现了Ethernet over TDM的功能。

关键字:时钟 信道 模块

引用地址:

基于FPGA的HDLC转E1传输控制器的实现

推荐阅读最新更新时间:2024-05-13 18:13

一种嵌入式时钟管理器的设计与实现

目前,在嵌入式产品的研发中,低档微处理器软件多采用裸机开发模式实现。在这种开发模式中,常有如下需求: (1)在经历特定的时间段后,执行特定操作; (2)根据给定周期执行特定操作。 传统的作法是利用前后台方式:设定硬件定时器,使其在后台以特定周期对各相关操作的标志变量作计数操作;前台则不断对各标志变量巡回查询,若发现标志变量达到预定值,则执行特定操作。可见,上述需求需直接操作硬件定时器实现,其过程繁琐,且需要用户对相关硬件有深入了解。因此,本文设计、实现了一种使用方便的低端系统时钟管理器。 本时钟管理器适用于可提供至少一个硬件定时器的处理器。其为用户提供了有益、友好的裁剪途径,以满足不同目标系统的实际需要。通过裁剪,

[单片机]

金风科技与英飞凌签署变流器模块技术引进协议

英飞凌科技股份有限公司与中国风电设备研发和制造企业 - 新疆金风科技股份有限公司,今日签署了一份核心模块技术引进协议。金风科技获权在国内生产兆瓦级风力发电机组变流器所需的英飞凌模块。 此外,英飞凌将向金风科技供应自产所需的IGBT(Insulated Gate Bipolar Transistor,绝缘栅双极型晶体管)部件。这些半导体能够高效地将发电机的变频输出转换为适合相应地区电网的固定频率。 金风科技董事长武钢先生在签约仪式上表示:“该项技术引进及后续自产将有效确保变流器核心模块的即时供应并获取显著成本效益,进而增进金风科技更好服务客户的能力。另外,我们还能够从中学习到以英飞凌为代表的先进德国生产工艺和质

[电源管理]

基于CPLD的双口模块设计

摘要:文章介绍了设计Multibus双口模块的方法。通过采用CPLD技术来实现模块内部逻辑,简化了模块的逻辑电路设计,提高了整个模块的稳定性和可靠性。达到了优化传统Multibus总线模块采用逻辑门电路和触发器来实现内部逻辑的目的。 关键词:Multibus总线;复杂可编程逻辑器件;双口RAM 0 引言 Multibus总线自1974年INTEL公司推出以来,以其自身支持集中式并行多处理、可靠性、抗干扰能力强等特点被广泛应用于工业控制领域和国防建设领域。但随着电子计算机技术的飞速发展,电子器件自身工艺、信号完整性等各方面不断提高,早期设计的Multibus总线模块通过逻辑门电路和触发器来实现内部逻辑的方法显然已经不

[嵌入式]

通讯手持设备的参考时钟设计

在通讯手持设备当中,参考时钟的贡献就像心脏对人体的作用一样,丝毫的差异都将导致系统功能的紊乱。之所以定义它为参考,是因为这类产品能否正常工作完全依赖于该时钟的精确度;而且一旦有误差存在,该误差就会随着倍频的增加而介入应用端的工作频段,无论是基带的数字和模拟部分还是射频的上变频和下变频都会受到影响。通常参考时钟所采用的中心频点都在10MHz ~ 30MHz,而且目前大多数都采用13MHz,20MHz,或26MHz,尤其是当射频和基带共用参考时钟时以13MHz和26MHz最多。 为什么要采用13MHz和26MHz作为参考时钟呢?客观上对射频RF而言,目前手持设备话务通信的频率资源主要集中在以1GHz和2GHz为中心的频率范围,从抗干

[单片机]

D3 Engineering推出毫米波雷达传感器模块

D3 Engineering宣布推出DesignCore RS-6843AOPUA mmWave雷达传感器,这是一款符合AEC Q-100要求的60 GHz雷达产品,集成了Texas Instruments C674x DSP,Arm Cortex-R4F MCU,雷达加速器和封装天线阵列。RF前端集成了一个PLL,三个发射器,四个接收器和基带ADC,并允许传感器在12 dBm的发射功率下覆盖高达4 GHz的频率,并且噪声特性大于15 dB。 该传感器模块可直接用于量产,具有散热金属主体和安装凸耳。可以通过USB接口对其进行测试和评估,并与PC或嵌入式开发平台一起使用。 该传感器有两个版本: RS-6843AOPA –

[传感器]

M37906微处理器和IPM模块在变频调速中的应用

摘要: 介绍了日本三菱公司最新推出的单片微处理器M37906和智能功率模块PS2124在变频调速中的应用,并结合不对称规则采样脉宽调制(PWM)法,给出了变频器设计的基本方法。

关键词: M37906 脉宽调制 智能功率模块 规则采样

随着电力电子技术和微电子技术的飞速发展,变频调速技术也在日新月异地进步。智能微控制器的不断完善和智能功率模块(IPM)的更新换代更加促进了变频调速技术的进步。近十多年来,以半导体功率器件为基础的PWM变频及脉宽调速技术在各个领域得到了广泛的应用。如何在普通环境中应用最新的电子技术成果,通过优化PWM算法提高控制性能,一直是技术人员的不懈追求。

本文介绍三菱公司

[传感技术]

工程师笔记|DFSDM 时钟配置问题

1.引言 DFSDM 全称为 Digital filter for sigma delta modulators。顾名思义,其作用主要是对外部 Σ∆调制的数字信号进行滤波。STM32L462xx 系列支持最多 4 个外部串行通道,2 个数字滤波器,最大可达到 24bit 的 ADC 分辨率。并且支持 SPI 接口和曼切斯特编码 1-wire接口。 2.问题分析 客户使用 STM32L462xx 的 DFSDM 连接数字麦克风,将麦克风的 PDM 信号转化为 PCM 信号,并采集数据。使用的参数为 16KHz 采样,2M 左右的时钟驱动数字麦克风,能够正常读取麦克风数据。了解到他们所使用的数字麦克风可以使用 768K 时钟驱动,从而

[单片机]

华为高管科普了7680帧超高速摄影

在华为Mate30系列发布会上,官方宣称该系列其中的一款Mate30 Pro支持7680帧超高速摄影,这个功能让很多消费者叹为观止,那该系列是怎么做到支持7680帧超高速摄影的呢?华为手机产品线副总裁李小龙在微博上做了一番科普。 李小龙说为了实现7680帧超高速摄影这个功能,主要是因为Mate30 Pro这三方面能力的增强:1,定制的这颗电影摄像头支持超高速的数据读写和传输能力,最高能实现HD1920帧/秒的数据输出,这是目前业界最强的硬件能力;2,摄像头和麒麟990之间能支持超高速的数据传输,能将大量的数据传输给麒麟990进行实时处理;3,麒麟990内置的新一代的ISP能够支持超

[手机便携]

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉)

ICCV2023论文汇总:Efficient and Scalable Vision(高效和可扩展视觉) GB/T 18655-2008 车辆、船和内燃机-无线电骚扰特性-用于 保护车载接收机的限值和测量方法

GB/T 18655-2008 车辆、船和内燃机-无线电骚扰特性-用于 保护车载接收机的限值和测量方法 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号