摘要:介绍了NESSIE标准中的分组密码算法——Camellia算法的加、解密过程,并对其在各种软、硬件平台上的性能进行了比较,结果表明Camellia算法在各种平台上均有着较高的效率。Camellia算法与其它技术相结合将在信息安全领域产生更广泛的应用。

关键词:NESSIE 分组密码 Camellia 算法 加密

继2000年10月美国推出二十一世纪高级数据加密标准AES后,2003年2月欧洲最新一代的安全标准NESSIE(New European Schemes for Signatures、Integrity and Encryption)出台。NESSIE是欧洲IST(Information Society Technologies)委员会计划的一个项目。Camellia算法以其在各种软件和硬件平台上的高效率这一显著特点成为NESSIE标准中两个128比特分组密码算法之一(另一个为美国的AES算法)。

Camellia算法由NTT和Mitsubishi Electric Corporation联合开发。作为欧洲新一代的加密标准,它具有较强的安全性,能够抵抗差分和线性密码分析等已知的攻击。与AES算法相比,Camellia算法在各种软硬件平台上表现出与之相当的加密速度。除了在各种软件和硬件平台上的高效性这一显著特点,它的另外一个特点是针对小规模硬件平台的设计。整个算法的硬件执行过程包括加密、解密和密钥扩展三部分,只需占用8.12K 0.18μm COMS工艺ASIC的库门逻辑。这在现有128比特分组密码中是最小的。

1 Camellia算法的组成

Camellia算法支持128比特的分组长度,128、192和256比特的密钥与AES的接口相同。本文以128比特密钥为例对Camellia算法进行详细介绍。

Camellia算法128比特密钥的加、解密过程共有18轮,采用Feistel结构,加、解密过程完全相同,只是子密钥注入顺序相反。而且密钥扩展过程和加、解密过程使用相同的部件。这使得Camellia算法不论是在软件平台还是硬件平台只需更小的规模和更小的存储即可。

(1)Camellia算法所采用的符号列表及其含义

B 8比特向量 W 32比特向量

L 64比特向量 Q 128比特向量

xn 比特向量

xL 向量x的左半部分 xR 向量x的右半部分

<<< 比特循环左移 || 两个操作数的连接

比特的异或操作 x 比特位取补操作

∪ 比特位的或操作 ∩ 比特位的与操作

(2)Camellia算法所采用的变量列表及其含义

M128 128比特明文组 C128 128比特密文组

K 主密钥 kwt64 ku64 klv64

子密钥

(3)Camellia算法所采用的变换函数

%26;#183;F变换

F变换(见式(1))是Camellia算法中最主要的部件之一,而且F变换被加、解密过程和密钥扩展过程所共用(128比特密钥的加、解密各用18次,密钥扩展用4次)。Camellia算法的F变换在设计时采用1轮的SPN(Substitution Permutation Network),包括一个P变换(线性)和一个S变换(非线性)。在Feistel型密码使用一轮SPN作轮函数时,对更高阶的差分和线性特性概率的理论评估变得更加复杂,在相同安全水平下的运行速度有所提高。

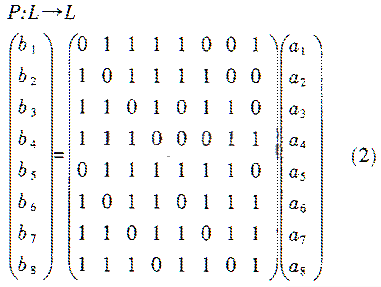

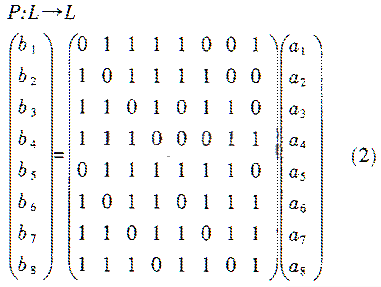

%26;#183;P变换

Camellia算法的P变换(见式(2))是一个线性变换。为了通信中软、硬件实现的高效性,它适合采用异或运算,并且其安全性能足以抵抗差分和线性密码分析。其在32位处理器、高端智能卡上的应用,跟在8位处理器上一样。

%26;#183;P变换

Camellia算法的P变换(见式(2))是一个线性变换。为了通信中软、硬件实现的高效性,它适合采用异或运算,并且其安全性能足以抵抗差分和线性密码分析。其在32位处理器、高端智能卡上的应用,跟在8位处理器上一样。

%26;#183;S变换

Camellia算法采用的S盒(见式(3))是一个GF(28)上的可逆变换,它加强了算法的安全性并且适用于小硬件设计。众所周知,GF(28)上函数的最大差分概率的最小值被证明为2-6,最大线性概率的最小值推测为2-6。Camellia算法选择GF(28)上能够获得最好的差分和线性概率的可逆函数作S盒,而且S盒每个输出比特具有高阶布尔多项式,使得对Camellia进行高阶差分攻击是困难的。S盒在GF(28)上输入、输出相关函数上的复杂表达式,使得插入攻击对Camellia无效。

S:L→L

(l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8)→

*s1(l"1(8)),s2(l"2(8)),s3(l"3(8)),s4("4(8)),s2(l"5(8)),s3(l"6(8)),

s4(l"7(8),s1(l"8(l8(8)))

其中, s2:y(8)=s1(x(8))=h(g(f(0xC5+x(8))))+0x6E

s2:Y(8)=s2(x(8))=s1(x(8))<<<1 (3)

s3:y(8)=s3(x(8))=s1(x(8))>>>1

s4:y(8)=s4(x(8))=s1(x(8))<<<1

算法中构造了四个不同的S盒,提高了Camellia算法抵抗阶段差分攻击的安全性。为了在小硬件上设计实现,GF(28)上的元素可以表示成系数为GF(24)上的多项式。这样,在实现S盒时,只需运用子域GF(24)上很少的操作。s1变换中所采用的f、h、g函数分别如(4)、(5)、(6)式所示。

%26;#183;S变换

Camellia算法采用的S盒(见式(3))是一个GF(28)上的可逆变换,它加强了算法的安全性并且适用于小硬件设计。众所周知,GF(28)上函数的最大差分概率的最小值被证明为2-6,最大线性概率的最小值推测为2-6。Camellia算法选择GF(28)上能够获得最好的差分和线性概率的可逆函数作S盒,而且S盒每个输出比特具有高阶布尔多项式,使得对Camellia进行高阶差分攻击是困难的。S盒在GF(28)上输入、输出相关函数上的复杂表达式,使得插入攻击对Camellia无效。

S:L→L

(l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8)→

*s1(l"1(8)),s2(l"2(8)),s3(l"3(8)),s4("4(8)),s2(l"5(8)),s3(l"6(8)),

s4(l"7(8),s1(l"8(l8(8)))

其中, s2:y(8)=s1(x(8))=h(g(f(0xC5+x(8))))+0x6E

s2:Y(8)=s2(x(8))=s1(x(8))<<<1 (3)

s3:y(8)=s3(x(8))=s1(x(8))>>>1

s4:y(8)=s4(x(8))=s1(x(8))<<<1

算法中构造了四个不同的S盒,提高了Camellia算法抵抗阶段差分攻击的安全性。为了在小硬件上设计实现,GF(28)上的元素可以表示成系数为GF(24)上的多项式。这样,在实现S盒时,只需运用子域GF(24)上很少的操作。s1变换中所采用的f、h、g函数分别如(4)、(5)、(6)式所示。

(b1,b2,b3,b4,b5,b6,b7,b8)=g(a1,a2,a3,a4,a5,a6,a7,a8)

其中,(b8+b7α+b6α2+b5α3)+(b4+b3α+b2α2+b1α3)β

=1/((a8+a7α+a6α2+a5α3)+(a4+a3α+a2α2+a1α3))(6)

规定(6)式中GF(2的8次方)上运算=1/0,β是GF(2的8次方)上方程x8+x6+x5+x3+1=0的根,a=β238=β6+β5+β3+β2是GF(2的4次方)上方程x4+x+1=0的根。当然根据性能要求,在具体实现加密算法时,S盒的实现电路也可以直接查表的方式进行。

%26;#183;FL/FL-1变换

Camellia算法每六圈加入一次FL/FL-1变换,用来打乱整个算法的规律性。加入FL/FL-1变换的另一个好处是可以抵抗未知的密码攻击方法,而且加入FL/FL-1变换并不影响Feistel结构加、解密过程相同。

(b1,b2,b3,b4,b5,b6,b7,b8)=g(a1,a2,a3,a4,a5,a6,a7,a8)

其中,(b8+b7α+b6α2+b5α3)+(b4+b3α+b2α2+b1α3)β

=1/((a8+a7α+a6α2+a5α3)+(a4+a3α+a2α2+a1α3))(6)

规定(6)式中GF(2的8次方)上运算=1/0,β是GF(2的8次方)上方程x8+x6+x5+x3+1=0的根,a=β238=β6+β5+β3+β2是GF(2的4次方)上方程x4+x+1=0的根。当然根据性能要求,在具体实现加密算法时,S盒的实现电路也可以直接查表的方式进行。

%26;#183;FL/FL-1变换

Camellia算法每六圈加入一次FL/FL-1变换,用来打乱整个算法的规律性。加入FL/FL-1变换的另一个好处是可以抵抗未知的密码攻击方法,而且加入FL/FL-1变换并不影响Feistel结构加、解密过程相同。

FL:L%26;#215;L→L

(XL(32)||XR(32),klL(32)||klR(32)→(7)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

FL-1:L%26;#215;L→L

(YL(32)||YR(32),klL(32)||klR(32)→ (8)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

2 Camellia算法的加、解密及密钥扩展实现过程

(1)加、解密过程

Camellia算法的整个加密过程有18轮Feistel结构,在第6轮和第12轮之后加入了FL/FL-1变换层,用来打乱算法的规律性,并且在第1轮之前和最后1轮之后使用了128比特的异或操作。解密过程与加密过程完全相同,只是圈密钥注入顺序与加密相反。128比特密钥Camellia算法的加密过程如图1所示。

FL:L%26;#215;L→L

(XL(32)||XR(32),klL(32)||klR(32)→(7)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

FL-1:L%26;#215;L→L

(YL(32)||YR(32),klL(32)||klR(32)→ (8)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

2 Camellia算法的加、解密及密钥扩展实现过程

(1)加、解密过程

Camellia算法的整个加密过程有18轮Feistel结构,在第6轮和第12轮之后加入了FL/FL-1变换层,用来打乱算法的规律性,并且在第1轮之前和最后1轮之后使用了128比特的异或操作。解密过程与加密过程完全相同,只是圈密钥注入顺序与加密相反。128比特密钥Camellia算法的加密过程如图1所示。

(2)密钥扩展

Camellia算法的密钥扩展遵循了严格的设计准则,如实现简单且与加、解密过程共用部件,密钥配置时间小于加密时间,支持在线密钥生成,没有等效密钥,能够抵抗相关密钥攻击和滑动攻击等。整个过程只需通过三个中间变量,KL(128)=K(128),K(128)=0KA的简单移位即可得到子密钥kwt(64)(t=1,…,4),ku(64)(u=1,…,18)和klv(64)(v=1,…,4),且中间生成过程与加密过程共用了部件F(如图1、2所示)。

3 Camellia算法的安全性

设计者用差分扩散概率和线性相关概率的保守上界证明了任何含SPN网络的十六圈Camellia密码对差分密码分析和线性密码分析都是安全的;此外,通过对活动S盒的计数说明十二圈Camellia中没有概率大于2-128的差分特征和线性特征;带或不带FL层的十圈Camellia都具有伪随机置换特性,能够抵抗截断差分攻击和线性密码分析;设计者还声称Camellia能够抵抗不可能差分攻击、Boomerang攻击、高阶差分攻击、相关密钥攻击、插入攻击、Slide攻击、线性和攻击及Square攻击。在密钥的安全性上,一方面不存在等效密钥;另一方面,子密钥来自主密钥的加密结果KA和KB,改变主密钥并不能获得预想的KA和KB,反之亦然,因而无法控制和预测子密钥之间的关系,从而相关密钥攻击难以成功。由于密钥长度不少于128比特,以当前的计算能力还无法对Camellia成功实施诸如密钥穷举搜索攻击、时间存储权衡攻击、字典攻击和密钥匹配等类型的强力攻击。

4 Camellia算法在各种平台上的性能比较

评测一个分组密码的好坏,除了要求其具有高的安全性外,还要求算法在应用平台上实现简单。Camellia算法在设计时充分考虑到了这一点,下面给出其在各种平台上的性能参数。评测算法在软件平台上实现性能时,首要考虑其速度,其次还要看算法实现时所需的存储空间,表1前半部分给出了Camellia算法在常用的32位处理器上各种软件平台的实现性能。高的加密速度和低的存储需求,表明Camellia算法可以有效地应用于各种软件系统中。从表1后半部分可以看出Camellia算法在高端和低端的智能卡平台上同样有着良好的性能;由于Camellia算法的密钥扩展与加、解密过程有共用部分,所以其硬件平台所需的芯片面积大大减少,降低了硬件成本,便于推广应用,详细参数见表2。

表1 Camellia算法在软件和智能卡平台上的性能

环 境

语 言

速度加、解密

RAM合计

ROM合计

PIII700MHz128MB256 L2-cache

Assembly

241.5Mbps

64bytes

11420bytes

PII300MHz160MB512 L2-cache

VC++6

66.6Mbps

108bytes

9461bytes

PIII 1GHz512MB256 L2-cache

Java

161.4Mbps

\

\

Intel 8051 12MHz

Assembly

10217

10.22msec

32bytes

990bytes

Z80 5MHz

Assembly

35951

7.19msec

106bytes

1698bytes

MC68HC705 B16 2.1MHz

Assembly

9900

4.71msec

208bytes

\

表2 Camellia算法在硬件平台上的性能

环 境

设计Lab

速度

芯片面积

加、解密

单元

合计

ASIC

Unrolled

Mitsubishi0.18μm

2785.00Mbps

Kgate

244.90

Loop

Mitsubishi0.18μm

1881.25Mbps

Kgate

44.30

FPGA

Unrolled

Xilinx VirtexE

401.89Mbps

Slice

9426

Loop

Xilinx VirtexE

227.42Mbps

Slice

1780

从本文可以看出,分组密码加密算法发展到今天,不论是从安全性还是从实用性的角度都越来越强。NESSIE标准中的Camellia加密算法充分考虑到了各种因素,既保证了算法的安全性又考虑到其在各种平台上的实现效率,尤其是针对小硬件的设计思想,使其有着广泛的应用前景。

(2)密钥扩展

Camellia算法的密钥扩展遵循了严格的设计准则,如实现简单且与加、解密过程共用部件,密钥配置时间小于加密时间,支持在线密钥生成,没有等效密钥,能够抵抗相关密钥攻击和滑动攻击等。整个过程只需通过三个中间变量,KL(128)=K(128),K(128)=0KA的简单移位即可得到子密钥kwt(64)(t=1,…,4),ku(64)(u=1,…,18)和klv(64)(v=1,…,4),且中间生成过程与加密过程共用了部件F(如图1、2所示)。

3 Camellia算法的安全性

设计者用差分扩散概率和线性相关概率的保守上界证明了任何含SPN网络的十六圈Camellia密码对差分密码分析和线性密码分析都是安全的;此外,通过对活动S盒的计数说明十二圈Camellia中没有概率大于2-128的差分特征和线性特征;带或不带FL层的十圈Camellia都具有伪随机置换特性,能够抵抗截断差分攻击和线性密码分析;设计者还声称Camellia能够抵抗不可能差分攻击、Boomerang攻击、高阶差分攻击、相关密钥攻击、插入攻击、Slide攻击、线性和攻击及Square攻击。在密钥的安全性上,一方面不存在等效密钥;另一方面,子密钥来自主密钥的加密结果KA和KB,改变主密钥并不能获得预想的KA和KB,反之亦然,因而无法控制和预测子密钥之间的关系,从而相关密钥攻击难以成功。由于密钥长度不少于128比特,以当前的计算能力还无法对Camellia成功实施诸如密钥穷举搜索攻击、时间存储权衡攻击、字典攻击和密钥匹配等类型的强力攻击。

4 Camellia算法在各种平台上的性能比较

评测一个分组密码的好坏,除了要求其具有高的安全性外,还要求算法在应用平台上实现简单。Camellia算法在设计时充分考虑到了这一点,下面给出其在各种平台上的性能参数。评测算法在软件平台上实现性能时,首要考虑其速度,其次还要看算法实现时所需的存储空间,表1前半部分给出了Camellia算法在常用的32位处理器上各种软件平台的实现性能。高的加密速度和低的存储需求,表明Camellia算法可以有效地应用于各种软件系统中。从表1后半部分可以看出Camellia算法在高端和低端的智能卡平台上同样有着良好的性能;由于Camellia算法的密钥扩展与加、解密过程有共用部分,所以其硬件平台所需的芯片面积大大减少,降低了硬件成本,便于推广应用,详细参数见表2。

表1 Camellia算法在软件和智能卡平台上的性能

环 境

语 言

速度加、解密

RAM合计

ROM合计

PIII700MHz128MB256 L2-cache

Assembly

241.5Mbps

64bytes

11420bytes

PII300MHz160MB512 L2-cache

VC++6

66.6Mbps

108bytes

9461bytes

PIII 1GHz512MB256 L2-cache

Java

161.4Mbps

\

\

Intel 8051 12MHz

Assembly

10217

10.22msec

32bytes

990bytes

Z80 5MHz

Assembly

35951

7.19msec

106bytes

1698bytes

MC68HC705 B16 2.1MHz

Assembly

9900

4.71msec

208bytes

\

表2 Camellia算法在硬件平台上的性能

环 境

设计Lab

速度

芯片面积

加、解密

单元

合计

ASIC

Unrolled

Mitsubishi0.18μm

2785.00Mbps

Kgate

244.90

Loop

Mitsubishi0.18μm

1881.25Mbps

Kgate

44.30

FPGA

Unrolled

Xilinx VirtexE

401.89Mbps

Slice

9426

Loop

Xilinx VirtexE

227.42Mbps

Slice

1780

从本文可以看出,分组密码加密算法发展到今天,不论是从安全性还是从实用性的角度都越来越强。NESSIE标准中的Camellia加密算法充分考虑到了各种因素,既保证了算法的安全性又考虑到其在各种平台上的实现效率,尤其是针对小硬件的设计思想,使其有着广泛的应用前景。

引用地址:一种新的实用安全加密标准算法——Camellia算法

%26;#183;P变换

Camellia算法的P变换(见式(2))是一个线性变换。为了通信中软、硬件实现的高效性,它适合采用异或运算,并且其安全性能足以抵抗差分和线性密码分析。其在32位处理器、高端智能卡上的应用,跟在8位处理器上一样。

%26;#183;P变换

Camellia算法的P变换(见式(2))是一个线性变换。为了通信中软、硬件实现的高效性,它适合采用异或运算,并且其安全性能足以抵抗差分和线性密码分析。其在32位处理器、高端智能卡上的应用,跟在8位处理器上一样。

%26;#183;S变换

Camellia算法采用的S盒(见式(3))是一个GF(28)上的可逆变换,它加强了算法的安全性并且适用于小硬件设计。众所周知,GF(28)上函数的最大差分概率的最小值被证明为2-6,最大线性概率的最小值推测为2-6。Camellia算法选择GF(28)上能够获得最好的差分和线性概率的可逆函数作S盒,而且S盒每个输出比特具有高阶布尔多项式,使得对Camellia进行高阶差分攻击是困难的。S盒在GF(28)上输入、输出相关函数上的复杂表达式,使得插入攻击对Camellia无效。

S:L→L

(l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8)→

*s1(l"1(8)),s2(l"2(8)),s3(l"3(8)),s4("4(8)),s2(l"5(8)),s3(l"6(8)),

s4(l"7(8),s1(l"8(l8(8)))

其中, s2:y(8)=s1(x(8))=h(g(f(0xC5+x(8))))+0x6E

s2:Y(8)=s2(x(8))=s1(x(8))<<<1 (3)

s3:y(8)=s3(x(8))=s1(x(8))>>>1

s4:y(8)=s4(x(8))=s1(x(8))<<<1

算法中构造了四个不同的S盒,提高了Camellia算法抵抗阶段差分攻击的安全性。为了在小硬件上设计实现,GF(28)上的元素可以表示成系数为GF(24)上的多项式。这样,在实现S盒时,只需运用子域GF(24)上很少的操作。s1变换中所采用的f、h、g函数分别如(4)、(5)、(6)式所示。

%26;#183;S变换

Camellia算法采用的S盒(见式(3))是一个GF(28)上的可逆变换,它加强了算法的安全性并且适用于小硬件设计。众所周知,GF(28)上函数的最大差分概率的最小值被证明为2-6,最大线性概率的最小值推测为2-6。Camellia算法选择GF(28)上能够获得最好的差分和线性概率的可逆函数作S盒,而且S盒每个输出比特具有高阶布尔多项式,使得对Camellia进行高阶差分攻击是困难的。S盒在GF(28)上输入、输出相关函数上的复杂表达式,使得插入攻击对Camellia无效。

S:L→L

(l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8),l"1(8)→

*s1(l"1(8)),s2(l"2(8)),s3(l"3(8)),s4("4(8)),s2(l"5(8)),s3(l"6(8)),

s4(l"7(8),s1(l"8(l8(8)))

其中, s2:y(8)=s1(x(8))=h(g(f(0xC5+x(8))))+0x6E

s2:Y(8)=s2(x(8))=s1(x(8))<<<1 (3)

s3:y(8)=s3(x(8))=s1(x(8))>>>1

s4:y(8)=s4(x(8))=s1(x(8))<<<1

算法中构造了四个不同的S盒,提高了Camellia算法抵抗阶段差分攻击的安全性。为了在小硬件上设计实现,GF(28)上的元素可以表示成系数为GF(24)上的多项式。这样,在实现S盒时,只需运用子域GF(24)上很少的操作。s1变换中所采用的f、h、g函数分别如(4)、(5)、(6)式所示。

(b1,b2,b3,b4,b5,b6,b7,b8)=g(a1,a2,a3,a4,a5,a6,a7,a8)

其中,(b8+b7α+b6α2+b5α3)+(b4+b3α+b2α2+b1α3)β

=1/((a8+a7α+a6α2+a5α3)+(a4+a3α+a2α2+a1α3))(6)

规定(6)式中GF(2的8次方)上运算=1/0,β是GF(2的8次方)上方程x8+x6+x5+x3+1=0的根,a=β238=β6+β5+β3+β2是GF(2的4次方)上方程x4+x+1=0的根。当然根据性能要求,在具体实现加密算法时,S盒的实现电路也可以直接查表的方式进行。

%26;#183;FL/FL-1变换

Camellia算法每六圈加入一次FL/FL-1变换,用来打乱整个算法的规律性。加入FL/FL-1变换的另一个好处是可以抵抗未知的密码攻击方法,而且加入FL/FL-1变换并不影响Feistel结构加、解密过程相同。

(b1,b2,b3,b4,b5,b6,b7,b8)=g(a1,a2,a3,a4,a5,a6,a7,a8)

其中,(b8+b7α+b6α2+b5α3)+(b4+b3α+b2α2+b1α3)β

=1/((a8+a7α+a6α2+a5α3)+(a4+a3α+a2α2+a1α3))(6)

规定(6)式中GF(2的8次方)上运算=1/0,β是GF(2的8次方)上方程x8+x6+x5+x3+1=0的根,a=β238=β6+β5+β3+β2是GF(2的4次方)上方程x4+x+1=0的根。当然根据性能要求,在具体实现加密算法时,S盒的实现电路也可以直接查表的方式进行。

%26;#183;FL/FL-1变换

Camellia算法每六圈加入一次FL/FL-1变换,用来打乱整个算法的规律性。加入FL/FL-1变换的另一个好处是可以抵抗未知的密码攻击方法,而且加入FL/FL-1变换并不影响Feistel结构加、解密过程相同。

FL:L%26;#215;L→L

(XL(32)||XR(32),klL(32)||klR(32)→(7)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

FL-1:L%26;#215;L→L

(YL(32)||YR(32),klL(32)||klR(32)→ (8)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

2 Camellia算法的加、解密及密钥扩展实现过程

(1)加、解密过程

Camellia算法的整个加密过程有18轮Feistel结构,在第6轮和第12轮之后加入了FL/FL-1变换层,用来打乱算法的规律性,并且在第1轮之前和最后1轮之后使用了128比特的异或操作。解密过程与加密过程完全相同,只是圈密钥注入顺序与加密相反。128比特密钥Camellia算法的加密过程如图1所示。

FL:L%26;#215;L→L

(XL(32)||XR(32),klL(32)||klR(32)→(7)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

FL-1:L%26;#215;L→L

(YL(32)||YR(32),klL(32)||klR(32)→ (8)

(YR(32)∪klR(32),YL(32)||((XL(32)∩klL(32)<<<1)+YR(32)

2 Camellia算法的加、解密及密钥扩展实现过程

(1)加、解密过程

Camellia算法的整个加密过程有18轮Feistel结构,在第6轮和第12轮之后加入了FL/FL-1变换层,用来打乱算法的规律性,并且在第1轮之前和最后1轮之后使用了128比特的异或操作。解密过程与加密过程完全相同,只是圈密钥注入顺序与加密相反。128比特密钥Camellia算法的加密过程如图1所示。

(2)密钥扩展

Camellia算法的密钥扩展遵循了严格的设计准则,如实现简单且与加、解密过程共用部件,密钥配置时间小于加密时间,支持在线密钥生成,没有等效密钥,能够抵抗相关密钥攻击和滑动攻击等。整个过程只需通过三个中间变量,KL(128)=K(128),K(128)=0KA的简单移位即可得到子密钥kwt(64)(t=1,…,4),ku(64)(u=1,…,18)和klv(64)(v=1,…,4),且中间生成过程与加密过程共用了部件F(如图1、2所示)。

3 Camellia算法的安全性

设计者用差分扩散概率和线性相关概率的保守上界证明了任何含SPN网络的十六圈Camellia密码对差分密码分析和线性密码分析都是安全的;此外,通过对活动S盒的计数说明十二圈Camellia中没有概率大于2-128的差分特征和线性特征;带或不带FL层的十圈Camellia都具有伪随机置换特性,能够抵抗截断差分攻击和线性密码分析;设计者还声称Camellia能够抵抗不可能差分攻击、Boomerang攻击、高阶差分攻击、相关密钥攻击、插入攻击、Slide攻击、线性和攻击及Square攻击。在密钥的安全性上,一方面不存在等效密钥;另一方面,子密钥来自主密钥的加密结果KA和KB,改变主密钥并不能获得预想的KA和KB,反之亦然,因而无法控制和预测子密钥之间的关系,从而相关密钥攻击难以成功。由于密钥长度不少于128比特,以当前的计算能力还无法对Camellia成功实施诸如密钥穷举搜索攻击、时间存储权衡攻击、字典攻击和密钥匹配等类型的强力攻击。

4 Camellia算法在各种平台上的性能比较

评测一个分组密码的好坏,除了要求其具有高的安全性外,还要求算法在应用平台上实现简单。Camellia算法在设计时充分考虑到了这一点,下面给出其在各种平台上的性能参数。评测算法在软件平台上实现性能时,首要考虑其速度,其次还要看算法实现时所需的存储空间,表1前半部分给出了Camellia算法在常用的32位处理器上各种软件平台的实现性能。高的加密速度和低的存储需求,表明Camellia算法可以有效地应用于各种软件系统中。从表1后半部分可以看出Camellia算法在高端和低端的智能卡平台上同样有着良好的性能;由于Camellia算法的密钥扩展与加、解密过程有共用部分,所以其硬件平台所需的芯片面积大大减少,降低了硬件成本,便于推广应用,详细参数见表2。

表1 Camellia算法在软件和智能卡平台上的性能

环 境

语 言

速度加、解密

RAM合计

ROM合计

PIII700MHz128MB256 L2-cache

Assembly

241.5Mbps

64bytes

11420bytes

PII300MHz160MB512 L2-cache

VC++6

66.6Mbps

108bytes

9461bytes

PIII 1GHz512MB256 L2-cache

Java

161.4Mbps

\

\

Intel 8051 12MHz

Assembly

10217

10.22msec

32bytes

990bytes

Z80 5MHz

Assembly

35951

7.19msec

106bytes

1698bytes

MC68HC705 B16 2.1MHz

Assembly

9900

4.71msec

208bytes

\

表2 Camellia算法在硬件平台上的性能

环 境

设计Lab

速度

芯片面积

加、解密

单元

合计

ASIC

Unrolled

Mitsubishi0.18μm

2785.00Mbps

Kgate

244.90

Loop

Mitsubishi0.18μm

1881.25Mbps

Kgate

44.30

FPGA

Unrolled

Xilinx VirtexE

401.89Mbps

Slice

9426

Loop

Xilinx VirtexE

227.42Mbps

Slice

1780

从本文可以看出,分组密码加密算法发展到今天,不论是从安全性还是从实用性的角度都越来越强。NESSIE标准中的Camellia加密算法充分考虑到了各种因素,既保证了算法的安全性又考虑到其在各种平台上的实现效率,尤其是针对小硬件的设计思想,使其有着广泛的应用前景。

(2)密钥扩展

Camellia算法的密钥扩展遵循了严格的设计准则,如实现简单且与加、解密过程共用部件,密钥配置时间小于加密时间,支持在线密钥生成,没有等效密钥,能够抵抗相关密钥攻击和滑动攻击等。整个过程只需通过三个中间变量,KL(128)=K(128),K(128)=0KA的简单移位即可得到子密钥kwt(64)(t=1,…,4),ku(64)(u=1,…,18)和klv(64)(v=1,…,4),且中间生成过程与加密过程共用了部件F(如图1、2所示)。

3 Camellia算法的安全性

设计者用差分扩散概率和线性相关概率的保守上界证明了任何含SPN网络的十六圈Camellia密码对差分密码分析和线性密码分析都是安全的;此外,通过对活动S盒的计数说明十二圈Camellia中没有概率大于2-128的差分特征和线性特征;带或不带FL层的十圈Camellia都具有伪随机置换特性,能够抵抗截断差分攻击和线性密码分析;设计者还声称Camellia能够抵抗不可能差分攻击、Boomerang攻击、高阶差分攻击、相关密钥攻击、插入攻击、Slide攻击、线性和攻击及Square攻击。在密钥的安全性上,一方面不存在等效密钥;另一方面,子密钥来自主密钥的加密结果KA和KB,改变主密钥并不能获得预想的KA和KB,反之亦然,因而无法控制和预测子密钥之间的关系,从而相关密钥攻击难以成功。由于密钥长度不少于128比特,以当前的计算能力还无法对Camellia成功实施诸如密钥穷举搜索攻击、时间存储权衡攻击、字典攻击和密钥匹配等类型的强力攻击。

4 Camellia算法在各种平台上的性能比较

评测一个分组密码的好坏,除了要求其具有高的安全性外,还要求算法在应用平台上实现简单。Camellia算法在设计时充分考虑到了这一点,下面给出其在各种平台上的性能参数。评测算法在软件平台上实现性能时,首要考虑其速度,其次还要看算法实现时所需的存储空间,表1前半部分给出了Camellia算法在常用的32位处理器上各种软件平台的实现性能。高的加密速度和低的存储需求,表明Camellia算法可以有效地应用于各种软件系统中。从表1后半部分可以看出Camellia算法在高端和低端的智能卡平台上同样有着良好的性能;由于Camellia算法的密钥扩展与加、解密过程有共用部分,所以其硬件平台所需的芯片面积大大减少,降低了硬件成本,便于推广应用,详细参数见表2。

表1 Camellia算法在软件和智能卡平台上的性能

环 境

语 言

速度加、解密

RAM合计

ROM合计

PIII700MHz128MB256 L2-cache

Assembly

241.5Mbps

64bytes

11420bytes

PII300MHz160MB512 L2-cache

VC++6

66.6Mbps

108bytes

9461bytes

PIII 1GHz512MB256 L2-cache

Java

161.4Mbps

\

\

Intel 8051 12MHz

Assembly

10217

10.22msec

32bytes

990bytes

Z80 5MHz

Assembly

35951

7.19msec

106bytes

1698bytes

MC68HC705 B16 2.1MHz

Assembly

9900

4.71msec

208bytes

\

表2 Camellia算法在硬件平台上的性能

环 境

设计Lab

速度

芯片面积

加、解密

单元

合计

ASIC

Unrolled

Mitsubishi0.18μm

2785.00Mbps

Kgate

244.90

Loop

Mitsubishi0.18μm

1881.25Mbps

Kgate

44.30

FPGA

Unrolled

Xilinx VirtexE

401.89Mbps

Slice

9426

Loop

Xilinx VirtexE

227.42Mbps

Slice

1780

从本文可以看出,分组密码加密算法发展到今天,不论是从安全性还是从实用性的角度都越来越强。NESSIE标准中的Camellia加密算法充分考虑到了各种因素,既保证了算法的安全性又考虑到其在各种平台上的实现效率,尤其是针对小硬件的设计思想,使其有着广泛的应用前景。

上一篇:一种高速并行FFT处理器的VLSI结构设计

下一篇:在远程通信中实现89LPC932的ISP功能

- 热门资源推荐

- 热门放大器推荐

小广播

热门活动

换一批

更多

最新应用文章

更多精选电路图

更多热门文章

更多每日新闻

- Allegro MicroSystems 在 2024 年德国慕尼黑电子展上推出先进的磁性和电感式位置感测解决方案

- 左手车钥匙,右手活体检测雷达,UWB上车势在必行!

- 狂飙十年,国产CIS挤上牌桌

- 神盾短刀电池+雷神EM-i超级电混,吉利新能源甩出了两张“王炸”

- 浅谈功能安全之故障(fault),错误(error),失效(failure)

- 智能汽车2.0周期,这几大核心产业链迎来重大机会!

- 美日研发新型电池,宁德时代面临挑战?中国新能源电池产业如何应对?

- Rambus推出业界首款HBM 4控制器IP:背后有哪些技术细节?

- 村田推出高精度汽车用6轴惯性传感器

- 福特获得预充电报警专利 有助于节约成本和应对紧急情况

更多往期活动

11月17日历史上的今天

厂商技术中心

ALD1701ASAXXXX

ALD1701ASAXXXX

京公网安备 11010802033920号

京公网安备 11010802033920号