前言

随着数字化广播电视技术的迅速发展和基于MPEG-2标准的图像压缩和复用技术的完善,利用PC对大容量信息的处理变得日益重要,如基于PC的软复用器的实现,使得通过PC接收DVB(数字视频广播)码流已逐渐成为一项不可替代的多媒体数据接收技术。因此,设计基于PC平台的DVB 码流接收卡是数字广播电视发展的需要。

由于DVB-ASI信号的平均传输速率为270 Mbps,而DVB传输流又要求保证接收的实时性,因此本文选择了PCI总线。33MHz、32位的PCI总线的数据传输速率最高可达133MBps, 完全可以满足高速实时传输的需求。选择了Altera公司的PCI编译器软件包来实现PCI接口控制电路。该软件包为PCI接口提供了一个完整的解决办法,包含了PCI控制电路的所有功能。用户可以通过修改参数生成所需的IP核模块,以设计自己的外部设备接口逻辑。本文选择了其生成的PCI_MT32功能模块。

系统硬件模块设计

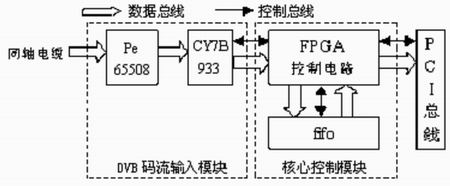

系统的硬件电路设计要求:能将传输速率为270 Mbps的串行DVB—ASI码流实时、无损地通过PCI接口传输到PC,以供PC上的应用程序做进一步处理。在操作和使用上要方便,在设计上要求结构紧凑、接口简单、性能可靠、易于升级。系统硬件框图如图1所示。

从图中可以看出,由于使用了FPGA及PCI IP核,使整个硬件电路显得特别简洁。它主要由DVB码流输入模块和核心控制模块组成。串行DVB传输流经同轴电缆进入DVB码流输入模块,转换为8位并行输出。核心控制模块对并行数据进行缓存,并采用DMA方式传输给PCI总线,完成本地总线和PCI总线的可靠通信。

DVB码流输入模块

本文选用ASI接口。ASI信号由同轴电缆经BNC接头输入,经过互感(用PE65508芯片)转换为PECL(正向发射极耦合逻辑)差分电平信号,再经过耦合电路,到达CY7B933的差分线输入端。 CY7B933是Cypress公司的一种用于点对点高速串行数据通信的接收芯片,它完成码流输入模块的核心功能。它有三种工作模式,这里选用它的解码模式对输入信号进行8B/10B解码和串并转换。最后输出经过字节对齐的8位并行TLL信号,输出的信号包括 MPEG-2传输流和作为同步字使用的逗号字符(在8B/10B传输码规则中定义为 K28.5专用字符),其输出速率恒定为27MBps。

图1 系统硬件框图

核心控制模块

核心控制模块由FPGA控制电路和异步FIFO组成。主要完成对输入ASI信号的缓存和对PCI总线信号的控制的功能。其中最主要的部分是FPGA控制电路。基于整个系统的性能的考虑,选择Altera公司的EP1C12。这款芯片有12060个逻辑单元,52个RAM块等资源,完全可以支持本设计的要求。

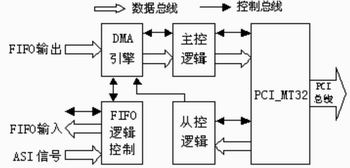

FPGA控制电路内部框图如图2所示,它是本设计的核心部分,对输入的ASI信号保留有效的DVB传输流,发送到FIFO输入端进行缓存。并将FIFO缓存后输出的数据用DMA传输方式通过PCI总线实现对PC内存的存取,同时利用FIFO的标志信号控制DMA传输过程。下面对FPGA控制电路的各模块进行介绍。

PCI_MT32功能模块

本文在选择PCI接口芯片时,选择了Altera公司的PCI 编译器软件包,它可以参数化地生成用于PCI接口的IP核----MegaCore。这个可编译和综合的MegaCore有以下4种宏功能模块:PCI_MT64、PCI_MT32、PCI_T64和PCI_T32。它们都可以完成总线协议的转换,将复杂的、电气和时序要求高的PCI总线逻辑转换为易于操作的本地接口逻辑,遵循PCI总线协议2.2版,经过严格的工业级验证并支持多款优化FPGA。其中,PCI_MT32是支持33/66MHz工作频率、32位PCI总线、支持主/从模式的PCI IP功能模块。考虑到市场的需求,通常的PC主板都支持32位PCI,且在主模式下DMA控制器才能工作,因此选择了PCI_MT32。 本地信号都以l (local)开头,其中以lt_开头的是从控信号,以lm_开头的是主控信号。

要使用PCI_MT32功能模块就要了解其配置寄存器,配置寄存器中的基址寄存器最为重要,PCI_MT32共提供了6个基址寄存器,可以映射6个存储器或I/O 空间。在操作系统启动前后,基址寄存器分别起到两个作用。在操作系统启动前,基址寄存器存放定义的空间长度。以使加电软件以确定在系统中有多少存储器以及系统中的 I/O 控制器要求多少地址空间,然后才可以把 I/O 控制器映射到合理的地址空间并引导系统。在操作系统启动后,基址寄存器又要起到存放基地址的作用,通过对要存取的基址寄存器用配置写操作写入基地址,再通过基地址加偏移量就可以访问想要存取的空间。

图2 FPGA控制电路内部框图

主控逻辑模块

当PCI_MT32作为PCI总线主设备进行主模式操作时,主控逻辑模块对PCI_MT32本地侧信号进行控制以执行PCI主模式写事务,将FIFO的数据传送给从设备。同时还为DMA引擎提供PCI总线所处的状态,如总线是否处于数据阶段,是否有从设备终止等。

模块的主要设计思路:当PCI总线仲裁器允许PCI_MT32成为总线主设备时,PCI_MT32功能模块在本地侧输出lm_adr_ackn信号,表明地址阶段开始,此时主控逻辑模块应在l_adi线提供PCI地址,并在l_cbeni线提供PCI命令。在接下来的数据阶段,如果本地侧数据已准备好,就使lm_rdyn(本地侧主设备准备好)信号有效,并在l_adi线提供数据,在l_cbeni线提供字节使能。如果从设备被选中且准备好,数据传输就开始了。最后,通过通知PCI总线当前周期是本地侧最后的数据阶段,在完成这次数据传输后就进入总线空闲状态,PCI_MT32不再是总线主设备,一次数据传输也就结束了。

从控逻辑模块

当PCI_MT32作为PCI总线从设备进行目标事务操作时,从控逻辑模块对PCI_MT32本地侧信号进行控制。PC通过读本地侧相应寄存器,了解当前状态,通过对相应DMA寄存器的写操作,来启动DMA引擎。由于对寄存器的读写只用到目标单周期事务,且大部分信号由主机控制,从控逻辑相对简单。主要是保证在要存取的目标地址命中,且frame信号有效时,trdyn(从设备准备好)信号有效。

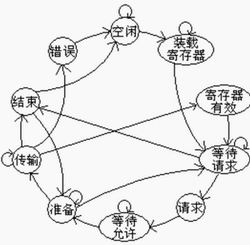

图3 DMA状态机流程图

DMA引擎模块

DMA引擎模块由DMA寄存器、DMA状态机等模块构成,当PCI_MT32作为PCI总线主设备进行主模式写操作时,它与主控逻辑模块共同将FIFO缓存输出的数据通过DMA操作发送到PCI_MT32本地信号侧。 其中,DMA寄存器的地址直接映射到PCI的地址空间,其基地址由PCI_MT32中的配置寄存器Bar0决定。主机通过访问这些寄存器来控制DMA操作。寄存器包括控制状态寄存器、PCI地址寄存器和中断状态寄存器。DMA状态机模块流程如图3所示。

以下对DMA状态机进行简要描述:状态机无数据传输时默认停留在空闲状态。当PC写控制状态寄存器中的启动位,就启动状态机,进入装载寄存器状态。自动装载PCI地址寄存器后进入等待请求状态。如果FIFO中的数据已经半满,进入请求状态申请占用PCI总线,接着进入等待允许状态,等待PCI设备获得总线的控制权。当PCI设备成为总线主设备,就进入准备状态。判断PCI总线的地址阶段结束将要进入数据阶段,则进入传输状态,进行数据传输。此时,如果从设备提出终止,则返回寄存器有效状态,根据情况重新申请总线的控制权;如果本次DMA数据传输结束或出现PCI异常中断、PCI系统错误、PCI奇偶校验错误、FIFO满等错误时,则分别进入结束状态或错误状态,写中断状态寄存器的相应位,同时发出中断信号。PC收到中断后,读中断状态寄存器确定中断类型,以进行下一步操作。最后返回空闲状态,并清除中断。

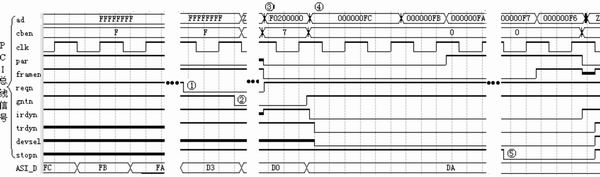

图4 PCI DMA传输仿真波形图

FIFO逻辑控制模块

FIFO逻辑控制模块根据CY7B933输出的状态信号,删除同步字K28.5,只将有效的数据读入,并将数据送入异步FIFO缓存。当FIFO空、半满、满时,对相应寄存器进行操作或通知DMA引擎模块,以防止数据的溢出或空读。

异步FIFO在核心控制模块中,主要起到两个作用。一是数据缓存,在系统进行DMA操作,将数据从ASI接口写入PC内存时,DVB-ASI数据仍在源源不断地输入系统,FIFO可以将这些数据缓存,以防止数据丢失。二是时钟隔离作用,输入的ASI信号时钟是27MHz,而PCI时钟达到33MHz,这就要求对两个频率不同的时钟进行同步,异步FIFO的数据输入和输出分别使用不同的时钟,从而实现时钟的隔离和无缝拼接。由于本设计对FIFO容量的要求较大,因此不采用Megafunction技术构造,而使用专门的高速FIFO芯片。

设计结果

在Quartus-II中进行了vhdl源程序仿真。图4是用DMA方式进行PCI传输结果的仿真波形图。其中ASI_D为模拟输入的8位ASI码流,在对相应的DMA寄存器进行操作后,启动DMA引擎,图中①处PCI_MT32通过拉低reqn信号发出总线占用请求信号,②处PCI总线仲裁器通过拉低gntn信号允许PCI_MT32成为主设备。③处进入地址阶段,PCI_MT32在ad线上提供地址,在cben线上提供总线命令。在接下来的多个数据阶段(图中④处),PCI_MT32在ad线和cben线上分别提供ASI_D输入的数据和字节使能,由于输入ASI信号是8位,而ad线为32位,因此利用ad信号的低8位来传输数据,可见,输出数据与ASI_D输入的数据相同。由于DMA传输长度的关系,本图最后通过模拟从设备断开(图中⑤处),终止了这次传输。由于DMA传输没有结束,在终止后,DMA状态机根据判断状态,还会自动继续传输。从图中可以看出,framen、irdyn、trdyn、devseln等接口控制信号完全符合PCI时序的要求。实现了将ASI信号通过PCI总线与PC进行实时数据传输的目的。图中32位ad信号的高位没有得到充分利用,如果需要,可以很方便地利用它们将电路升级为两路或4路的多路DVB-ASI码流接收卡。如果使用支持64位PCI总线的PCI_MT64功能模块,则最多可以实现8路ASI信号的接收。

结语

本系统采用FPGA加PCI IP核的模式实现对高速、大容量DVB传输流的实时传输,实现了系统设计的目标。选择PCI总线可以保证在足够的带宽下进行数据传输。FPGA的应用易于在线升级电路,扩充平台的功能。IP核的使用使硬件电路更为简洁、可靠。经过验证,本文设计的系统可以很好地实现DVB-ASI信号的接收功能,同时,也可以作为其它DVB-ASI应用的基础平台,有着良好的应用前景。

参考文献:

1 Altera Corporation. PCI Compiler User Guide. October 2005

2 李贵山,戚德虎. PCI局部总线开发者指南[M].西安:西安电子科技大学出版社,1997

3 纪献永,黄皆雨等.? DVB-ASI信号接收与发送系统的研究. 北京:电视技术,2004(11): 87-88

上一篇:一种精简可靠的低成本嵌入式以太网接口设计

下一篇:RS-232串行通信消除干扰噪声的设计方法分析

推荐阅读最新更新时间:2024-05-13 18:16

- 热门资源推荐

- 热门放大器推荐

-

ICCV2023论文汇总:Image and Video Forensics(图像和视频取证)

ICCV2023论文汇总:Image and Video Forensics(图像和视频取证) -

ICCV2023论文汇总:Humans, 3D Modeling, and Driving(人类、3D 建模和驾驶)

ICCV2023论文汇总:Humans, 3D Modeling, and Driving(人类、3D 建模和驾驶) -

ICCV2023论文汇总:Human-in-the-Loop Computer Vision(人机协同计算机视觉)

ICCV2023论文汇总:Human-in-the-Loop Computer Vision(人机协同计算机视觉) -

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐 -

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 -

微机原理与接口技术 第3版

微机原理与接口技术 第3版 -

随机信号分析(第二版)

随机信号分析(第二版) -

开关电容电路:从入门到精通

开关电容电路:从入门到精通

- TI 工业知识挑战赛开启,一起争霸前20强,赢取属于你的荣耀!

- 下载《ADI 任意波形发生器方案》抢楼有礼啦!

- 【EEWORLD第三十八届】2012年05月社区明星人物揭晓!

- 泰克送你三板斧,招招解决电源测试大难题!答题赢好礼喽!

- 【社区大讲堂】之让我们学学AVR!

- TI有奖直播|C2000™ F280013x实现更低成本且更高效的实时控制方案

- 【电源技术需求调查,为2024年蓄力!】活动开始啦~

- 一起分享,共同成长!EEWORLD月月有奖优秀主题/回复第29期

- 【分享成长,10月有奖】EEWORLD优秀主题/回复第15期活动开始啦!!!

- 阅读TI Think.lnnovate 神级DIY系列博文,你来畅想我送礼!

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 TLC2810ZP

TLC2810ZP

京公网安备 11010802033920号

京公网安备 11010802033920号