1 引言

MAX12557是Maxim公司开发的一款高速、低功耗、高性能的14位模/数转换器。该模/数转换器具有完全差分的双通道带宽采样保持(T/H)输入端,采样速率为65MS/s,输入带宽为750MHz,还具有很好的动态特性,在输入信号频率为70MHz/175MHz时,输出信噪比为74.1dB/72.5dB,无杂散动态范围为83.4dBc。MAX12557由3.3V的单电源供电,简化了外部供电电路的设计。满量程模拟输入幅度范围为±0.35V-±1.15V,用于数字输出的电压输入范围为1.7V-3.6V,易与不同的逻辑电平接口。该电路的功耗低,在输入频率为175MHz、传输信噪比为72.5dB时,功耗仅为610mW;支持单端或差分输入时钟,时钟具有用户可选的2分频(DIV2)和4分频(DIV4)模式,应用设计更灵活,并有助于减小时钟抖动的负面影响。与同类电路相比,MAX12557采用了更小巧的68引脚QFN-EP小尺寸封装(10mm×10mm×0.8mm),正常工作温度范围为-40℃-+85℃。

MAX12557可广泛应用在要求低功耗的数据采集、I/O接收器、数字机顶盒、便携式仪表、超声和医学成像,以及蜂窝通信、LMDS、点到点微波通信、MMDS、HFC、WLAN的中频与基带通信接收器等领域。

2 引脚排列及功能

MAX12557的引脚排列如图1所示。

各个引脚的功能如下所述:

GND(1,4,5,9,13,14,17)是接地参考点。

VDD(23-26,61,62,63)是模拟电源输入。将VDD接在3.15V-3.60V的供电电源上,并通过由1只10μF以上的电容器和1只0.1μF电容器组成的并联旁路与地相连。

OVDD(27,43,60)是输出驱动电源输入。将OVDD接在1.7V-VDD的供电电源上,并通过由1只10μF以上的电容器和1只0.1μF电容器组成的并联旁路与地相连。

INAP、INAN和INBP、INBN(2,3,16,15)分别为通道A、B的差分模拟输入。

COMA、COMB(6,12)是通道A、B共模电压输入/输出。COMA/COMB通过1只0.1μF的旁路电容器与地相连。

REFAP、REFAN和REFBP、REFBN(7,8,11,10)是通道A、B模拟基准电压输入/输出。通道A、B的电压变化范围是±2/3×(VREFAP/REFAB-VREFAN/REFBN)。REFAP/REFBP接1只0.1μF的旁路电容器到地。REFAP/REFBP和REFAN/REFBN之间需接10μF和1μF的旁路电容器。

DIFFCLK/SECLK(18)是选择输入时钟方式。DIFFCLK/SECLK=GND,选择单端时钟输入;DIFFCLK/?SECLK=OVDD,选择差分时钟输入。

CLKN、CLKP(19、20)是时钟输入。在差分时钟输入模式下,将差分时钟接在CLKP和CLKN之间;在单端时钟输入模式下,将时钟接在CLKP,CLKN接地。

DIV2、DIV4(21,22)是采样时钟2/4分频模式选择。

D0A-D13A、D0B-D13B(45-58,28-41)是通道A、B的14位COMS数字输出。

DORA、DORB(59,42)是通道A、B数据溢出指示。当通道A、B逻辑输入电压超出范围时,DORA/DORB数字输出发出溢出指示信号。当DORA/DORB为1时,超出范围;当DORA/DORB为0时,没有超出范围。

DAV(44)是输出数据有效指示。DAV上升沿表示当前数字输出端数据有效。

G/T(64)是输出格式选择。当接地时,选择输出格式为二进制补码。当接OVDD时,选择输出格式为格雷码。

PD(65)是电路工作状态选择。当接GND时为全工作状态;接OVDD时ADC断开。

SHREF(66)是选择共享基准电压。当为VDD时,使能共享基准。当为地时,取消共享基准。当共享基准电压时,在外部将REFAP与REFBP相连以保证VREFAP=VREFBP;将REFAN与REFBN相连以保证VREFAN=VREFBN。

REFOUT(67)是内部基准电压输出。

REFIN(68)是输入单端基准电压。

3 内部结构及工作原理

MAX12557的内部结构框图如图2所示。该电路提供了2路独立的A、D通道,每1路通道都具有独立的采样保持器(T/H)、14位流水线ADC、数字误差校正器、输出编码格式选择器、输出驱动器和基准电压生成器。电路内部集成了电压控制和偏压电路,以及用于对采样时钟进行处理的时钟分频器和占空比均衡器。

输入端采样保持(T/H)电路允许175MHz以上的模拟高频信号输入,并且支持VDD/2的共模电压输入。采样保持(T/H)结构通过采样时钟控制开关电容器的输入,将输入的模拟信号存储在采样电容器中,当采样时钟为高电平是开关关闭,此时的状态为采样模式;当采样时钟为低电平时开关打开,此时的状态为保持模块,输入的模拟信号必须提供足够的动态电流来实现对采样电容器开关的控制。为了避免信号的恶化,这些电容器的压降必须在半个时钟周期内保持输入最低有效位的1/2精确度。MAX12557在内部基准电压模式和带缓冲的外部基准电压模式下都可通过COM输出端提供最佳的共模电压VDD/2,COM端的输出电压可调整输入网络电路。

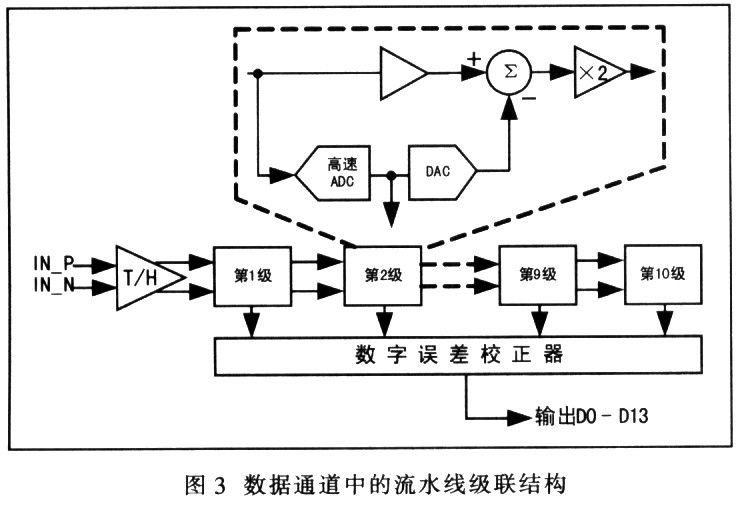

为了实现对输入模拟信号的高速转换,MAX12557在每路A/D通道中都采用了10阶全差分的流水线结构,如图3所示。这种结构使MAX12557在实现高速A/D转换时的功耗很小。整个流水线结构共分10级,电路输入端的采样数据在流水线中每半个时钟周期前进1级,从输入端到输出端的数据总延迟时间为8个时钟周期。流水线中每1个转换级都会将输入电压转换成数字编码输出。在每1级中(除了最后1级),输入电压和数字编码输出之间的误差都会被叠加并传递给下1级,数字误差校正器在每级中都会对ADC的比较偏移量进行补偿来保证采样编码输出没有遗漏。

MAX12557满幅度模拟输入电压范围是±2/3×VREF,共模输入时电压范围为VDD/2±0.5V。VREF是REFAP(REFBP)与REFAN(REFBN)之间的电压差。该电路提供了3种基准电压工作模式。如表1所示。REFIN端的输入电压用于选择电路的基准电压工作模式。将REFOUT与REFIN之间短接或者通过1个电阻分压器连接起来都会进入内部基准模式。带缓冲器的外部基准电压模式实际上与内部基准电压模式是等效的,除非基准电压系统由外部基准驱动而不由电路内部的带隙基准驱动。MAX12557还有1种共享基准电压模式,通过这种模式用户可以更好地实现通道间的接口。

4 应用电路及需注意的问题

图4示出MAX12557在宽带中频数字接收机中的应用框图。该接收机实现了对载波频率为70MHz、数据率为10Mb/s、最大载波频偏为±70KHz的QPSK调制信号的解调。由于中频调制信号是高载波的带通信号,带宽为10MHz,所以接收时采用欠采样技术,根据带通抽样定理,该ADC的采样频率选为40MHz。

接收到的中频调制信号经带通滤波后送入MAX12557,MAX12557在外部FPGA(现场可编程门阵列)控制下对信号进行采样,在电路内部由通道A将采样后的数字信号送入FPGA中进行数字解调并提取有用的调制信息。选用Xilinx公司生产的Virtex?Ⅱ系列XC2V3000型FPGA。中频接收机采用全数字解调方式,采样信号在FPGA内部移相后生成1、Q2路正交信号分别进行数字解调。数字解调中I、Q2路数字混频器和滤波器的特性完全一致,可以避免模拟调制时由于模拟器件特性的一致性和稳定性不理想而导致的I、Q通道间幅度不平衡及相位正交误差较大的现象。

图5示出MAX12557的外围电路,中频接受信号经过MAX4108型运算放大器将信号放大后送入ADC。制作电路板时需要注意以下几点:

(1)应用电路最好采用多层板设计,这样可以保持完整的电源层和地层,降低电源内阻,得到更大的对地电容器,抑制和屏蔽电源路径上的噪声,有效控制信号间的串扰,而且可以保证信号线具有稳定的特征阻抗。

(2)设计电路板时,各引脚的旁路电容器应尽可能地放置在靠近电路的位置,最好能在电路的同一侧,并采用贴片元件来减少感应系数。PCB所有的接地线和电路的扩展引脚都必须连在相同的地层上,同时要注意电路所有外接元件的均匀分布。

(3)MAX4108型运算放大器输出端应尽量靠近ADC的输入端(INAP),以减小信号波形失真和能量损耗。电源引脚VDD和OVDD都需通过1只220μF的陶瓷电容器与地连接,同时电容器需并联至少1只10μF、4.7μF和0.1μF的陶瓷电容器。高频旁路去耦电容器应该尽可能靠近A/D变换器的引脚。

经过实际硬件测试,MAX12557的工作正常,功耗低,可满足接收机系统的设计要求。

上一篇:小型UPS的原理与维护

下一篇:电源质量问题地危害及解决方案

推荐阅读最新更新时间:2024-05-13 18:14

- 2024年Automechanika Shanghai海量同期活动刷新历届记录,汇聚行业智慧,共谋未来发展

- 企业文化分享 如何培养稀缺的硅IP专业人员?SmartDV开启的个人成长与团队协作之旅

- 恩智浦发布首个超宽带无线电池管理系统解决方案

- 北交大本科生探秘泰克先进半导体开放实验室,亲历前沿高科技魅力

- 新帅上任:杜德森博士(Dr. Torsten Derr)将于2025年1月1日出任肖特集团首席执行官

- 边缘 AI 如何提升日常体验

- 苹果要首发!台积电宣布2nm已准备就绪

- AMD有望用上全新芯片堆叠技术:延迟大幅减少、性能显著提升

- 宁德时代发布10月战报

- 2024年10月电池行业:增长势头不减!

ICCV2023论文汇总:Deep Learning Architectures and Techniques(深度学习架构与技术)

ICCV2023论文汇总:Deep Learning Architectures and Techniques(深度学习架构与技术) GB/T 31466-2015 电动汽车高压系统电压等级

GB/T 31466-2015 电动汽车高压系统电压等级 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号