[b]0 引言

[/b] 传统的逆变技术虽然成熟可靠、应用广泛,但存在体积大且笨重、音频噪音大、系统动态特性差等缺点。用高频变压器替代传统逆变器中的工频变压器,克服了传统逆变器的缺点,显著提高了逆变器的特性。高频脉冲交流环节逆变器具有双向功率流、两级功率变换(DC/HFAC/LFAC)、变换效率和可靠性高等特点,成为近几年电源界研究的热点。

1 新颖的变频变换系统

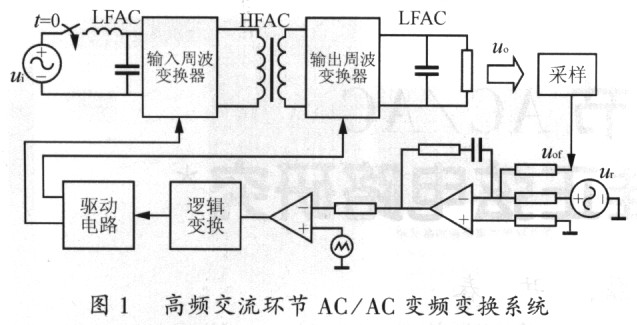

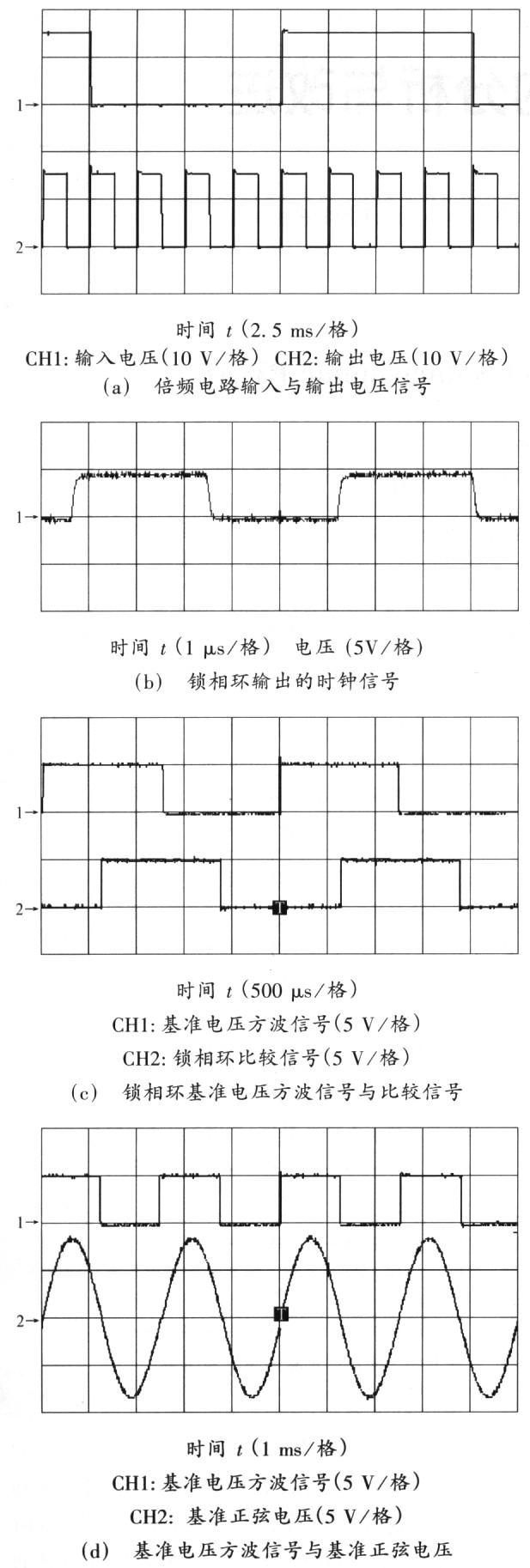

新颖的高频交流环节AC/AC变频变换系统,如图1所示。该电路由输入周波变换器、高频变压器或高频储能式变压器、输出周波变换器构成,能够将一种频率的交流电变换成另一种频率的交流电,具有两级功率变换(LFAC/HFAC/LFAC)、变换效率高、双向功率流、高频电气隔离、无音频噪音等优点,是实现新型变频电源的关键技术基础。

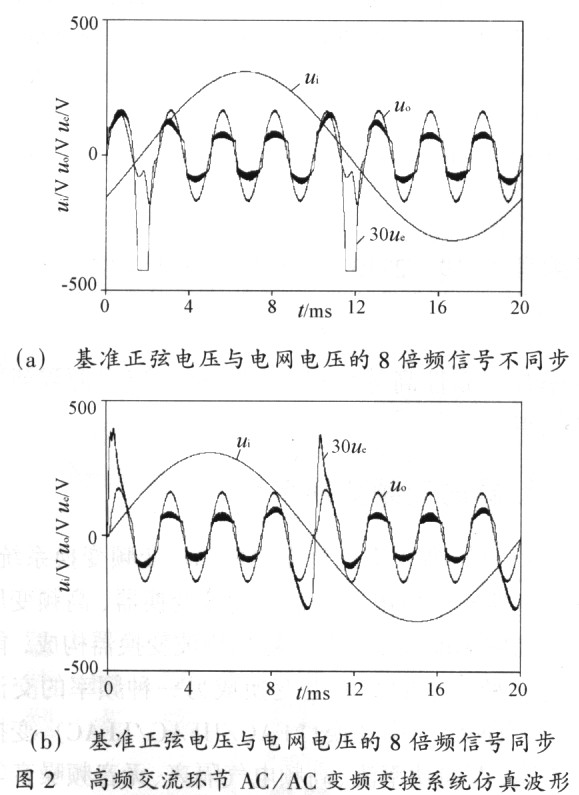

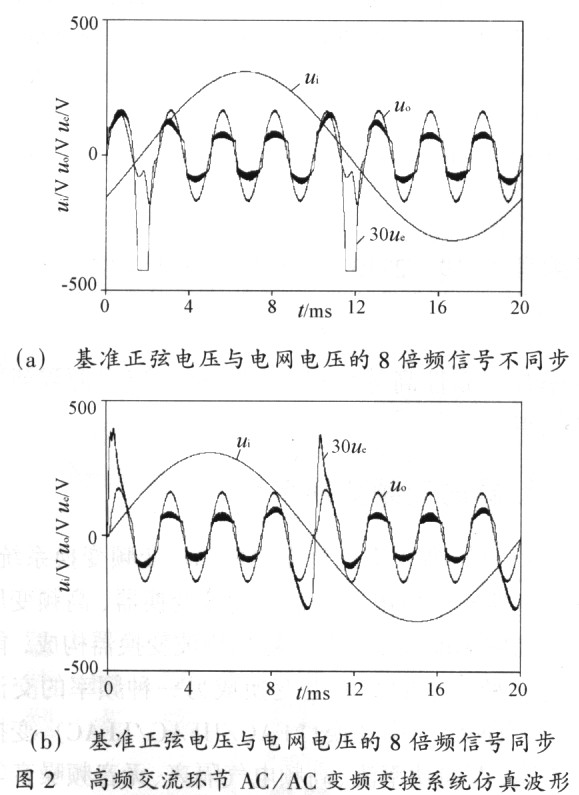

图1所示变换系统中,输出电压。u0总是跟踪基准正弦电压ur山的。如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号不同步,当输入电网电压ui很小(如过零点)、且要得到较大的输出电压u0时,则要求PWM信号占空比很大,从而使PI调节器输出饱和,那么输出电压u0就无法跟踪基准正弦电压ur,输出电压u0波形就产生了畸变,仿真波形如图2(a)所示;如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号同步,即基准正弦电压ur与输入电网电压ui的过零点重合,则不会产生上述PI调节器输出饱和现象,输出电压u0能很好地跟踪基准正弦电压ur,仿真波形如图2(b)所示。图2中,ui为输入电网电压,u0为输出电压,ue为Pl调节器输出电压。

图1所示变换系统中,输出电压。u0总是跟踪基准正弦电压ur山的。如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号不同步,当输入电网电压ui很小(如过零点)、且要得到较大的输出电压u0时,则要求PWM信号占空比很大,从而使PI调节器输出饱和,那么输出电压u0就无法跟踪基准正弦电压ur,输出电压u0波形就产生了畸变,仿真波形如图2(a)所示;如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号同步,即基准正弦电压ur与输入电网电压ui的过零点重合,则不会产生上述PI调节器输出饱和现象,输出电压u0能很好地跟踪基准正弦电压ur,仿真波形如图2(b)所示。图2中,ui为输入电网电压,u0为输出电压,ue为Pl调节器输出电压。

因此,基准正弦电压ur与输入电网电压ui的n倍频或n分频信号必须同步。本文提出并深入研究了一类全数字化技术、与电网电压n倍频或n分频信号同步的基准正弦电路,并给出了关键电路参数设计准则和试验结果。

2 与电网电压n倍频或n分频信号同步的基准正弦电路构成与原理

2.1 基准正弦电路构成

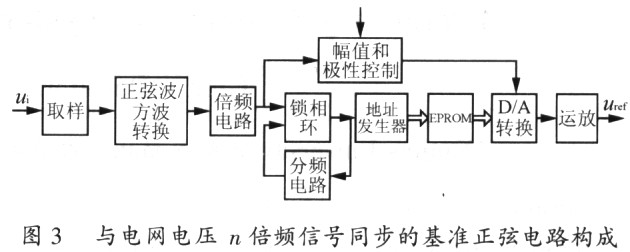

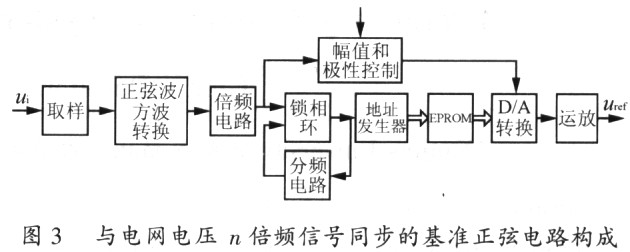

与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频电路或分频电路、时钟信号形成电路(包括锁相环和分频电路)、相位同步电路(即地址发生器清零信号形成电路)、正弦波幅值和极性控制电路、正弦波产生电路(包括EPROM、D/A转换电路和运放)等6个部分组成,如图3所示。

因此,基准正弦电压ur与输入电网电压ui的n倍频或n分频信号必须同步。本文提出并深入研究了一类全数字化技术、与电网电压n倍频或n分频信号同步的基准正弦电路,并给出了关键电路参数设计准则和试验结果。

2 与电网电压n倍频或n分频信号同步的基准正弦电路构成与原理

2.1 基准正弦电路构成

与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频电路或分频电路、时钟信号形成电路(包括锁相环和分频电路)、相位同步电路(即地址发生器清零信号形成电路)、正弦波幅值和极性控制电路、正弦波产生电路(包括EPROM、D/A转换电路和运放)等6个部分组成,如图3所示。

其基本思想是先将电网电压ui变换成一个与其同步的电压方波信号,将电压方波信号n倍频后(如n=8)得到基准电压方波信号,输入到锁相环,锁相环输出信号经爪分频电路(如m=450)后再送回锁相环,作为基准电压方波信号的比较信号。当锁相环处于锁定状态时,锁相环输出频率为基准电压方波信号m倍的时钟信号。该时钟信号送入地址发生器,然后依次读取出事先固化在EPROM中的数字化的标准正弦信号,再经过D/A转换和运放,变换成与基准电压方波信号同步的基准正弦电压。

2.2 基准正弦电路原理

与电网电压8倍频信号同步的基准正弦电路的各环节电路,如图4所示。

其基本思想是先将电网电压ui变换成一个与其同步的电压方波信号,将电压方波信号n倍频后(如n=8)得到基准电压方波信号,输入到锁相环,锁相环输出信号经爪分频电路(如m=450)后再送回锁相环,作为基准电压方波信号的比较信号。当锁相环处于锁定状态时,锁相环输出频率为基准电压方波信号m倍的时钟信号。该时钟信号送入地址发生器,然后依次读取出事先固化在EPROM中的数字化的标准正弦信号,再经过D/A转换和运放,变换成与基准电压方波信号同步的基准正弦电压。

2.2 基准正弦电路原理

与电网电压8倍频信号同步的基准正弦电路的各环节电路,如图4所示。

电网电压取样与正弦波/方波转换电路由变压器取样、过零比较器组成,其输出的电压方波信号与电网电压同步。

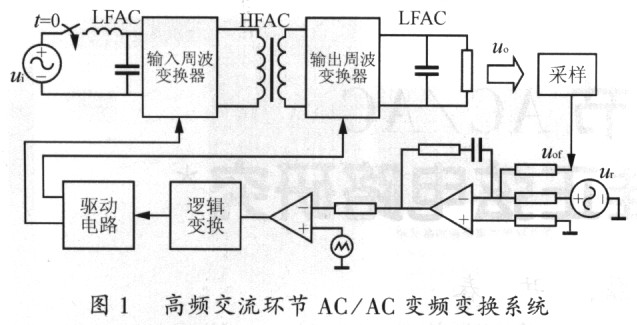

倍频电路,如图4(a)所示。电路中,R1和C1组成微分电路,输入方波信号前沿经R1和C1,并通过与非门产生输出方波。与此同时,输入方波信号后沿通过反相器和R2和C2微分电路,再经与非门也产生输出方波,于是在与非门输出端得到的是倍频方波信号。上述一级电路得到倍频,3级电路串联得到8倍频方波信号即基准电压方波信号。

时钟信号形成电路,如图4(b)所示。将基准电压方波信号输入锁相环,由锁相环输出电路所需的时钟信号。在锁相环的锁定状态下,该时钟信号频率为基准电压方波信号频率的450倍。该时钟信号经分频器4520和40175实现450分频,所得信号作为锁相环的比较信号。将此时钟信号送入地址发生器4040。

相位同步电路即4040清零信号的形成电路,如图4(c)所示。将基准方波电压信号及其经过与非门4011后的反相信号一起送人单稳态触发器4528,经或门407l后得到4040的清零信号,以实现4040的225分频计数,从而保证对EPROM中数据的正确读取,以及数据经D/A转换后与正弦波正负半周极性控制信号严格对应。

正弦波幅值和极性控制电路由运放LF353与模拟开关4066及外围电阻R6、R7、R8组成,如图4(d)所示。取R6=R7=R8,则该电路实质是一个单位增益放大器。由于4066控制信号为基准电压方波信号,则LF353输出双极性方波信号。该双极性方波信号作为模数转换器DAC0832的参考电压信号,且与所需要产生的基准正弦电压同相。通过调节电位器,可以调节基准正弦电压的幅值。

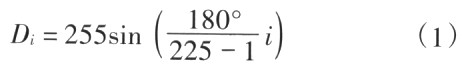

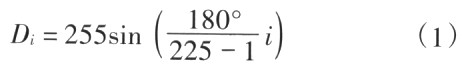

正弦波产生电路由地址发生器4040、EPROM27C64、DAC0832和LF353组成,如图4(c)所示。其核心是EPROM27C64和DAC0832。考虑到DAC0832的极性控制功能,可事先将半周期正弦波进行225分频离线采样,算好其幅值后按序排成数据表存入EPROM中。EPROM中存入的数据表的计算式为

电网电压取样与正弦波/方波转换电路由变压器取样、过零比较器组成,其输出的电压方波信号与电网电压同步。

倍频电路,如图4(a)所示。电路中,R1和C1组成微分电路,输入方波信号前沿经R1和C1,并通过与非门产生输出方波。与此同时,输入方波信号后沿通过反相器和R2和C2微分电路,再经与非门也产生输出方波,于是在与非门输出端得到的是倍频方波信号。上述一级电路得到倍频,3级电路串联得到8倍频方波信号即基准电压方波信号。

时钟信号形成电路,如图4(b)所示。将基准电压方波信号输入锁相环,由锁相环输出电路所需的时钟信号。在锁相环的锁定状态下,该时钟信号频率为基准电压方波信号频率的450倍。该时钟信号经分频器4520和40175实现450分频,所得信号作为锁相环的比较信号。将此时钟信号送入地址发生器4040。

相位同步电路即4040清零信号的形成电路,如图4(c)所示。将基准方波电压信号及其经过与非门4011后的反相信号一起送人单稳态触发器4528,经或门407l后得到4040的清零信号,以实现4040的225分频计数,从而保证对EPROM中数据的正确读取,以及数据经D/A转换后与正弦波正负半周极性控制信号严格对应。

正弦波幅值和极性控制电路由运放LF353与模拟开关4066及外围电阻R6、R7、R8组成,如图4(d)所示。取R6=R7=R8,则该电路实质是一个单位增益放大器。由于4066控制信号为基准电压方波信号,则LF353输出双极性方波信号。该双极性方波信号作为模数转换器DAC0832的参考电压信号,且与所需要产生的基准正弦电压同相。通过调节电位器,可以调节基准正弦电压的幅值。

正弦波产生电路由地址发生器4040、EPROM27C64、DAC0832和LF353组成,如图4(c)所示。其核心是EPROM27C64和DAC0832。考虑到DAC0832的极性控制功能,可事先将半周期正弦波进行225分频离线采样,算好其幅值后按序排成数据表存入EPROM中。EPROM中存入的数据表的计算式为

式中:i=0,1,2,3,4……224;225为FFH对应的十进制数。

锁相环输出的时钟信号输入到地址发生器4040,4040顺序扫描存入EPROM中的数据表,则代表正弦波幅值的8位二进制数被送到DAC0832,将数字量转换成模拟量输出。周而复始,产生一串阶梯正弦波形。由于DAC0832为电流型器件,因此,必须与运算放大器连接,构成D/A转换器。

3 关键电路参数设计

锁相环CD4046B是整个电路关键器件之一,其锁定范围和外围电阻R4、R5和电容C4有很大关系。R3和C3构成了锁相环CD4046B的外接低通滤波器。

3.1 CD4046B的外接电阻R4、R5和外接电容C4的设计

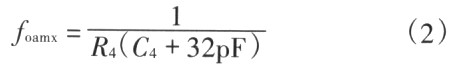

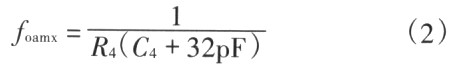

当无须R5的补偿,即R5为无穷大时,锁相环的输出频率范围从零到最高输出频率fomax,且

式中:i=0,1,2,3,4……224;225为FFH对应的十进制数。

锁相环输出的时钟信号输入到地址发生器4040,4040顺序扫描存入EPROM中的数据表,则代表正弦波幅值的8位二进制数被送到DAC0832,将数字量转换成模拟量输出。周而复始,产生一串阶梯正弦波形。由于DAC0832为电流型器件,因此,必须与运算放大器连接,构成D/A转换器。

3 关键电路参数设计

锁相环CD4046B是整个电路关键器件之一,其锁定范围和外围电阻R4、R5和电容C4有很大关系。R3和C3构成了锁相环CD4046B的外接低通滤波器。

3.1 CD4046B的外接电阻R4、R5和外接电容C4的设计

当无须R5的补偿,即R5为无穷大时,锁相环的输出频率范围从零到最高输出频率fomax,且

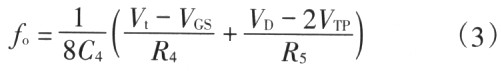

此时fomin=0。在特定的使用状态下,若要限制锁相环的输出频率范围,可通过R5的补偿作用来实现。锁相环输出频率fo的估算式为

此时fomin=0。在特定的使用状态下,若要限制锁相环的输出频率范围,可通过R5的补偿作用来实现。锁相环输出频率fo的估算式为

式中: V1为锁相环压控振荡器的输入信号(即CD4046脚9的电平),其幅值正比于基准电压方波信号和锁相环比较信号之间的相位差;VGS和VTP分别为锁相环内部MOS管的栅一源极压降和栅极的开启阈值电平;VD为锁相环工作电压。

因为本电路要求锁相环的输出频率经过450分频后为400Hz,即锁相环必须锁定在180000Hz附近,故可取R4=10kΩ,R5=∞,C4=1000pF。

3.2 CD4046B低通滤波器R3、C3的设计

适当选择R3和C3,对改善环路捕捉性能及工作稳定性很有作用。若取较大的时间常数R3C3,则会使环路跟踪较快变化的输入频率时引起过度的延迟;若取较小的时间常数R3C3,则会使环路跟踪快速变化的输入信号时,引起锁相环输出频率的反常变化。综合考虑,选择R3=100kΩ,C3=2μF。

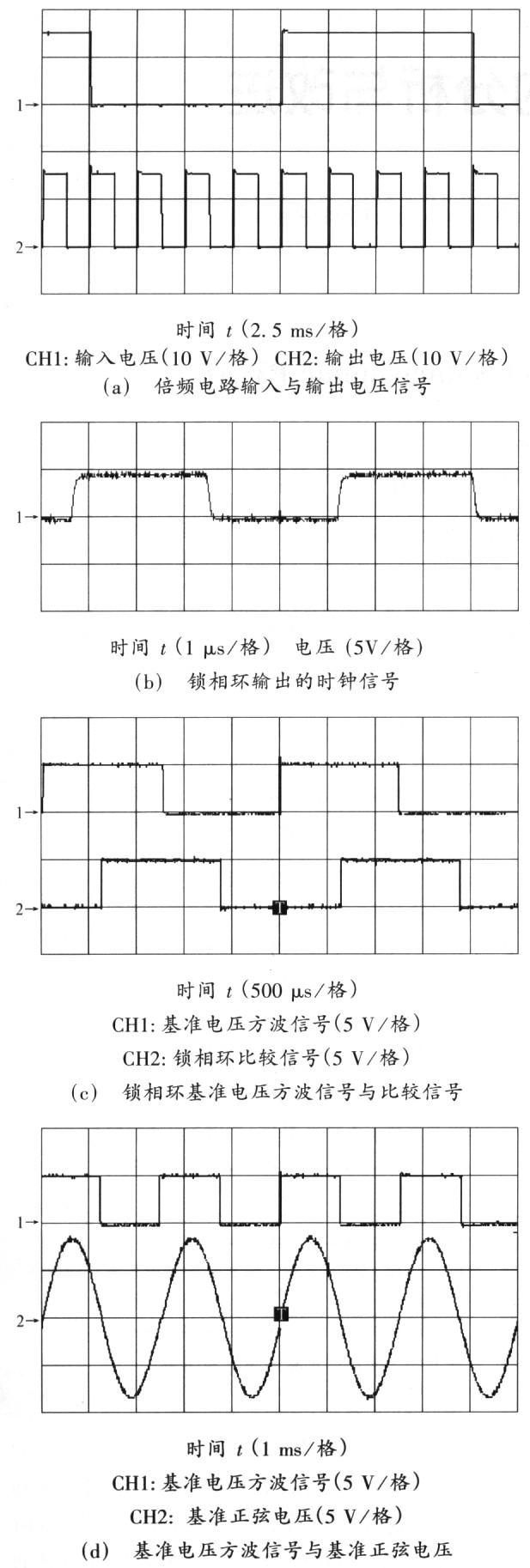

4 基准正弦电路设计实例与试验

与电网电压8倍频信号同步的基准正弦电路设计实例:输入电压=220(1%26;#177;10%)V 50Hz,基准输出电压=0"15V(峰值)400Hz,锁相环芯片CD4046B,地址发生器4040,EPROM27C64,数模转换芯片DAC0832,分频器4520及40175,单稳态触发器4528,C1=C2=100nF,C3=2μF,c3=1000nF。R1及R2用电位器504,R3=100kΩ,R4=10kΩ。R5=∞,R6=R7=R8=150kΩ。

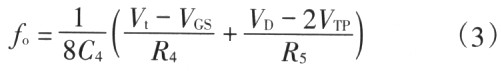

设计并研制成功的与电网电压8倍频信号同步的基准正弦电路试验结果,如图5所示。由图5可见,该基准正弦电路具有输出电压与电网电压8倍频信号同步、THD小、幅值可调但不受电网电压波动的影响等优点。试验结果与理论分析一致。

式中: V1为锁相环压控振荡器的输入信号(即CD4046脚9的电平),其幅值正比于基准电压方波信号和锁相环比较信号之间的相位差;VGS和VTP分别为锁相环内部MOS管的栅一源极压降和栅极的开启阈值电平;VD为锁相环工作电压。

因为本电路要求锁相环的输出频率经过450分频后为400Hz,即锁相环必须锁定在180000Hz附近,故可取R4=10kΩ,R5=∞,C4=1000pF。

3.2 CD4046B低通滤波器R3、C3的设计

适当选择R3和C3,对改善环路捕捉性能及工作稳定性很有作用。若取较大的时间常数R3C3,则会使环路跟踪较快变化的输入频率时引起过度的延迟;若取较小的时间常数R3C3,则会使环路跟踪快速变化的输入信号时,引起锁相环输出频率的反常变化。综合考虑,选择R3=100kΩ,C3=2μF。

4 基准正弦电路设计实例与试验

与电网电压8倍频信号同步的基准正弦电路设计实例:输入电压=220(1%26;#177;10%)V 50Hz,基准输出电压=0"15V(峰值)400Hz,锁相环芯片CD4046B,地址发生器4040,EPROM27C64,数模转换芯片DAC0832,分频器4520及40175,单稳态触发器4528,C1=C2=100nF,C3=2μF,c3=1000nF。R1及R2用电位器504,R3=100kΩ,R4=10kΩ。R5=∞,R6=R7=R8=150kΩ。

设计并研制成功的与电网电压8倍频信号同步的基准正弦电路试验结果,如图5所示。由图5可见,该基准正弦电路具有输出电压与电网电压8倍频信号同步、THD小、幅值可调但不受电网电压波动的影响等优点。试验结果与理论分析一致。

5 结语

1)高频交流环节AC/AC变频变换系统基准正弦电压必须与电网电压的n倍频或n分频信号同步。

2)与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频或分频电路、时钟信号产生电路、相位同步电路、正弦波幅值和极性控制电路、正弦波产生电路等6个部分构成。

3)该基准正弦电路具有与电网电压n倍频或n分频同步、THD小、幅值可调但不受电网电压波动的影响、简单实用、价格低廉等优点。

4)试验结果与理论分析一致。

5 结语

1)高频交流环节AC/AC变频变换系统基准正弦电压必须与电网电压的n倍频或n分频信号同步。

2)与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频或分频电路、时钟信号产生电路、相位同步电路、正弦波幅值和极性控制电路、正弦波产生电路等6个部分构成。

3)该基准正弦电路具有与电网电压n倍频或n分频同步、THD小、幅值可调但不受电网电压波动的影响、简单实用、价格低廉等优点。

4)试验结果与理论分析一致。

引用地址:高频交流环节AC/AC变频变换系统基准正弦电路研究

图1所示变换系统中,输出电压。u0总是跟踪基准正弦电压ur山的。如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号不同步,当输入电网电压ui很小(如过零点)、且要得到较大的输出电压u0时,则要求PWM信号占空比很大,从而使PI调节器输出饱和,那么输出电压u0就无法跟踪基准正弦电压ur,输出电压u0波形就产生了畸变,仿真波形如图2(a)所示;如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号同步,即基准正弦电压ur与输入电网电压ui的过零点重合,则不会产生上述PI调节器输出饱和现象,输出电压u0能很好地跟踪基准正弦电压ur,仿真波形如图2(b)所示。图2中,ui为输入电网电压,u0为输出电压,ue为Pl调节器输出电压。

图1所示变换系统中,输出电压。u0总是跟踪基准正弦电压ur山的。如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号不同步,当输入电网电压ui很小(如过零点)、且要得到较大的输出电压u0时,则要求PWM信号占空比很大,从而使PI调节器输出饱和,那么输出电压u0就无法跟踪基准正弦电压ur,输出电压u0波形就产生了畸变,仿真波形如图2(a)所示;如果基准正弦电压ur与输入电网电压ui的n倍频或n分频信号同步,即基准正弦电压ur与输入电网电压ui的过零点重合,则不会产生上述PI调节器输出饱和现象,输出电压u0能很好地跟踪基准正弦电压ur,仿真波形如图2(b)所示。图2中,ui为输入电网电压,u0为输出电压,ue为Pl调节器输出电压。

因此,基准正弦电压ur与输入电网电压ui的n倍频或n分频信号必须同步。本文提出并深入研究了一类全数字化技术、与电网电压n倍频或n分频信号同步的基准正弦电路,并给出了关键电路参数设计准则和试验结果。

2 与电网电压n倍频或n分频信号同步的基准正弦电路构成与原理

2.1 基准正弦电路构成

与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频电路或分频电路、时钟信号形成电路(包括锁相环和分频电路)、相位同步电路(即地址发生器清零信号形成电路)、正弦波幅值和极性控制电路、正弦波产生电路(包括EPROM、D/A转换电路和运放)等6个部分组成,如图3所示。

因此,基准正弦电压ur与输入电网电压ui的n倍频或n分频信号必须同步。本文提出并深入研究了一类全数字化技术、与电网电压n倍频或n分频信号同步的基准正弦电路,并给出了关键电路参数设计准则和试验结果。

2 与电网电压n倍频或n分频信号同步的基准正弦电路构成与原理

2.1 基准正弦电路构成

与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频电路或分频电路、时钟信号形成电路(包括锁相环和分频电路)、相位同步电路(即地址发生器清零信号形成电路)、正弦波幅值和极性控制电路、正弦波产生电路(包括EPROM、D/A转换电路和运放)等6个部分组成,如图3所示。

其基本思想是先将电网电压ui变换成一个与其同步的电压方波信号,将电压方波信号n倍频后(如n=8)得到基准电压方波信号,输入到锁相环,锁相环输出信号经爪分频电路(如m=450)后再送回锁相环,作为基准电压方波信号的比较信号。当锁相环处于锁定状态时,锁相环输出频率为基准电压方波信号m倍的时钟信号。该时钟信号送入地址发生器,然后依次读取出事先固化在EPROM中的数字化的标准正弦信号,再经过D/A转换和运放,变换成与基准电压方波信号同步的基准正弦电压。

2.2 基准正弦电路原理

与电网电压8倍频信号同步的基准正弦电路的各环节电路,如图4所示。

其基本思想是先将电网电压ui变换成一个与其同步的电压方波信号,将电压方波信号n倍频后(如n=8)得到基准电压方波信号,输入到锁相环,锁相环输出信号经爪分频电路(如m=450)后再送回锁相环,作为基准电压方波信号的比较信号。当锁相环处于锁定状态时,锁相环输出频率为基准电压方波信号m倍的时钟信号。该时钟信号送入地址发生器,然后依次读取出事先固化在EPROM中的数字化的标准正弦信号,再经过D/A转换和运放,变换成与基准电压方波信号同步的基准正弦电压。

2.2 基准正弦电路原理

与电网电压8倍频信号同步的基准正弦电路的各环节电路,如图4所示。

电网电压取样与正弦波/方波转换电路由变压器取样、过零比较器组成,其输出的电压方波信号与电网电压同步。

倍频电路,如图4(a)所示。电路中,R1和C1组成微分电路,输入方波信号前沿经R1和C1,并通过与非门产生输出方波。与此同时,输入方波信号后沿通过反相器和R2和C2微分电路,再经与非门也产生输出方波,于是在与非门输出端得到的是倍频方波信号。上述一级电路得到倍频,3级电路串联得到8倍频方波信号即基准电压方波信号。

时钟信号形成电路,如图4(b)所示。将基准电压方波信号输入锁相环,由锁相环输出电路所需的时钟信号。在锁相环的锁定状态下,该时钟信号频率为基准电压方波信号频率的450倍。该时钟信号经分频器4520和40175实现450分频,所得信号作为锁相环的比较信号。将此时钟信号送入地址发生器4040。

相位同步电路即4040清零信号的形成电路,如图4(c)所示。将基准方波电压信号及其经过与非门4011后的反相信号一起送人单稳态触发器4528,经或门407l后得到4040的清零信号,以实现4040的225分频计数,从而保证对EPROM中数据的正确读取,以及数据经D/A转换后与正弦波正负半周极性控制信号严格对应。

正弦波幅值和极性控制电路由运放LF353与模拟开关4066及外围电阻R6、R7、R8组成,如图4(d)所示。取R6=R7=R8,则该电路实质是一个单位增益放大器。由于4066控制信号为基准电压方波信号,则LF353输出双极性方波信号。该双极性方波信号作为模数转换器DAC0832的参考电压信号,且与所需要产生的基准正弦电压同相。通过调节电位器,可以调节基准正弦电压的幅值。

正弦波产生电路由地址发生器4040、EPROM27C64、DAC0832和LF353组成,如图4(c)所示。其核心是EPROM27C64和DAC0832。考虑到DAC0832的极性控制功能,可事先将半周期正弦波进行225分频离线采样,算好其幅值后按序排成数据表存入EPROM中。EPROM中存入的数据表的计算式为

电网电压取样与正弦波/方波转换电路由变压器取样、过零比较器组成,其输出的电压方波信号与电网电压同步。

倍频电路,如图4(a)所示。电路中,R1和C1组成微分电路,输入方波信号前沿经R1和C1,并通过与非门产生输出方波。与此同时,输入方波信号后沿通过反相器和R2和C2微分电路,再经与非门也产生输出方波,于是在与非门输出端得到的是倍频方波信号。上述一级电路得到倍频,3级电路串联得到8倍频方波信号即基准电压方波信号。

时钟信号形成电路,如图4(b)所示。将基准电压方波信号输入锁相环,由锁相环输出电路所需的时钟信号。在锁相环的锁定状态下,该时钟信号频率为基准电压方波信号频率的450倍。该时钟信号经分频器4520和40175实现450分频,所得信号作为锁相环的比较信号。将此时钟信号送入地址发生器4040。

相位同步电路即4040清零信号的形成电路,如图4(c)所示。将基准方波电压信号及其经过与非门4011后的反相信号一起送人单稳态触发器4528,经或门407l后得到4040的清零信号,以实现4040的225分频计数,从而保证对EPROM中数据的正确读取,以及数据经D/A转换后与正弦波正负半周极性控制信号严格对应。

正弦波幅值和极性控制电路由运放LF353与模拟开关4066及外围电阻R6、R7、R8组成,如图4(d)所示。取R6=R7=R8,则该电路实质是一个单位增益放大器。由于4066控制信号为基准电压方波信号,则LF353输出双极性方波信号。该双极性方波信号作为模数转换器DAC0832的参考电压信号,且与所需要产生的基准正弦电压同相。通过调节电位器,可以调节基准正弦电压的幅值。

正弦波产生电路由地址发生器4040、EPROM27C64、DAC0832和LF353组成,如图4(c)所示。其核心是EPROM27C64和DAC0832。考虑到DAC0832的极性控制功能,可事先将半周期正弦波进行225分频离线采样,算好其幅值后按序排成数据表存入EPROM中。EPROM中存入的数据表的计算式为

式中:i=0,1,2,3,4……224;225为FFH对应的十进制数。

锁相环输出的时钟信号输入到地址发生器4040,4040顺序扫描存入EPROM中的数据表,则代表正弦波幅值的8位二进制数被送到DAC0832,将数字量转换成模拟量输出。周而复始,产生一串阶梯正弦波形。由于DAC0832为电流型器件,因此,必须与运算放大器连接,构成D/A转换器。

3 关键电路参数设计

锁相环CD4046B是整个电路关键器件之一,其锁定范围和外围电阻R4、R5和电容C4有很大关系。R3和C3构成了锁相环CD4046B的外接低通滤波器。

3.1 CD4046B的外接电阻R4、R5和外接电容C4的设计

当无须R5的补偿,即R5为无穷大时,锁相环的输出频率范围从零到最高输出频率fomax,且

式中:i=0,1,2,3,4……224;225为FFH对应的十进制数。

锁相环输出的时钟信号输入到地址发生器4040,4040顺序扫描存入EPROM中的数据表,则代表正弦波幅值的8位二进制数被送到DAC0832,将数字量转换成模拟量输出。周而复始,产生一串阶梯正弦波形。由于DAC0832为电流型器件,因此,必须与运算放大器连接,构成D/A转换器。

3 关键电路参数设计

锁相环CD4046B是整个电路关键器件之一,其锁定范围和外围电阻R4、R5和电容C4有很大关系。R3和C3构成了锁相环CD4046B的外接低通滤波器。

3.1 CD4046B的外接电阻R4、R5和外接电容C4的设计

当无须R5的补偿,即R5为无穷大时,锁相环的输出频率范围从零到最高输出频率fomax,且

此时fomin=0。在特定的使用状态下,若要限制锁相环的输出频率范围,可通过R5的补偿作用来实现。锁相环输出频率fo的估算式为

此时fomin=0。在特定的使用状态下,若要限制锁相环的输出频率范围,可通过R5的补偿作用来实现。锁相环输出频率fo的估算式为

式中: V1为锁相环压控振荡器的输入信号(即CD4046脚9的电平),其幅值正比于基准电压方波信号和锁相环比较信号之间的相位差;VGS和VTP分别为锁相环内部MOS管的栅一源极压降和栅极的开启阈值电平;VD为锁相环工作电压。

因为本电路要求锁相环的输出频率经过450分频后为400Hz,即锁相环必须锁定在180000Hz附近,故可取R4=10kΩ,R5=∞,C4=1000pF。

3.2 CD4046B低通滤波器R3、C3的设计

适当选择R3和C3,对改善环路捕捉性能及工作稳定性很有作用。若取较大的时间常数R3C3,则会使环路跟踪较快变化的输入频率时引起过度的延迟;若取较小的时间常数R3C3,则会使环路跟踪快速变化的输入信号时,引起锁相环输出频率的反常变化。综合考虑,选择R3=100kΩ,C3=2μF。

4 基准正弦电路设计实例与试验

与电网电压8倍频信号同步的基准正弦电路设计实例:输入电压=220(1%26;#177;10%)V 50Hz,基准输出电压=0"15V(峰值)400Hz,锁相环芯片CD4046B,地址发生器4040,EPROM27C64,数模转换芯片DAC0832,分频器4520及40175,单稳态触发器4528,C1=C2=100nF,C3=2μF,c3=1000nF。R1及R2用电位器504,R3=100kΩ,R4=10kΩ。R5=∞,R6=R7=R8=150kΩ。

设计并研制成功的与电网电压8倍频信号同步的基准正弦电路试验结果,如图5所示。由图5可见,该基准正弦电路具有输出电压与电网电压8倍频信号同步、THD小、幅值可调但不受电网电压波动的影响等优点。试验结果与理论分析一致。

式中: V1为锁相环压控振荡器的输入信号(即CD4046脚9的电平),其幅值正比于基准电压方波信号和锁相环比较信号之间的相位差;VGS和VTP分别为锁相环内部MOS管的栅一源极压降和栅极的开启阈值电平;VD为锁相环工作电压。

因为本电路要求锁相环的输出频率经过450分频后为400Hz,即锁相环必须锁定在180000Hz附近,故可取R4=10kΩ,R5=∞,C4=1000pF。

3.2 CD4046B低通滤波器R3、C3的设计

适当选择R3和C3,对改善环路捕捉性能及工作稳定性很有作用。若取较大的时间常数R3C3,则会使环路跟踪较快变化的输入频率时引起过度的延迟;若取较小的时间常数R3C3,则会使环路跟踪快速变化的输入信号时,引起锁相环输出频率的反常变化。综合考虑,选择R3=100kΩ,C3=2μF。

4 基准正弦电路设计实例与试验

与电网电压8倍频信号同步的基准正弦电路设计实例:输入电压=220(1%26;#177;10%)V 50Hz,基准输出电压=0"15V(峰值)400Hz,锁相环芯片CD4046B,地址发生器4040,EPROM27C64,数模转换芯片DAC0832,分频器4520及40175,单稳态触发器4528,C1=C2=100nF,C3=2μF,c3=1000nF。R1及R2用电位器504,R3=100kΩ,R4=10kΩ。R5=∞,R6=R7=R8=150kΩ。

设计并研制成功的与电网电压8倍频信号同步的基准正弦电路试验结果,如图5所示。由图5可见,该基准正弦电路具有输出电压与电网电压8倍频信号同步、THD小、幅值可调但不受电网电压波动的影响等优点。试验结果与理论分析一致。

5 结语

1)高频交流环节AC/AC变频变换系统基准正弦电压必须与电网电压的n倍频或n分频信号同步。

2)与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频或分频电路、时钟信号产生电路、相位同步电路、正弦波幅值和极性控制电路、正弦波产生电路等6个部分构成。

3)该基准正弦电路具有与电网电压n倍频或n分频同步、THD小、幅值可调但不受电网电压波动的影响、简单实用、价格低廉等优点。

4)试验结果与理论分析一致。

5 结语

1)高频交流环节AC/AC变频变换系统基准正弦电压必须与电网电压的n倍频或n分频信号同步。

2)与电网电压n倍频或n分频信号同步的基准正弦电路,由电网电压取样和正弦波/方波转换电路、倍频或分频电路、时钟信号产生电路、相位同步电路、正弦波幅值和极性控制电路、正弦波产生电路等6个部分构成。

3)该基准正弦电路具有与电网电压n倍频或n分频同步、THD小、幅值可调但不受电网电压波动的影响、简单实用、价格低廉等优点。

4)试验结果与理论分析一致。

上一篇:用MC9S12H256实现异步电机变频调速

下一篇:微机控制高速平缝机两个重要硬件系统的设计

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 HCPL-7820OPTION500

HCPL-7820OPTION500

京公网安备 11010802033920号

京公网安备 11010802033920号