1 数字前端

该低功耗数字接收机主要是针对语音信号的,要处理的信号都是窄带的。对数字前端中的混频器送出的模拟窄带中频信号进行采样,产生数字窄带中频信号。对该信号进行解调之前,先将频谱搬至零中频处,再进行滤波,降采样率等处理,如图1所示。

图1中A/D表示模数转换器,LPF表示低通滤波器,fs表示采样率,fo表示最靠近零频处镜像的中频。其中LPF实现如图2所示的功能。设滤出的复数信号采样率降为f's=fs/M。

图2中,细线表示上边带(USB),粗线表示下边带(LSB)。

说明一点,在实际中,上下边带的位置关系要根据模拟信号的中频及采样率fs才能确定,这里为了方便解释,就认为LSB在左,USB在右。

2 解调方案一

以解调上边带为例,如图3所示,设计一个数字带通滤波器,其频响关于中心频率fo'对称, 别为f3,f4,截止频率处的衰减至少为-20 dB。

别为f3,f4,截止频率处的衰减至少为-20 dB。

该带通滤波器的设计步骤如下:

(1)先设计一个低通滤波器,通带带宽为Δf1=f2-f1,过渡带带宽为Δf2=f1-f3。估算滤波器阶数:N=

(2)将上述的低通滤波器进行频谱搬移即可实现该带通滤波器(BPF),如图5所示。因此滤波器系数:

(3)如果利用FIRS指令实现边带滤波器,那么边带滤波的执行时间会降为原来的一半。但这时要求滤波器的系数是对称的。前面提到的低通滤波器系数是对称的。

为使带通滤波器的系数对称,我们将带通滤波器的系数附加一个相位△φ(n)。即:

的实部和虚部均为正。所以,带通滤波器的系数有这样的特点:实部偶对称,虚部奇对称。

3 解调方案二

还是以解调上边带为例,先搬移待解调信号的频谱,再做低通滤波,最后又将信号的频谱搬移回来,如图7所示。这种方案滤波器的设计思路简单,但要对信号进行两次频谱搬移。

LPF与方案一中所设计的低通滤波器相同。如图8所示,信号被搬至零中频处。

4两种方案的比较

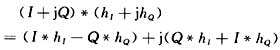

方案一中,带通滤波器在一个时钟周期内进行如下的计算:

其中"*"表示卷积运算,下同。这表示要做4N次乘加运算,考虑到对称性只需要2N次乘加运算。

如果信号不是独立边带的,上边带信号解调所用的带通滤波器的系数与下边带信号解调所用的带通滤波器的系数是共轭关系,即hUSB(n)=hLSB*(n),则另外一个边带的滤波计算为:

其结果与前面的成共轭关系,因此,只要得到其中一个边带的实数部分即可得到解调结果。这样只需要N次乘加运算。

如果是独立边带的,上下边带的共轭关系不存在,则解调其中一个边带需要2N次乘加运算,上下边带解调共需要4N次乘加运算。

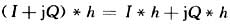

方案二中,低通滤波器在一个时钟周期内进行如下的计算:

这表示要做2N次乘加运算,考虑到对称性只需要N次乘加运算。

如果信号不是独立边带的,那么同方案一,只需要N/2次乘加运算。如果信号是独立边带的那就上下边带解调共需要2N次乘加运算。

另外两次经过NCO的运算在一个时钟周期内共需要8次乘加运算。

综合来说,就运算开销方面而言方案二要优于方案一。

关键字:混频 频谱 滤波 采样

引用地址:

基于DSP的低功耗接收机单边带解调方法

推荐阅读最新更新时间:2024-05-13 18:17

STM32 ADC 采样 频率的确定

一 STM32 ADC 采样 频率的确定 1. : 先看一些资料,确定一下ADC 的时钟: (1),由时钟控制器提供的ADCCLK 时钟和PCLK2(APB2 时钟)同步。CLK 控制器为ADC 时钟提供一个专用的可编程预分频器。 (2) 一般情况下在程序 中将 PCLK2 时钟设为 与系统时钟 相同 /* HCLK = SYSCLK */ RCC_HCLKConfig(RCC_SYSCLK_Div1); /* PCLK2 = HCLK */ RCC_PCLK2Config(RCC_HCLK_Div1); /* PCLK1 = HCLK/2 */ RCC_PCLK1Config(RCC_HCL

[单片机]

浅析高频谱仪的幅度测量精度方案

扫频式超外差频谱仪通过混频器把输入信号变换到中频(IF),在中频进行放大、滤波和检波处理。预选滤波器(有时是低通滤波器)主要用于滤除镜像频率的信号,频谱仪屏幕上显示的参考电平和中频放大器的增益有关,该放大器只是调节信号在屏幕上显示的垂直位置,不影响输入衰减器端的电平。屏幕的横轴是频率,纵轴是测得的信号电平,一般以线形的电压Volt或对数形式的dB表示。 频谱仪的幅度精确度通常有绝对精度和相对精度两种。绝对精度指的是信号的功率电平精度,单位为dBm;而相对精度指的是测量两个信号之间差值的精度,其中的一个信号作为另一个的参考,例如测量谐波信号的时候,一般测量谐波和基波的功率比。通过测量一个幅度和频率非常准确的校准源,以上两种精度都

[测试测量]

Triarchy usb频谱仪的特点

USB微型频谱分析仪(USB mini Spectrum Analyzer) 是一种基于PC的超小型频谱分析仪。它外观极小——只有一个U盘大小,重量极轻——只有20g ,但是只要通过USB接口与计算机相连,立刻就 变成 了一台真正的频谱分析仪。 目前公司产品有TSA4G1,TSA6G1,TSA12G5,频率可达到12.5GHz 输入平:-110dBm~+30dBm 1,外形小巧,重量不到 1 磅,占用很少桌面空间,方便拿在手中以及放在包、口袋或工具带里。 2、它与功能全面的 SignalVu-PC 信号分析软件(现可免费下载)配合使用。 功能强大 – 实时分析功能,频率覆盖范围为 9 kHz 至 6.2 GHz 经济实惠

[测试测量]

“中国纳米谷”5G射频滤波器二期项目扩产动工

2月21日,黄埔区、广州开发区举办“奋进‘十四五’启航新征程—第一季度重大项目集中签约动工活动”。活动上,72个新投资动工项目、31个签约项目进行了集中展示,涵盖战略性新兴产业、集成电路、新型显示等类别。 其中,在集成电路领域,胜科纳米将在知识城建立国内最顶尖的半导体分析测试平台,开展芯片材料、可靠性等检测服务,填补集成电路检测的重要一环。 由中国科学院院士赵宇亮领衔的“中国纳米谷”重磅项目5G射频滤波器也在当天迎来二期扩产动工。项目拥有滤波器自主知识产权,建设包括晶圆前道、后道产线,将进一步扩大生产5G声表面波滤波器,助力解决5G通信射频前端的国家关键技术问题。 此外,富乐德在该区启动建设半导体及TFT设备精密再生修复工厂,

[手机便携]

采用LC滤波的大功率本安Buck开关变换器

引言 随着对大功率低电压本安电源的需求增大,基本本安Buck变换器就需要进一步提高输出功率。但是要想提高输出功率,增大输出电流,可以使变换器输出端电感电容的容量增加,但是这样很容易引燃爆炸性气体,降低本质安全性能;再者可以通过提高开关频率来实现,一方面能够减小为满足输出纹波电压要求所需的电感和电容取值,因此也有利于本质安全,但另一方面提高开关频率却降低了变换器的效率,导致最大电感电流增大而不利于本质安全。此外提高开关频率还可能导致电容器的实际有效容量显著下降而影响滤波效果,并且过高的开关频率不仅不易实现,而且电路稳定性也会受影响。为此,本文提出在基本本安Buck变换器输出端采用LC滤波电路的思想,使得本安Buck变换器在小电

[模拟电子]

频谱分析仪的参数和性能指标的含义了解

射频和微波频谱分析仪甚至在原理上也是不简单的。将这两种频谱分析仪称为校正的超外差接收机仅能反映它们有什么功能及如何实现这些功能。如将它们称为频域示波器,则反映的内容就更少了。此外,如果只是走马观花地看一看这项技术,那你就会得出错误的结论:在过去十年里,射频和微波频谱分析仪没有多大变化。然而,在迅猛发展的无线技术领域,能够显示频率高达3GHz以上——常常达到7GHz,有时达到20GHz--信号的频谱分析仪事实上正在发生重大变化,其重要性也正在大大提高。 更糟糕的是,为某项任务选择最为合适的分析仪可能是个很大的难题,当你的上司不明白这一选择过程为什么不只是对一两份制造商产品说明书上的价格和一些参数进行比较而已时,尤其是这样。对于以

[测试测量]

网络分析仪与采样示波器TDR的优势比较

序言 最近几年随着多Gbps传输的普及,数字通信标准的比特率也在迅速提升。例如, USB 3.0的比特率达到 5 Gbps。比特率的提高使得在传统数字系统中不曾见过的问题显现了出来。诸如反射和损耗的问题会造成数字信号失真,导致出现误码。另外由于保证器件正确工作的可接受时间裕量不断减少,信号路径上的时序偏差问题变得非常重要。杂散电容所产生的辐射电磁波和耦合会导致串扰,使器件工作出现错误。随着电路越来越小、越来越紧密,这一问题也就越来越明显。更糟糕的是,电源电压的降低将会导致信噪比降低,使器件的工作更容易受到噪声的影响。尽管这些问题增加了数字电路设计的难度,但是设计人员在缩短开发时间上受到的压力丝毫没有减轻。 随着比特率的提高,

[测试测量]

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器

IIR数字滤波器设计-在FPGA上实现任意阶IIR数字滤波器 摘 要:本文介绍了一种采用级联结构在FPGA上实现任意阶IIR数字滤波器的方法。此设计扩展性好,便于调节滤波器的性能,可以根据不同的要求在不同规模的FPGA上加以实现。 IIR数字滤波器在很多领域中有着广阔的应用。与FIR数字滤波器相比,它可以用较低的阶数获得高选择性,所用存储单元少,经济而效率高,在相同门级规模和相同时钟速度下可以提供更好的带外衰减特性。下面介绍一种在FPGA上实现IIR数字滤波器的方法。 IIR数字滤波器的结构 任意阶的IIR滤波器可通过数学分解,表示为: 其中为如下的二阶形式: 这样就可以将任意阶的IIR滤波器通过若干二阶网

[嵌入式]

别为f3,f4,截止频率处的衰减至少为-20 dB。

别为f3,f4,截止频率处的衰减至少为-20 dB。

汽车用磁性材料-共模滤波电感

汽车用磁性材料-共模滤波电感 ICCV2023论文汇总:Deep Learning Architectures and Techniques(深度学习架构与技术)

ICCV2023论文汇总:Deep Learning Architectures and Techniques(深度学习架构与技术)

京公网安备 11010802033920号

京公网安备 11010802033920号