引言

随着CMOS(互补金属氧化物半导体)技术的发展及市场需求的增加,CMOS图像传感器得以迅速发展。由于采用了CMOS技术,可以将像素阵列与外围支持电路(如图像传感器核心、单一时钟、所有的时序逻辑、可编程功能和A/D转换器)集成在同一块芯片上。与CCD(电容耦合器件)图像传感器相比,CMOS图像传感器将整个图像系统集成在一块芯片上,具有体积小、重量轻、功耗低、编程方便、易于控制等优点,因此,CMOS图像传感器的应用已经变得越来越广泛。

但是,目前市场上的大部分基于CMOS图像传感器的图像采集系统都是采用DSP与图像传感器相连,由DSP来控制图像传感器,然后由DSP采集到图像后再通过USB接口将图像数据传输到PC机进行后续的处理。这样的图像采集系统成本较高,功耗大,而且体积上也有一定的限制,并不适合一些简单的应用。

本文设计了一种基于S3C2410的CMOS图像传感器数据采集系统。该系统成本更为低廉、结构更为简单、设计更为新颖。

1 CMOS图像传感器结构性能及工作原理

该系统选用OmniVision公司的OV7141黑白CMOS数字图像传感器。OV7620是一款单片VGA模式黑白数字像机芯片,具有640×480=307 200像素,最高可以30帧/s的速度输出数字图像数据。具有高灵敏度、宽动态范围、抗开花、零光晕等特点,所有的图像特性参数如曝光量、增益、白平衡、帧频、输出图像数据格式、图像时序信号极性、窗口大小及位置等,都可以通过SCCB接口进行设置,并可立刻生效。

OV7141的主要特性参数如下:图像尺寸为3.6 mm×2.7 mm;像素尺寸为5.6μm×5.6μm;像素数为640×480像素(VGA),320×240像素(QVGA);信噪比>46 dB;最小照度为3.0 V/(Lux·s);暗电流为30 mV/s;动态范围为62 dB;电源为DC 3.3 V和DC 2.5V;功耗为40 mW(工作),30μA(休眠)。

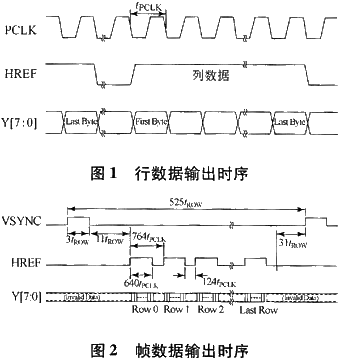

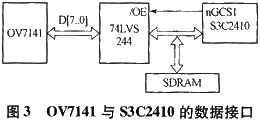

CMOS镜像阵列的设计主要建立在逐行传送的扫描场读出系统和带同步像素读出电路的电子快门之上。而电子曝光控制算法(或系统规则)则建立在整个图(物)像亮度基础之上。在景像(或布景)正常时,一般曝光都比较理想。但在景像光线不适当时,则应通过AEC(自动曝光控制)白/黑比调节来使其满足应用要求。图像采集窗口可以任意设定,数据输出方式可以选择逐行工作模式或隔行工作模式。OV7141内部嵌入了一个8位A/D转换器,因而可以同步输出8位的数字视频流D[7…0]。在输出数字视频流的同时,还可提供像素同步时钟PCLK,水平参考信号HREF以及帧同步信号VSYNC,以方便外部电路读取图像。像素数据输出与PCLK、HREF、VSYNC的时序关系如图1和图2所示。

2 S3C2410简介

Samsung公司推出的16/32位RISC处理器S3C2410,为手持设备和一般类型应用提供了低价格、低功耗、高性能小型微控制器的解决方案。为了降低整个系统的成本,S3C2410提供了以下丰富的内部设备:分开的指令Cache和数据Cache,内带MMU、LCD控制器(支持STN&TFT),支持NAND Flash系统引导,系统管理器(片选逻辑和SDRAM控制器),3通道UART,4通道DMA(直接存储器存取),4通道PWM(脉宽调制)定时器,I/O端口,RTC,8通道10位A/D转换器和触摸屏接口,IIC-BUS接口,USB主机,USB设备,SD主卡和MMC卡接口,2通道的SPI以及内部PLL(锁相环)时钟倍频器。

3 CMOS图像传感器与控制器接口电路设计

接口电路的设计主要应考虑CMOS图像传感器与控制器S3C2410的数据输出电路接口、控制电路接口以及IIC总线接口。

3.1 数据接口模块

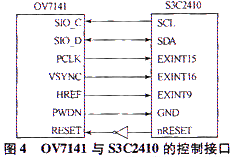

由于CMOS图像传感器的每一个成像单元像DRAM内存的存储单元一样被单独编址,且OV7141内部嵌入了一个8位A/D转换器,因而可以同步输出8位的数字视频流D[7…0]。因此,与其数据线连接就和DRAM一样,将数据线和S3C2410的数据总线直接连接即可。线路连接如图3所示。

但CMOS图像传感器也有与内存不同的地方:内存在计算机系统中总是作为一个从设备来对待,只有控制器对其进行读写操作时它才打开数据总线,其他时刻为断开状态(高阻态);而OV7141图像传感器一旦开始采集图像数据,它根本不管系统中的主控制器是否对其进行读写操作,总是按照它自己的时序向其数据总线输出数据,这样就可能造成数据总线的冲突问题。为了避免这种总线冲突问题,需要在系统控制器的数据总线与OV7141图像传感器的数据总线之间接入一个具有三态功能的总线驱动器,该驱动器的使能端/OE由S3C2410的存储器单元片选信号nGCS1来选通,这样,控制器S3C2410对图像传感器的读写就如同读写内存一样。

3.2 控制接口模块

当CMOS图像传感器工作于逐行扫描方式时,在输出一帧同步信号后将输出一帧的数据,在每一行数据前也会输出行同步信号,每一个像素有效信号触发一个点的信号输出,输出有效窗口由HREF信号决定。由图1、图2可知,帧同步信号VSYNC标示一帧数据的开始。然后,在每一个PCLK信号的作用下,传感器顺序地从左到右依次输出每一个像素数据。当输出的像素数据为有效数据时,HREF为有效电平。当一帧的所有数据都输出后,则又产生一个帧同步信号VSYNC,开始下一帧数据的传输。根据以上时序图的特定,可以采用DMA的传送方式来实现图像传感器到DRAM的数据传输。可以使用帧同步信号VSYNC来作为主控制器的一个中断输入信号,以初始化DMA控制器,用水平同步信号HREF作为一个外部中断输入信号,以统计每行数据的输出,用输出数据同步信号PCLK作为DMA传送的请求信号(Request),以请求传输一个像素的数据信息。连接电路如图4所示。

3.3 IIC总线接口模块

CMOS图像传感器目前普遍采用IIC总线功能集中的一个子集,因此该接口比一个完整的主IIC总线更简单。硬件连接只需将OV7141的SIO_C、SIO_D分别与S3C2410的SCL、SDA相连皆可,见图4。

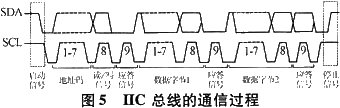

IIC总线由双向数据线SDA和时钟线SCL组成,用户使用集电极开路门以“线与”方式进行总线连接。IIC总线的通信协议见图5,包括开始信号、结束信号、应答信号和数据有效等状态。当SCL持续为高电平时,SDA由“1”跳变到“0”,表示开始信号;当SCL持续为高电平时,SDA由“0”跳变到“1”,表示结束信号;在数据传输过程中,SDA在时钟高电平时有效,低电平时更换数据。开始和结束信号均由主IIC产生,通过SDA传输的数据以字节(8 bit)为单位,高位在前,低位在后,在每个字节后面由接收端发送一个低电平的应答信号。

其读写周期如下:当要进行IIC总线写操作时,先发送所使用的CMOS传感器特定ID写地址,紧接着发送需要写的寄存器的地址(sub_address),再发送数据(data);当进行IIC总线读操作时,先发送所使用的CMOS传感器特定ID写地址,紧接着发送需要写的寄存器的地址(sub_address),再发送CMOS传感器特定ID读地址,最后接收数据(data)。对于不同的CMOS传感器,它们的ID地址是不同的。OV7141为42H(写),43H(读)。

4 CMOS图像传感器的软件驱动设计

CMOS图像传感器需要控制器S3C2410的驱动才能正常工作,并输出正确的图像数据。为了实现CMOS传感器和主存储器(DRAM)之间的快速传输,可以采用DMA方式。DMA是一种快速传送数据的机制,它不需要CPU的参与而实现高速外设和主存储器之间自动成批交换数据的操作方式。由于处理端采用的是S3C2410,DMA、中断以及IIC总线接口都已经集成在控制器内部,因此,整个软件驱动只需要完成两个功能模块的设置:对主控制器S3C2410的设置;通过SCCB口对OV7141的设置。

4.1 对主控制器S3C2410的设置

a) 设置DMA的源地址为控制总线驱动器的那一个地址,每一次传输该地址值不变化;

b) 设置DMA的目标地址为要保存图像数据的内存区域的起始地址,每一次传输该值加1;

c) 设置DMA的计数器为有效窗口的像素数的个数;

d) 设置DMA中断为软件触发,且设置PCLK、VSYNC、HREF为外部中断触发信号,以控制图像数据的输出。

4.2 通过SCCB接口对OV7141的设置

a) 读OV7141的1C、1D寄存器,判断芯片是否正常;

b) 设置13寄存器为0x07,允许AGC,允许白平衡;

c) 设置14寄存器为0x00,设置有效窗口为640×480像素(VGA);

d) 设置17、18、19、lA寄存器,设置HREF和VSYNC信号的起始与停止;

e) 设置28寄存器为0x60,设置为黑白模式和逐行扫描模式。

5 实验与讨论

本系统中,图像传感器的时钟由外接24 MHz的晶振供给,主控制器S3C2410工作频率为200 MHz,CMOS图像传感器OV7141工作于逐行扫描方式,图像采集窗口为640×480像素,数据保存在系统中一片SDRAM中。实验表明,系统每秒能稳定采集到15帧图像数据。若要提高图像采集的速率,可以再加入一块双端口SDRAM作为数据输出缓存,这样速率有所提高,但双端口SDRAM价格较贵,或者选用能工作于更高工作频率的主控制器也能提高采集速率。

本设计是基于32位处理器的嵌入式图像采集系统。设计中直接将主控制器S3C2410与图像传感器连接,再加上一些存储芯片,构成一个简单的图像采集系统,因而与其他大多数基于PC机的图像采集系统相比具有结构简单、成本低、体积小、功耗低、通用性好等优点,特别适合一些对体积、成本、功耗有较高要求的应用,如目前市场上的指纹识别系统等。因此,该系统具有广泛的应用价值和一定的研究意义。

上一篇:基于加速度传感器的低功耗冲击记录仪的实现

下一篇:一种改进的图像重组算法及其硬件实现

推荐阅读最新更新时间:2024-05-13 18:37

- 热门资源推荐

- 热门放大器推荐

-

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 -

浅谈电子技术在汽车自动控制中的应用

浅谈电子技术在汽车自动控制中的应用 -

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐 -

ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟)

ICCV2023论文汇总:Embodied Vision: Active Agents, Simulation(具身视觉:主动代理、模拟) -

嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练 -

东芝1200V SIC SBD “TRSxxx120Hx系列” 助力工业电源设备高效

东芝1200V SIC SBD “TRSxxx120Hx系列” 助力工业电源设备高效 -

一起来学Cadence Allegro高速PCB设计

一起来学Cadence Allegro高速PCB设计 -

5G+MEC+V2X车联网解决方案白皮书

5G+MEC+V2X车联网解决方案白皮书

整车控制策略开发需求分析及新能源汽车动力总成测试系统

整车控制策略开发需求分析及新能源汽车动力总成测试系统 ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐

ICCV2023论文汇总:Fairness, Privacy, Ethics, Social-good, Transparency, Accountability in Vision(视觉中的公平、隐 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号