概要

该项目的目标是设计一个高效电源系统,其输出电压(VOUT)可以数字调节。为了保证输出电压的精确性,采用数字闭环控制,用于修正失调、漂移和负载变化(最大至600mA)的影响。电路包括输出可调的降压型控制器、ADC与DAC、电压基准以及一个微控制器(MCU)。

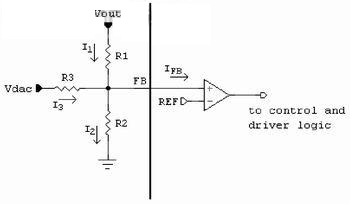

在大多数DC-DC转换器中,位于FB引脚上的电阻网络可以调整转换器的输出电压(见图1)。在本文电路中,利用DAC输出电压(VDAC)改变电阻网路的基准电压,达到调整转换器输出(VOUT)的目的。ADC检测输出电压,并将结果送入微处理器。微处理器调整DAC输出,以控制系统输出电压达到预定值。为使电路尽可能简单,预设输出电压通过PC的串行通信口(RS-232)送入微处理器。这个系统在一些需要精确控制供电电压的嵌入式系统中非常有用。例如为ASIC、DSP或者MCU供电的电源,电源电压对应于处理器的工作速率。将供电电压调整到工作速率对应的最小电压,可以降低处理器功耗。

图1

电路所需器件和开发工具

系统的主电源选择低静态电流、输出1.25V~5.5V可调的降压型调节器MAX1692,它可以提供最大600mA的电流。MAX1692评估板提供了一个经过验证的电路布局和推荐输入电容、输出电容和电感量。MAX1692反馈引脚电阻网络的偏置由低功耗、12位DAC提供,MAX5302可以提供2.5mA的负载驱动。DAC基准电压为2.5V。电压调节器输出电压由低功耗、12位ADC(MAX1286)读取, MAX1286能自动关断,可以在转换之间减少电源消耗。ADC基准由高精度5V电压基准MAX6126 提供。ADC和DAC均采用SPI口通信。高精度电压基准包括输出检测和地检测引脚,将其连接到ADC的基准和地引脚。这样可以保证ADC具有最高准度的基准电压。

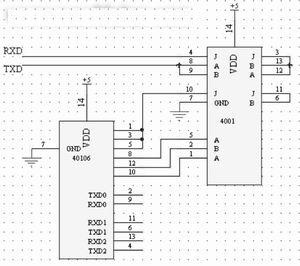

图2 供电系统的模拟部分产生一路负载可达600mA、1.25V~5V可调的高准确度输出电压

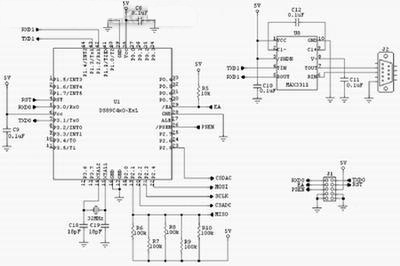

微处理器选择高速的8051兼容微处理器DS89C420,使用32MHz晶体。该微处理器的绝大多数指令为单指令周期,可以运行在32MIPS。处理器可以由J1口在线编程(见图3)。DS89C420/430/440/450系列用户手册介绍了如何通过PC串行通信口,利用微软的超级终端(HyperTermina)下载固件。处理器固件用C编写并可使用免费的Sourceforge Small Devices C编译器(SDCC)编译。

图3 供电系统的数字部分需要一个稳定的5V电源(与模拟部分共用),数字部分通过逐位控制的SPI接口与DAC、ADC通信。串行收发器(U8)从PC接收VOUT设定值,J1提供MCU的在线编程。

模拟电路设计

为计算电阻网络中的R1、R2和R3 (见图2),先假设流入FB引脚的电流(IFB)可以忽略(MAX1692规格表给出的最大值为50nA),设R2为49.9kΩ。FB引脚电压为1.25V,电流I2为25mA,远高于50nA,证明忽略IFB的决定是正确的。最后,计算R1和R2:

(1)

DAC输出电压(VDAC)为最大值2.5V时,降压调节器的输出(VOUT)应该为最小值1.25V。代入式1:

第一项为零,得到R3为50 kΩ。当VDAC 为最小值0V时, VOUT 应该为最大值5V。代入式1 :

得到R1值为75kΩ。

ADC采集VOUT并将其通过SPI接口传送给MCU,形成闭环数字控制。

数字电路设计

DAC和ADC由逐位控制的SPI总线和MCU通信。MCU是主器件,而DAC和ADC是从器件。MCU的5个引脚分别作为SCLK、MOSI、MISO、CSADC(ADC片选)、CSDAC(DAC片选)。总线上的器件共用SCLK,为达到最高通信速度,使用32MHz的晶体供给MCU系统时钟。MCU通过PC串口接收VOUT值。MAX3311是RS-232收发器,将RS-232电平转为TTL/COMS电平。

布局考虑

使用宽的引线连接所有无源器件(旁路电容、补偿电容、输入电容、输出电容和电感)与降压转换器。这些元件和FB引脚的电阻网络应尽可能靠近降压转换器,以减小PCB引线电阻和噪声干扰。降压转换器处需要大面积的覆铜,以降低IC在重负载下的工作温度。可以参考MAX1692评估板。为保持信号完整性,必须尽可能将模拟信号线和数字信号线隔离开。将DAC和ADC靠近降压器放置,用短线连接所有模拟信号。数字信号在另一方向连接到MCU。尽可能将电压基准靠近ADC,提供电压基准的电压反馈线用较短的隔离线连接到ADC的REF 和GND引脚,以保证ADC的转换精度。

必须确保MCU下方没有高速信号线。同时,32MHz时钟晶体尽可能靠近MCU的输入引脚。如同所有PCB布线一样,不允许存在90°引线转角,所有IC电源都用0.1μF陶瓷电容旁路,并且尽可能地靠近供电引脚安装。

软件

本系统MCU软件通过PC串口获取要设定的VOUT,对应由ADC采样得到的降压转换器输出电压。由于MCU是8位总线,而ADC是12位分辨率,将字节左移4位(相当于乘以16),4位最低有效位置零。软件用C编写,可从Maxim网站下载。

测试结果

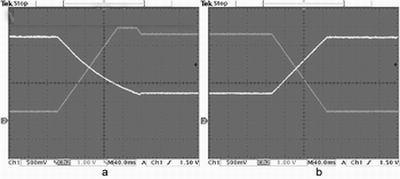

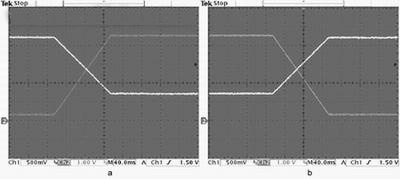

即便是满负载,该系统也可以正确地将转换器的输出电压控制在设定电压的1% 误差内。由ADC得到的反馈可以补偿负载变化、失调和输出电压漂移,以准确控制输出电压。图4a和图4b是电源电压在1mA负载时的性能,图5a表示VOUT和VDAC在VOUT 由4.5V转变到1.5V时的变化,图5b为VOUT和VDAC在VOUT 由1.5V转变到4.5V时的变化。从中可以看出VOUT的下降速率比上升速率慢很多。这是由于输出大电容放电所致(见图2的C16)。转换器可以非常快地对电容充电,但负载没有办法使电容快速放电。注意电压的变化速率非常接近,因为350mA负载可以使电容足够快地放电。这样,一个足够大的负载可以使VOUT以同样速率增加或减小。

图4 波形显示了负载电流为1mA时,降压转换器输出电压(VOUT)和DAC的输出电压(VDAC)。图a为VOUT从4.5V到1.5V变化时的VOUT和VDAC波形;图b为VOUT从1.5V到4.5V变化时的VOUT 和 VDAC波形

图5. 波形显示了负载电流为350mA时,降压转换器输出电压(VOUT)和DAC的输出电压(VDAC)。图a为VOUT从4.5V到1.5V变化时的VOUT和VDAC波形;图b为VOUT从1.5V到4.5V变化时的VOUT 和 VDAC波形

虽然电压可以准确控制,但测试结果也提醒我们系统存在的某些问题,图4a显示反馈系统会上冲或下冲。这是由软件程序循环的占用时间引起的。图4a显示VOUT达到设定值之前,VDAC增大到它的最大值。当VOUT最后达到设定值,VDAC必须减小,降低DAC输出电压需要时间,这导致VOUT下冲。理想情况下,VDAC必须和VOUT以同样速度变化,但是,在系统负载达到一定水平之前无法实现这一平衡。该系统需要100μs,用以调整大的输出电压变化,因为软件需要在ADC采样后逐位改变VDAC。为了使VOUT从5V变到1.25V,MCU必须让12位DAC的电压增加4,095次,同时对VOUT 采样4,095次,每次ADC采样都需要耗费采样时间和转换时间。

上一篇:一种基于单片机的太阳能电池发电量监控系统

下一篇:锂离子电池的修复仪的设计方案

推荐阅读最新更新时间:2023-10-18 14:57

![[组图]300V电子管稳压<font color='red'>电源</font>](https://6.eewimg.cn/news/statics/images/loading.gif)

Vishay线上图书馆

- 选型-汽车级表面贴装和通孔超快整流器

- 你知道吗?DC-LINK电容在高湿条件下具有高度稳定性

- microBUCK和microBRICK直流/直流稳压器解决方案

- SOP-4小型封装光伏MOSFET驱动器VOMDA1271

- 使用薄膜、大功率、背接触式电阻的优势

- SQJQ140E车规级N沟道40V MOSFET

西电-印刷电路板(PCB)设计指南_1-99

西电-印刷电路板(PCB)设计指南_1-99 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号