1、引言

目前,电荷泵锁相环是所有锁相环中最受关注的一种,例如它在射频的频率合成器、数字电路中的时钟产生以及时钟恢复电路中都被广泛采用,这主要是因为电荷泵锁相环具有良好的跟踪能力和捕获能力。研究开发性能良好的电荷泵锁相环有着重要的现实意义[1]。同时,CMOS工艺具有工作电压范围宽、静态功耗低、抗干扰能力强等优点,是当今集成电路制造业的主流工艺[2]。因此,使用CMOS工艺设计的锁相环路应用范围越来越广,而电荷泵是电荷泵锁相环里面除VCO外最重要的电路模块,而电流失配、电荷共享、过冲和时钟馈通等现象一直限制着电荷泵性能的提高[3],因此研究性能良好的电荷泵有非常重要的现实意义。

2、传统电荷泵

2.1基本原理

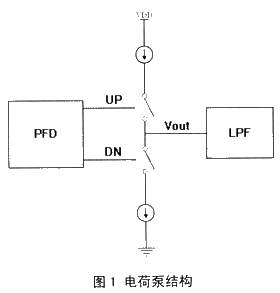

图l是典型的电荷泵结构。此处电荷泵为两个受鉴频鉴相器(PFD)输出信号控制的开关电流源,它与后面的环路滤波器共同作用,将PFD的逻辑信号转化为电压信号,该电压信号进而调节压控振荡器的振荡频率[4]。

当鉴频鉴相器输出电压信号UP为高时,电荷泵上端开关导通,电荷泵将以电流Ip对滤波器充电。

当鉴频鉴相器输出电压信号DN为高,打开电荷泵下端开关,电荷泵以电流Ip对滤波器放电。因为这种结构的鉴频鉴相器通过电流充、放电来改变低通滤波器的电压Vout所以对Vout电压幅值没有限制。因此电荷泵锁相环的捕获范围很宽,直接由压控振荡器能够工作的频率范围来决定。同时,当电荷泵上下的开关都关断时,低通滤波器的电压可以保持Vout不变,而且UP和DN信号表征的是输入与输出之间的相差,UP和DN均为低电平说明鉴频鉴相器的输出相差为0。所以,这种结构的电荷泵和鉴频鉴相器具有锁定时相差为0的优点。

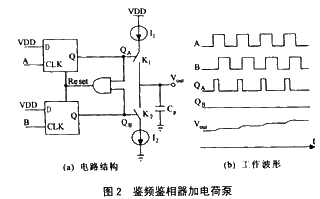

当鉴频鉴相器和电荷泵一同使用时,电路结构如图2所示。电路有充电、放电和保持三种状态。当QA=QB=0时,K1和K2关断,保持Vout不变。如果QA为高,QB为低,电容Cp通过I1充电。反之,如果QA为低,QB为高,Cp通过I2放电。因此,如果A超前B,QA连续产生脉冲,Vout值逐渐升高,呈阶梯形。I1和I2就分别为上述的UP和DOWN电流,通常取一样的值[5]。虽然电路能正常工作,但也产生了下述的电荷共享问题。

2.2"电荷共享"问题

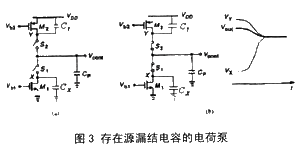

电荷泵的"电荷共享"是电荷泵的主要问题之一,问题来源于电流源漏端所存在的一定的电容间。其原理如图3所示,开关S1和S2都断开,那么M1使结点X放电到零电位,M2使结点Y充电到VDD。在下一个相位比较瞬间,开关S1和S2都导通,从而Vx的电压上升,Vy电压下降,如果忽略在开关S1和S2上的电压降,则有Vx一Vy一Vcont(图b),如果相位误差为零,而且且ID1=|ID2|,则在开关导通时,Vcont值将发生跳变。此时即使Cx=CY,VX和VY的变化量也不相等。例如,若Vcont比较高,则Vx变化量大而Vy变化量较小。这两者变化的差额必须由Cp来提供,从而导致Vcont跳动[7]。

3. 抑制"电荷共享"的方法

上述电荷共享现象可以通过"自举"(bootstrapping)的办法来消除[8]。

如图4所示,其思路就是在相位比较完后,将VX和VY的电位"固定"到Vcont。当S1和S2断开时,S3和S4导通,再用单位增益放大器将结点X和Y的电位保持在Vcont,在下一个相位比较瞬间,S1和S2导通,S3和S4断开,这时候VX和VY的电位都等于Vcont,所以在CP和X点、Y点的电容之间不会发生电荷共享。而新型低电荷共享的电荷泵就是这种结构的具体电路实现。

4、低电荷共享的新型电荷泵

图5是本文提出的新型电荷泵电路,它将单一晶体管的开关改为双向传输门,这使电流传输不受晶体管阈值电压的影响,并可扩大X、Y两点的电压跟随范围。用一个单端放大器构成负反馈,形成电压跟随器,偏置电流源同时为放大器提供尾电流。改进后的电荷泵同一般的电荷泵相比,多了一个跟随器,这个跟随器使得电流源在关断时,漏端电压能够跟随Vcont,这样当开关打开时,可以认为△v等于零,同时避免了两个电流源漏端寄生电容的电荷共享效应。否则会引起较大的上下电流不对称效应,增大锁相环的抖动。

5、传统电荷泵和新型电荷泵的对比

对比仿真采用GSMC0.18Dμm工艺库,在相同的尺寸和各种工艺角 TT、FF、SS,供电电压1.8v10%,温度0℃到125℃等仿真条件下进行,仿真软件为spectre和hspice。这里的传统电荷泵结构仅比上述的新型电荷泵少了右边的差动放大器。通过观察CPLL锁定时的压控振荡器的控制电压Vcont的波纹大小可初步比较得出电荷泵的性能,由于两者的抖动在本次中都很小(10ps数量级),所以肉眼不能从时钟信号观察出来。从图6和图7可以看出新型电荷泵的Vcont波纹的振幅约为4mV,仅为传统的电荷泵的振幅12mV的l/3,这减少的量主要是从抑制电荷共享而获得,另外两个波纹产生的原因是时钟馈通和电流过冲。更小的波纹将导致CPPLL的更小的抖动。

从表1的仿真结果可以知道,新型电荷泵由于结构上的改进,得到了比传统电荷泵更小的抖动和失配,由于增加了电压跟随电路,功耗会大一点.

我们阐述了一个低失配(mismatch2%)、低电荷共享的新型电荷泵,通过增加并不复杂的电路达到了加倍提高电荷泵性能的目的,这种电荷可广泛用于CPPLL中.

上一篇:如何选择合适的(变)电站用直流电源屏

下一篇:一种用于白光LED驱动的电荷泵电路设计

推荐阅读最新更新时间:2023-10-18 14:39

Vishay线上图书馆

- 选型-汽车级表面贴装和通孔超快整流器

- 你知道吗?DC-LINK电容在高湿条件下具有高度稳定性

- microBUCK和microBRICK直流/直流稳压器解决方案

- SOP-4小型封装光伏MOSFET驱动器VOMDA1271

- 使用薄膜、大功率、背接触式电阻的优势

- SQJQ140E车规级N沟道40V MOSFET

西电-印刷电路板(PCB)设计指南_1-99

西电-印刷电路板(PCB)设计指南_1-99 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号