在使用DSP进行数字信号处理时,应用过采样技术可以增加其内置模数转换器的分辨率。讨论了应用过采样技术的原理、如何使用TMS320LF2407来实现过采样,以及在软件上的实现方法。

关键词:过采样,抗混叠滤波器,抽取,数字信号处理器

1 引 言

模数(AD)转换通常是数字信号处理应用中的第一步,依据应用的不同,对模数转换器(ADC)也有不同的要求,衡量模数转换器的最重要的标准是它的转换速率、分辨率和精度。应用过采样技术,再加上适当的数字滤波和抽取,就可以得到比原有的ADC更高的分辨率。

在数字信号处理器(DSP)中应用过采样技术需要快速ADC以非常快的速度来采样模拟信号,并且需要快速DSP来执行数字低通滤波和抽取。TI公司出品的DSP芯片TMS320LF2407采用3.3V供电,30MIPS的执行速度使得指令周期缩短至33ns,内置有10位的AD转换器,最小转换时间为500ns(详见TI公司的资料:TMS320LF/LC240x DSPController,Systemand Peripherals,2000),这些为在DSP中应用过采样技术创造了条件。

2 过采样降低对模拟抗混叠滤波器的限制

在采样过程中首要的问题是采样频率的选择,Nyquist采样定理指出:若连续信号x(t)是有限带宽的,其频谱的最高频率为fc,对x(t)采样时,若保证采样频率fs≥2fc,那么,就可由采样信号恢复出x(t)。在实际对x(t)作采样时,首先要了解x(t)的最高截止频率fc,以确定应选取的采样频率fs。若x(t)不是有限带宽的,在采样前应使用抗混叠(anti-aliasing)滤波器对x(t)作模拟滤波,以去掉f>fc的高频成分。

因此,在AD转换前就需要模拟低通滤波器具有尖锐的滚降特性,来限制模拟信号的频谱。一个理想的滤波器应能让所有低于fs/2的频率通过,而完全阻隔掉所有大于fs/2的频率。通常,滤波器和采样频率的选择是将我们感兴趣的频带限制在DC和fs/2之间。

用更高的采样频率可以降低对低通滤波器的限制,图1所示为以2倍的原采样频率对模拟信号进行采样,在这种情况下,滤波器的截频为fs/2,阻带的起始频率为fs,这样就可以让所有我们感兴趣的频率通过,而抑制掉所有高于fs的频率。但这样做违反了Nyquist采样定理,所以还需要用ADC后的数字滤波器来将信号的频率限制到fs/2以下。采用了过采样后的这种抗混迭滤波器可以得到简化,允许的通带到阻带的过渡区很宽。

3 过采样提高信噪比

经模拟滤波后,模拟信号被采样并转换成数字值,因为数字域仅包含有限的字长,若要用它来表示连续信号,就要引入量化误差,最大量化误差为±0.5LSB。因为一个N位的ADC的输入范围被分成2N个离散的数值,每一个数值由一个N位的二进制数表示,所以,ADC的输入范围和字长N是最大量化误差的一个直接表示,也是分辨率的一个直接表示。代表数字值的字长决定了信噪比,因此通过增加信噪比可以增加转换的分辨率。加入三角波信号可提高信噪比(详见TI公司的资料:Oversampling Techniques Using theTMS320C24x Family,June 1998)。

如果输入信号在两个量化步长q1与q0之间,则它将被量化成q1或q0。当增加一个适当的三角波信号,并高速采样,将会量化出一系列的q1与q0,这两个值出现的比例就代表了此输入信号在两个量化步长之间的相对位置。要应用这种方法得到比较好的效果,三角波信号的幅度必须为(n+0.5)LSB,其中,n=0,1,2,...。

因为有了高采样速率,输入信号的变化相对来说比较缓慢,图2中,输入信号为0.6 LSB,一个典型的AD转换器将采样这个信号并把它转换成1 LSB。当用一个三角波信号与此输入信号进行叠加,并高速采样时,转换器产生一系列的0或1采样值。0和1出现的比例就表示了这个在0和1 LSB之间的实际值。

图2中的采样因子K为16,采样值为0.563,得到了比原转换结果更小的量化误差。使用三角波调制过采样技术所增加的信噪比可以表示为:![]()

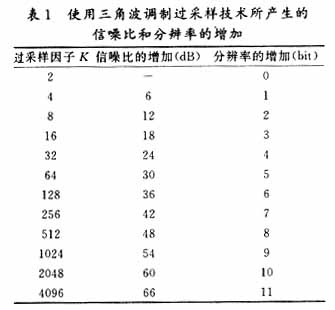

用该法产生的信噪比和分辨率的增加见表1。

使用增加三角波信号的过采样每加一倍过采样速率,就可以增加6 dB的分辨率。然而这种方法需要输入信号与三角波信号不相关,如果不能做到这一点,那信号在一个过采样周期内变化不能超过±0.5 LSB。

4 用TMS320LF2407来实现过采样

图3为利用TMS320LF2407来实现过采样,虚线框部分都可以用LF2407来实现。PWM信号输出可以用来产生三角波信号,数字滤波和抽取用软件来实现。

图4为三角波信号产生以及与输入信号叠加的电路图。PWM信号的占空比在0和100%之间。R3和C1作为积分器产生一个0到3V之间的三角波信号输入到运放。输出信号连至ADC的输入。

5 过采样的软件实现

实现过采样的DSP软件包括以下6个主要模块。

5.1 外设初始化

采用EVA模块的TIMER1来启动ADC转换并且提供PWM输出,TIMER1工作于连续增计数模式,周期寄存器的值等于AD转换速率,由周期匹配事件来启动AD转换。

5.2 三角波信号产生

由前面论述可知,三角波信号由PWM信号产生,PWM信号的占空比由编程TIMER1的比较寄存器(T1CMPR)决定。为了得到三角波信号,T1CMPR中的值需要由某一步长(STEP)来不断地增加和减少,而这一步长由定时器周期寄存器(T1PR)和过采样因子(K)决定,其计算公式如下:![]()

用一标志(FLAG)表示三角波的上升或下降,它用来决定比较寄存器中的值被STEP增加还是减少了。CURRENT代表当前定时器比较寄存器中的值。用软件改变PWM占空比的流程如图5所示。

5.3 数据采集

AD转换完成后产生中断,在中断服务子程序中读出每次转换的结果,作为数字低通滤波的输入。

5.4 数字滤波

采用FIR结构的滑动平均滤波器(MovingAverage Filter),滑动平均滤波器的Z变换为:![]()

从输入xi计算输出yi的表达式为:

5.5 抽取

抽取过程将以K倍来降低最后的数据率。一般来说,抽取操作是和数字滤波结合在一起的,即,只需在数字滤波中计算每K个输出值。

5.6 中断服务程序

在中断服务程序中执行以下几个操作:调整PWM占空比、读出AD转换值、数字滤波(其中包括抽取)。

6 结束语

本文从分析过采样的频谱特性出发,分析了过采样技术的原理、用DSP实现过采样的方法以及软件上的实现,随着DSP在各种信号处理领域中的广泛应用,过采样技术在其中的应用也将日益广泛,因此,本文也有助于进一步发展利用过采样技术。

上一篇:基于ADF4106的锁相环频率合成器

下一篇:动态调节系统参数,提高回声与噪声消除性能

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 LM218J-8

LM218J-8

京公网安备 11010802033920号

京公网安备 11010802033920号