摘要:与通常采用外围的CPLD器件和CPU来产生配置接口控制逻辑的方法不同,本文设计了采用嵌入到FPGA的Leon3开源CPU软核来控制实现Virtex系列FPGA的SelectMap接口配置的方法,可将其应用于对FPGA芯片的在线配置。该方法设计成本低,不局限于某一类型的FPGA芯片,减少了外围分立元件的使用,增强了设计的灵活性。仿真结果表明该设计满足SelectMap接口配置所需控制逻辑要求,可以完成FPGA的并行配置。

关键词:FPGA;嵌入式CPU;Leon3软核;SelectMap接口

引言

随着FPGA和SOPC技术的发展,基于FPGA的嵌入式系统与传统的嵌入式系统相比,具有设计周期短、设计风险和设计成本低、集成度高、灵活性大、维护和升级方便、硬件缺陷修复等优点。基于FPGA的嵌入式系统设计技术和市场逐渐成熟,使得嵌入式CPU软核(如Xilinx公司推出的MicroBlaze、Altera公司的Nios、欧空局开发的Leon3软核等)的大量应用成为可能。

本文结合具体应用需求,介绍了利用嵌入式CPU Leon3软核处理器对Virtex系列FPGA的配置进行控制的方法。此系统能够实现FPGA配置数据的重构,并且减少了外围CPU和CPLD器件的使用,具有很好的应用价值。

1 Leon3软核

Leon3是欧空局开发的32位CPU软核,其标准版是一种开源的软核,使用GNU LGPL授权协议,可以免费地应用于研究、教学和商业目的。Leon3软核使用VHDL语言描述,与SPARC V8兼容,使用7级流水线,集成了全流水的IEEE-754浮点处理器,提高了对多处理器的支持。由于Leon系列指令集符合SPARC V8标准,外部总线符合AMBA标准,兼容软件和IP核资源极其丰富,加上其开放源代码的策略,对它的研究和应用受到了广泛的关注。Leon3软核具有良好的可配置性和可移植性,能够根据需要灵活地选择外围控制器。并且该软核不是FPGA厂商推出的,因此可以应用于不同类型的FPGA芯片。Leon3开源软核的Grlib IP库中提供了多种功能模块,如串口控制器、存储器控制器、通用可编程I/O等,把该软核及其外围的控制模块集成到FPGA中,构成一个嵌入式片上系统。

2 SelectMap接口配置系统设计

2.1 Virtex系列FPGA配置方式

Virtex系列FPGA基于SRAM工艺,共有4种配置方式:主串(master serial)、从串(slave setial)、SelectMap和边界扫描(boundarysca-n)。串行(主串或从串)模式需要的配置信号少(PROGRAM、CCLK、DIN、INIT、DONE),FPGA在配置时钟的上升沿接收1位配置数据,该配置方式速度较慢。边界扫描模式没有存储芯片,掉电后需重新配置,所以该种配置方式多用于调试阶段。SelectMap模式是一种8位并行配置模式,它是Virtex系列FPGA最快的一种配置模式,其配置时钟最高可达66MHz,每个配置时钟周期内有8位配置数据下载到FPGA内。在对配置速度要求较高的一些应用场合,一般采用SelectMap配置方式。

SelectMap配置方式所需引脚及相应功能如表1所列。表中BUSY信号是握手信号,只有当配置时钟的频率超过50MHz时才起作用,本设计的配置时钟频率低于50MHz,因此不使用BUSY信号。M(2:0)是模式选择信号,在SelectMap配置模式下,M(2:0)应置为110。

2.2 SelectMap接口配置硬件设计实现

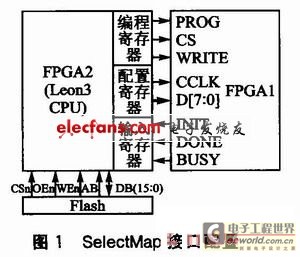

本文设计的SelectMap接口配置系统由两片FPGA和存储器(Flash)构成,如图1所示。设计中FPGA1选用了Xilinx公司Virtex系列芯片Vir-tex-5 XC5VSX95T,是需要进行配置的芯片。FPGA2内部嵌入了Leon3 CPU软核,可利用该CPU软核的存储控制器模块对Flash进行读写控制;利用FPGA内部丰富的资源,在FPGA2内部集成一个自定义的SelectMap接口控制IP核,主要用来产生FPGA的配置信号,这些SelectMap配置信号的状态由嵌入在FPGA2内部的CPU Leon3软核监控。该设计采用开源的Leon3软核CPU,并且充分利用了FPGA丰富的资源,与通常的SelectMap配置系统相比,设计成本低,设计较灵活。

Flash存储器采用Intel公司的JS28F256P30T95,具有32 MB的存储空间,用来存储FPGA1的配置数据。因为Flash的每个地址空间中存储着16位数据,Leon3 CPU处理器读取Flash地址中的数据,然后把数据以字节形式传送到FPGA2。这个过程中,CPU处理器所在的FPGA2为FPGA1提供配置时序控制信号。这些控制信号的产生由FPGA2内部集成的SelectMap接口控制IP核实现。该IP核的功能模块由3个寄存器组成:配置寄存器、编程寄存器和输入寄存器。每次CPU对Flash进行读或写操作时,这些寄存器存储FPGA1的配置信号数据。其中配置寄存器和编程寄存器为只写寄存器,输入寄存器为只读寄存器。详细的逻辑框图如图2所示。CPU数据线在SelectMap接口控制IP核内部寄存器的构成如表2所列。

该配置逻辑模块完成以下几方面的功能:启动FPGA1配置时序;向FPGA1内部传入配置数据;监测FPGA1是否正常配置。使用嵌入式CPU软核配置FPGA1的流程如下:

①启动FPGA1的配置时序。CPU地址线选中FPGA2内部编程寄存器,数据线输出FPGA1配置控制信号CS、WRITE和PROGRAM,将CS和WRITE置低,PROGRAM置高。

②监测FPGA的配置状态。CPU地址线选中FPGA2内部输入寄存器,接收FPGA1的输出信号INIT,若其值为高,那么CPU开始发出FPGA1的配置数据,否则持续检查INIT的值,直到其值为1。

③向FPGA1内传送配置数据。CPU地址线选中FPGA2内部配置寄存器,数据线Data[15:8]输出FPGA1的配置数据,Data[0]产生配置时钟CCLK,在CCLK的上升沿FPGA1接收配置数据。配置数据传送分两步,首先Data[0]置0,然后Data[0]置1。CCLK产生一个上升沿,在此过程中Data[15:8]数据保持不变。重复此过程,CPU输出FPGA1全部配置数据。

④检查FPGA1是否配置成功。FPGA1的配置数据被传送至结束时,CPU地址线选中FPGA2内部输入寄存器,接收FPGA1的输出信号DONE。若其值为高时,说明FPGA1配置成功,否则需要重新配置FPGA1。

SelectMap接口配置方式下FPGA的时序如图3所示。

3 仿真及分析

FPGA2采用Xilinx公司的Virtex-5 XC5VFX70T,SelectMap接口控制IP核采用VHDL语言实现,嵌入式CPU软核采用的是欧空局开发的Lcon3软核。在XilinxISE 10.1平台下完成对Lcon3 CPU软核处理器、外围控制器及自定义SelectMap接口控制IP核集成的设计、综合,利用Modelsim SE6.0完成仿真。

SelectMap配置仿真波形如图4所示。由于FPGA1(Virtex-5 XC5VSX95T)的配置数据较大,仿真出完整的配置过程是不现实的,图中用5个字节的配置数据来代替FPGA的完整配置过程。为了把配置寄存器数据Data和并行配置的8位数据相对照,分离出了Data的高8位Data[15:8]。从图中可以看出,在一次完整的配置过程中,CS和WRITE为低,PROGRAM为高,当监测到INIT为高时发出配置数据,在配置时钟CCLK的上升沿接收8位配置数据,DONE信号为高电平指示配置完成。该仿真结果和SelectMap配置方式的FPGA时序一致,证明了本设计的正确性及可行性。

结语

通过使用嵌入式Lcon3 CPU软核和FPGA及开发板上的存储器件,实现了对Xilinx公司的FPGA进行SelectMap配置的一种有效的方案。该方法除了可以完成FPGA芯片的配置外,更重要的是可以灵活地在线升级系统、修改和调试FPGA程序。如果存储空间够大,可以存储不同功能的FPGA程序代码,这样就可根据实际情况来加载不同代码,甚至通过通信接口也可以方便地实现远程下载代码和更新系统,使整个系统可在线配置,增强了系统的适用性和灵活性。

上一篇:嵌入式以太网控制器设计

下一篇:一种雷达信号处理模块的设计和实现

- 热门资源推荐

- 热门放大器推荐

Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用 UPC8152TB-E3

UPC8152TB-E3

京公网安备 11010802033920号

京公网安备 11010802033920号