摘要:采用FM-DCSK调制的混沌保密通信较其它混沌键控保密通信具有更优良的特性,但同时电路实现也更加复杂。DSP以其高效和灵活性在混沌通信中具有广阔的应用前景。文中根据TMS320C5402的特点,给出了用两块DSP来实现FM-DCSK通信系统的硬件方案,同时给出了系统独立工作时的硬件原理框图和软件设计流程。

关键词:数字信号处理器(DSP);调频-差分混沌键控(FM-DCSK);混沌通信;多通道缓冲串行口

1 引言

近年来,随着混沌同步和控制理论的提出与发展,混沌在信号处理、通信和控制领域的应用也日渐广泛。一般认为,在通信领域,混沌信号代替传统的正弦信号作信息载体有以下优势:其一是混沌信号的宽频特性可以实现某种意义上的扩频;其二是混沌信号的类似噪声难以预测,而这一特点正好可为信息的保密传输提供保证。

图1

混沌通信的类型很多,其中较有应用前景的有差动混沌键控(DCSK)和混沌扩频通信。它们的共同特点是信道中传送的信号不再是实现发送端和接收端同步的耦合信号,而是利用混沌信号的统计特性,即混沌信号的自相关和互相关特性来实现一定程度的保密通信。目前的研究工作主要是以理论研究和计算机仿真为主,而利用硬件来验证DCSK及其改进的FM-DCSK通信性能的设计还很少,因此,笔者设计了基于双数字信号处理器(DSP)的FM-DCSK通信系统方案,文中分别介绍了系统中的话音终端、 混沌序列的产生及其FM调制、 DCSK调制解调及数据通信等电路,分析了系统工作时程序的装载原理和可行性,同时给出了硬件原理框图和软件设计流程图。

2 系统硬件总体结构

本系统主要用来完成语音信号的采集、语音压缩编码以及对语音信号进行FM-DCSK调制,并将调制后的数据通过DSP的多通道缓冲串行口(McBSP)发送出去,同时对接收到的数据进行DCSK解调和语音解压缩、译码,并将译码后的数据进行D/A转换以还原出模拟话音。本系统利用串行数模/模数转换芯片TLV320AIC10来将输入语音信号转换成数字语音信号,待进行完处理后再将数字语音转换成模拟语音信号;低比特率声码器AMBE-1000则用来对数字语音信号进行低速率的语音压缩编码和对DCSK解调后的数据进行解码;TMS320C5402(主)不仅要对编码后的数据进行DC-SK调制和DCSK解调,而且还要作为整个系统的控制器来完成对各个功能芯片的设置、控制,并通过双口RAM芯片(IDT7206)与TMS320C5402(从)进行数据传递,同时通过多通道缓冲串行口(McBSP)与另一块TMS320C5402(从)进行双向的数据通信。TMS320C5402(从)则在TMS320C5402(主)控制下完成混沌序列的生成和序列的FM调制运算。整个系统的硬件原理如图1所示。

图中,C5402(主)采用并行方式装载程序而C5402(从)则是采用HPI方式装载程序。由于没有通过双端口RAM采用并行方式装载程序,因而可以减少C5402(主)在C5402从 装载程序时复杂的控制过程,有效地利用资源。在系统独立工作时,C5402主、从双方的通信主要通过双端口RAM来完成。

3 系统电路工作原理

本系统包括话音终端电路、混沌序列产生及其FM调制电路、DCSK调制及解调以及两个系统数据通信实现电路。各个部分在控制器的协调下完成双向的FM-DCSK通信。

3.1 话音终端电路

话音终端电路由声码器AMBE-1000与串行数模/模数转换芯片TLV320AIC10构成,可在DSP控制器的控制下完成模拟话音的数字化,并进行压缩编码以输出成帧的编码数据包,然后将其作为信息数据再经DSP做FM-DCSK调制后输出。同时将接收到的并经过DSP解调的数据包进行译码以还原出数字话音,最后经过D/A变换输出模拟话音。

图中,C5402(主)采用并行方式装载程序而C5402(从)则是采用HPI方式装载程序。由于没有通过双端口RAM采用并行方式装载程序,因而可以减少C5402(主)在C5402从 装载程序时复杂的控制过程,有效地利用资源。在系统独立工作时,C5402主、从双方的通信主要通过双端口RAM来完成。

3 系统电路工作原理

本系统包括话音终端电路、混沌序列产生及其FM调制电路、DCSK调制及解调以及两个系统数据通信实现电路。各个部分在控制器的协调下完成双向的FM-DCSK通信。

3.1 话音终端电路

话音终端电路由声码器AMBE-1000与串行数模/模数转换芯片TLV320AIC10构成,可在DSP控制器的控制下完成模拟话音的数字化,并进行压缩编码以输出成帧的编码数据包,然后将其作为信息数据再经DSP做FM-DCSK调制后输出。同时将接收到的并经过DSP解调的数据包进行译码以还原出数字话音,最后经过D/A变换输出模拟话音。

在硬件连接中,AMBE-1000的发送、接收选通信号以及移位时钟均为TLV320AIC10产生的FS和CLKS信号。为满足AMBE-1000的时序要求,将TX_STRB、TX_O_CLK分别与TLV320AIC10产生的FS和CLKS直接相连,而RX_STRB、RX_O_CLK则经过CPLD逻辑转换后与FS、CLKS相连。AMBE-1000的编码速率、信道接口方式、AD接口方式以及各种控制都是由C5402(主)通过操作不同的I/O口并经CPLD锁存完成的,其中AMBE-1000的时序逻辑图如图2所示。

对TLV320AIC10中各控制寄存器的控制可用C5402(从)通过多通道缓冲串行口McBSP0向DCSI写入相应格式的数据来完成。与C5402(从)的连接工作在SPI模式,并同样由TLV320AIC10产生FS和CLKS信号。初始化完成后,TLV320AIC10则在8kHz的采样率和16bit的线性量化模式下与声码器交换数据。而声码器每20ms与C5402(主)交换一次数据。当然,所有的工作方式都可以通过软件编程来实现。

3.2 混沌序列的产生及其FM调制

混沌序列的产生及其FM调制主要由C5402(从)完成。可利用经典的Logistic映射:

在硬件连接中,AMBE-1000的发送、接收选通信号以及移位时钟均为TLV320AIC10产生的FS和CLKS信号。为满足AMBE-1000的时序要求,将TX_STRB、TX_O_CLK分别与TLV320AIC10产生的FS和CLKS直接相连,而RX_STRB、RX_O_CLK则经过CPLD逻辑转换后与FS、CLKS相连。AMBE-1000的编码速率、信道接口方式、AD接口方式以及各种控制都是由C5402(主)通过操作不同的I/O口并经CPLD锁存完成的,其中AMBE-1000的时序逻辑图如图2所示。

对TLV320AIC10中各控制寄存器的控制可用C5402(从)通过多通道缓冲串行口McBSP0向DCSI写入相应格式的数据来完成。与C5402(从)的连接工作在SPI模式,并同样由TLV320AIC10产生FS和CLKS信号。初始化完成后,TLV320AIC10则在8kHz的采样率和16bit的线性量化模式下与声码器交换数据。而声码器每20ms与C5402(主)交换一次数据。当然,所有的工作方式都可以通过软件编程来实现。

3.2 混沌序列的产生及其FM调制

混沌序列的产生及其FM调制主要由C5402(从)完成。可利用经典的Logistic映射:

然后经离散迭代运算产生所需要的混沌序列。由FM-DCSK通信方式的原理可知,所产生的混沌序列需经过FM调制,然后才能对话音数据作DCSK调制。FM-DCSK调制解调系统框图如图3所示。因为混沌序列的FM运算量比较大,因此,本设计选择TMS320C5402作为运算处理器,它的最高工作频率可达100MHz。

C5402(从)通过双口RAM将FM调制后的混沌序列送给C5402(主),也就相当于在FM-DCSK调制解调系统中完成了混沌发生器和FM调制器的功能。

3.3 DCSK调制解调及数据通信

用C5402主可完成低速率编码后话音信号的DCSK调制和接收数据的DCSK解调,同时可控制CPLD以产生各种控制信号。

然后经离散迭代运算产生所需要的混沌序列。由FM-DCSK通信方式的原理可知,所产生的混沌序列需经过FM调制,然后才能对话音数据作DCSK调制。FM-DCSK调制解调系统框图如图3所示。因为混沌序列的FM运算量比较大,因此,本设计选择TMS320C5402作为运算处理器,它的最高工作频率可达100MHz。

C5402(从)通过双口RAM将FM调制后的混沌序列送给C5402(主),也就相当于在FM-DCSK调制解调系统中完成了混沌发生器和FM调制器的功能。

3.3 DCSK调制解调及数据通信

用C5402主可完成低速率编码后话音信号的DCSK调制和接收数据的DCSK解调,同时可控制CPLD以产生各种控制信号。

每次通信过程中,C5402(主)将从双口RAM中读取相应数目FM调制后的混沌序列,然后对接收到的话音数据按bit 进行DC-SK调制,同时通过McBSP用DMA方式接收DCSK调制数据并由C5402(主)进行DCSK解调。这两项工作都是通过中断来完成的

3.4 系统独立工作时的程序装载过程

本系统的程序装载分为C5402(主)自身的并行装载和C5402(从)的HPI装载两部分。

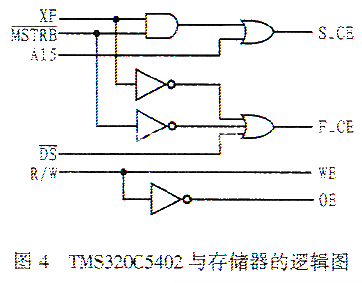

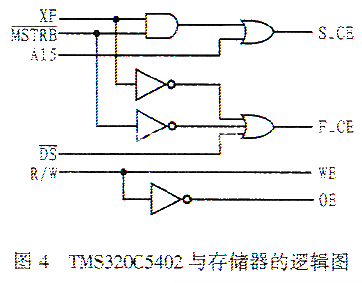

C5402(主)与Flash AT29LV1024和双口RAM之间的逻辑如图4所示。C5402(主)上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,因此,在系统进入并行引导装载模式后,C5402(主)将从数据寻址为0FFFFh的单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址和并行装载数据流。此时,C5402可将 Flash地址08000h—0FFFFh单元中的数据读到C5402对应于0000h—7FFFh寻址区的片内DRAM和片外SRAM中。Boot-loader程序结束后,用户程序的第一条语句为RSBX XF,即置XF引脚为低电平, 那么Flash将始终不选通。这样,双端口RAM的高32k区域(08000h—0FFFFh)将被释放出来作为C5402主运行时的数据区或程序区使用。C5402主装载进来的程序数据主要分为三部分:给C5402(从)的装载程序、自身的运行程序及C5402(从)的运行程序。

在C5402(主)进行并行装载的过程中,C5402(从)将判断是哪种装载模式。因为C5402从的HINT和INT2连在一起,因此,DSP上电初始化时会将07FH单元清0,同时HINT置0会导致INT2的IFR相应标志位有效,C5402(从)在查询到INT2的标志位有效后,则判断为HPI装载模式。C5402(主)在进行并行装载后,将首先运行装载程序,以便将C5402(从)的运行程序数据传送到C5402(从)中,从而将C5402(从)的程序入口地址写到07FH单元,这样即表明HPI装载结束。

每次通信过程中,C5402(主)将从双口RAM中读取相应数目FM调制后的混沌序列,然后对接收到的话音数据按bit 进行DC-SK调制,同时通过McBSP用DMA方式接收DCSK调制数据并由C5402(主)进行DCSK解调。这两项工作都是通过中断来完成的

3.4 系统独立工作时的程序装载过程

本系统的程序装载分为C5402(主)自身的并行装载和C5402(从)的HPI装载两部分。

C5402(主)与Flash AT29LV1024和双口RAM之间的逻辑如图4所示。C5402(主)上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,因此,在系统进入并行引导装载模式后,C5402(主)将从数据寻址为0FFFFh的单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址和并行装载数据流。此时,C5402可将 Flash地址08000h—0FFFFh单元中的数据读到C5402对应于0000h—7FFFh寻址区的片内DRAM和片外SRAM中。Boot-loader程序结束后,用户程序的第一条语句为RSBX XF,即置XF引脚为低电平, 那么Flash将始终不选通。这样,双端口RAM的高32k区域(08000h—0FFFFh)将被释放出来作为C5402主运行时的数据区或程序区使用。C5402主装载进来的程序数据主要分为三部分:给C5402(从)的装载程序、自身的运行程序及C5402(从)的运行程序。

在C5402(主)进行并行装载的过程中,C5402(从)将判断是哪种装载模式。因为C5402从的HINT和INT2连在一起,因此,DSP上电初始化时会将07FH单元清0,同时HINT置0会导致INT2的IFR相应标志位有效,C5402(从)在查询到INT2的标志位有效后,则判断为HPI装载模式。C5402(主)在进行并行装载后,将首先运行装载程序,以便将C5402(从)的运行程序数据传送到C5402(从)中,从而将C5402(从)的程序入口地址写到07FH单元,这样即表明HPI装载结束。

4 系统软件设计

4.1 程序流程

系统的软件设计主要包括对C5402主和C5402(从)的编程。C5402主的软件设计由C5402的初始化、AMBE-1000的初始化、McBSP0和McB-SP1初始化、DMA的初始化、DSP中断设置、接收数据中断设置程序和发送数据中断设置程序构成。图5为C5402(主)软件系统流程图,图6和图7分别为McBSP0接收中断设置和McBSP1接收中断设置流程图。C5402(从)的软件设计由C5402初始化、TLV320AIC10的初始化以及混沌序列产生和混沌序列的FM调制构成。

4 系统软件设计

4.1 程序流程

系统的软件设计主要包括对C5402主和C5402(从)的编程。C5402主的软件设计由C5402的初始化、AMBE-1000的初始化、McBSP0和McB-SP1初始化、DMA的初始化、DSP中断设置、接收数据中断设置程序和发送数据中断设置程序构成。图5为C5402(主)软件系统流程图,图6和图7分别为McBSP0接收中断设置和McBSP1接收中断设置流程图。C5402(从)的软件设计由C5402初始化、TLV320AIC10的初始化以及混沌序列产生和混沌序列的FM调制构成。

4.2 程序设计应注意的问题

在进行系统软件设计时,应注意以下几个问题:

(1)由于McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位要合理设置。同时,在设置中断向量表时,中断向量表的位置应与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,IPTR的9位地址指向128字的中断向量所在的程序页同时,中断向量表也要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

(2)要实现DSP数据采集系统的脱机独立运行,程序装载十分关键。C5402(主)进行并行装载时,AT29LV1024中的程序数据流要严格按照并行装载的格式依次把C5402从装载程序、C5402(主)自身执行程序和C5402(从)的程序装载到片内DRAM和片外双口SRAM中。

(3)当双端口RAM在两片DSP之间进行数据传递时,要合理分配空间,协调好读写时序,严格避免数据冲突。

5 结束语

本文利用两片TMS320C5402设计了FM-DCSK通信系统的硬件实现方案,给出了系统独立工作时的硬件原理框图和软件设计流程图。实践证明:并行装载模式和HPI装载模式同时使用,可有效利用系统资源、降低成本。

4.2 程序设计应注意的问题

在进行系统软件设计时,应注意以下几个问题:

(1)由于McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位要合理设置。同时,在设置中断向量表时,中断向量表的位置应与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,IPTR的9位地址指向128字的中断向量所在的程序页同时,中断向量表也要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

(2)要实现DSP数据采集系统的脱机独立运行,程序装载十分关键。C5402(主)进行并行装载时,AT29LV1024中的程序数据流要严格按照并行装载的格式依次把C5402从装载程序、C5402(主)自身执行程序和C5402(从)的程序装载到片内DRAM和片外双口SRAM中。

(3)当双端口RAM在两片DSP之间进行数据传递时,要合理分配空间,协调好读写时序,严格避免数据冲突。

5 结束语

本文利用两片TMS320C5402设计了FM-DCSK通信系统的硬件实现方案,给出了系统独立工作时的硬件原理框图和软件设计流程图。实践证明:并行装载模式和HPI装载模式同时使用,可有效利用系统资源、降低成本。

引用地址:以双DSP为核心的FM-DCSK通信系统方案设计

图中,C5402(主)采用并行方式装载程序而C5402(从)则是采用HPI方式装载程序。由于没有通过双端口RAM采用并行方式装载程序,因而可以减少C5402(主)在C5402从 装载程序时复杂的控制过程,有效地利用资源。在系统独立工作时,C5402主、从双方的通信主要通过双端口RAM来完成。

3 系统电路工作原理

本系统包括话音终端电路、混沌序列产生及其FM调制电路、DCSK调制及解调以及两个系统数据通信实现电路。各个部分在控制器的协调下完成双向的FM-DCSK通信。

3.1 话音终端电路

话音终端电路由声码器AMBE-1000与串行数模/模数转换芯片TLV320AIC10构成,可在DSP控制器的控制下完成模拟话音的数字化,并进行压缩编码以输出成帧的编码数据包,然后将其作为信息数据再经DSP做FM-DCSK调制后输出。同时将接收到的并经过DSP解调的数据包进行译码以还原出数字话音,最后经过D/A变换输出模拟话音。

图中,C5402(主)采用并行方式装载程序而C5402(从)则是采用HPI方式装载程序。由于没有通过双端口RAM采用并行方式装载程序,因而可以减少C5402(主)在C5402从 装载程序时复杂的控制过程,有效地利用资源。在系统独立工作时,C5402主、从双方的通信主要通过双端口RAM来完成。

3 系统电路工作原理

本系统包括话音终端电路、混沌序列产生及其FM调制电路、DCSK调制及解调以及两个系统数据通信实现电路。各个部分在控制器的协调下完成双向的FM-DCSK通信。

3.1 话音终端电路

话音终端电路由声码器AMBE-1000与串行数模/模数转换芯片TLV320AIC10构成,可在DSP控制器的控制下完成模拟话音的数字化,并进行压缩编码以输出成帧的编码数据包,然后将其作为信息数据再经DSP做FM-DCSK调制后输出。同时将接收到的并经过DSP解调的数据包进行译码以还原出数字话音,最后经过D/A变换输出模拟话音。

在硬件连接中,AMBE-1000的发送、接收选通信号以及移位时钟均为TLV320AIC10产生的FS和CLKS信号。为满足AMBE-1000的时序要求,将TX_STRB、TX_O_CLK分别与TLV320AIC10产生的FS和CLKS直接相连,而RX_STRB、RX_O_CLK则经过CPLD逻辑转换后与FS、CLKS相连。AMBE-1000的编码速率、信道接口方式、AD接口方式以及各种控制都是由C5402(主)通过操作不同的I/O口并经CPLD锁存完成的,其中AMBE-1000的时序逻辑图如图2所示。

对TLV320AIC10中各控制寄存器的控制可用C5402(从)通过多通道缓冲串行口McBSP0向DCSI写入相应格式的数据来完成。与C5402(从)的连接工作在SPI模式,并同样由TLV320AIC10产生FS和CLKS信号。初始化完成后,TLV320AIC10则在8kHz的采样率和16bit的线性量化模式下与声码器交换数据。而声码器每20ms与C5402(主)交换一次数据。当然,所有的工作方式都可以通过软件编程来实现。

3.2 混沌序列的产生及其FM调制

混沌序列的产生及其FM调制主要由C5402(从)完成。可利用经典的Logistic映射:

在硬件连接中,AMBE-1000的发送、接收选通信号以及移位时钟均为TLV320AIC10产生的FS和CLKS信号。为满足AMBE-1000的时序要求,将TX_STRB、TX_O_CLK分别与TLV320AIC10产生的FS和CLKS直接相连,而RX_STRB、RX_O_CLK则经过CPLD逻辑转换后与FS、CLKS相连。AMBE-1000的编码速率、信道接口方式、AD接口方式以及各种控制都是由C5402(主)通过操作不同的I/O口并经CPLD锁存完成的,其中AMBE-1000的时序逻辑图如图2所示。

对TLV320AIC10中各控制寄存器的控制可用C5402(从)通过多通道缓冲串行口McBSP0向DCSI写入相应格式的数据来完成。与C5402(从)的连接工作在SPI模式,并同样由TLV320AIC10产生FS和CLKS信号。初始化完成后,TLV320AIC10则在8kHz的采样率和16bit的线性量化模式下与声码器交换数据。而声码器每20ms与C5402(主)交换一次数据。当然,所有的工作方式都可以通过软件编程来实现。

3.2 混沌序列的产生及其FM调制

混沌序列的产生及其FM调制主要由C5402(从)完成。可利用经典的Logistic映射:

然后经离散迭代运算产生所需要的混沌序列。由FM-DCSK通信方式的原理可知,所产生的混沌序列需经过FM调制,然后才能对话音数据作DCSK调制。FM-DCSK调制解调系统框图如图3所示。因为混沌序列的FM运算量比较大,因此,本设计选择TMS320C5402作为运算处理器,它的最高工作频率可达100MHz。

C5402(从)通过双口RAM将FM调制后的混沌序列送给C5402(主),也就相当于在FM-DCSK调制解调系统中完成了混沌发生器和FM调制器的功能。

3.3 DCSK调制解调及数据通信

用C5402主可完成低速率编码后话音信号的DCSK调制和接收数据的DCSK解调,同时可控制CPLD以产生各种控制信号。

然后经离散迭代运算产生所需要的混沌序列。由FM-DCSK通信方式的原理可知,所产生的混沌序列需经过FM调制,然后才能对话音数据作DCSK调制。FM-DCSK调制解调系统框图如图3所示。因为混沌序列的FM运算量比较大,因此,本设计选择TMS320C5402作为运算处理器,它的最高工作频率可达100MHz。

C5402(从)通过双口RAM将FM调制后的混沌序列送给C5402(主),也就相当于在FM-DCSK调制解调系统中完成了混沌发生器和FM调制器的功能。

3.3 DCSK调制解调及数据通信

用C5402主可完成低速率编码后话音信号的DCSK调制和接收数据的DCSK解调,同时可控制CPLD以产生各种控制信号。

每次通信过程中,C5402(主)将从双口RAM中读取相应数目FM调制后的混沌序列,然后对接收到的话音数据按bit 进行DC-SK调制,同时通过McBSP用DMA方式接收DCSK调制数据并由C5402(主)进行DCSK解调。这两项工作都是通过中断来完成的

3.4 系统独立工作时的程序装载过程

本系统的程序装载分为C5402(主)自身的并行装载和C5402(从)的HPI装载两部分。

C5402(主)与Flash AT29LV1024和双口RAM之间的逻辑如图4所示。C5402(主)上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,因此,在系统进入并行引导装载模式后,C5402(主)将从数据寻址为0FFFFh的单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址和并行装载数据流。此时,C5402可将 Flash地址08000h—0FFFFh单元中的数据读到C5402对应于0000h—7FFFh寻址区的片内DRAM和片外SRAM中。Boot-loader程序结束后,用户程序的第一条语句为RSBX XF,即置XF引脚为低电平, 那么Flash将始终不选通。这样,双端口RAM的高32k区域(08000h—0FFFFh)将被释放出来作为C5402主运行时的数据区或程序区使用。C5402主装载进来的程序数据主要分为三部分:给C5402(从)的装载程序、自身的运行程序及C5402(从)的运行程序。

在C5402(主)进行并行装载的过程中,C5402(从)将判断是哪种装载模式。因为C5402从的HINT和INT2连在一起,因此,DSP上电初始化时会将07FH单元清0,同时HINT置0会导致INT2的IFR相应标志位有效,C5402(从)在查询到INT2的标志位有效后,则判断为HPI装载模式。C5402(主)在进行并行装载后,将首先运行装载程序,以便将C5402(从)的运行程序数据传送到C5402(从)中,从而将C5402(从)的程序入口地址写到07FH单元,这样即表明HPI装载结束。

每次通信过程中,C5402(主)将从双口RAM中读取相应数目FM调制后的混沌序列,然后对接收到的话音数据按bit 进行DC-SK调制,同时通过McBSP用DMA方式接收DCSK调制数据并由C5402(主)进行DCSK解调。这两项工作都是通过中断来完成的

3.4 系统独立工作时的程序装载过程

本系统的程序装载分为C5402(主)自身的并行装载和C5402(从)的HPI装载两部分。

C5402(主)与Flash AT29LV1024和双口RAM之间的逻辑如图4所示。C5402(主)上电复位装载时,由于Bootloader程序在初始化时设置XF为高电平,因此,在系统进入并行引导装载模式后,C5402(主)将从数据寻址为0FFFFh的单元(A15=1,选中Flash)中读取将要载入的程序存储区首地址和并行装载数据流。此时,C5402可将 Flash地址08000h—0FFFFh单元中的数据读到C5402对应于0000h—7FFFh寻址区的片内DRAM和片外SRAM中。Boot-loader程序结束后,用户程序的第一条语句为RSBX XF,即置XF引脚为低电平, 那么Flash将始终不选通。这样,双端口RAM的高32k区域(08000h—0FFFFh)将被释放出来作为C5402主运行时的数据区或程序区使用。C5402主装载进来的程序数据主要分为三部分:给C5402(从)的装载程序、自身的运行程序及C5402(从)的运行程序。

在C5402(主)进行并行装载的过程中,C5402(从)将判断是哪种装载模式。因为C5402从的HINT和INT2连在一起,因此,DSP上电初始化时会将07FH单元清0,同时HINT置0会导致INT2的IFR相应标志位有效,C5402(从)在查询到INT2的标志位有效后,则判断为HPI装载模式。C5402(主)在进行并行装载后,将首先运行装载程序,以便将C5402(从)的运行程序数据传送到C5402(从)中,从而将C5402(从)的程序入口地址写到07FH单元,这样即表明HPI装载结束。

4 系统软件设计

4.1 程序流程

系统的软件设计主要包括对C5402主和C5402(从)的编程。C5402主的软件设计由C5402的初始化、AMBE-1000的初始化、McBSP0和McB-SP1初始化、DMA的初始化、DSP中断设置、接收数据中断设置程序和发送数据中断设置程序构成。图5为C5402(主)软件系统流程图,图6和图7分别为McBSP0接收中断设置和McBSP1接收中断设置流程图。C5402(从)的软件设计由C5402初始化、TLV320AIC10的初始化以及混沌序列产生和混沌序列的FM调制构成。

4 系统软件设计

4.1 程序流程

系统的软件设计主要包括对C5402主和C5402(从)的编程。C5402主的软件设计由C5402的初始化、AMBE-1000的初始化、McBSP0和McB-SP1初始化、DMA的初始化、DSP中断设置、接收数据中断设置程序和发送数据中断设置程序构成。图5为C5402(主)软件系统流程图,图6和图7分别为McBSP0接收中断设置和McBSP1接收中断设置流程图。C5402(从)的软件设计由C5402初始化、TLV320AIC10的初始化以及混沌序列产生和混沌序列的FM调制构成。

4.2 程序设计应注意的问题

在进行系统软件设计时,应注意以下几个问题:

(1)由于McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位要合理设置。同时,在设置中断向量表时,中断向量表的位置应与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,IPTR的9位地址指向128字的中断向量所在的程序页同时,中断向量表也要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

(2)要实现DSP数据采集系统的脱机独立运行,程序装载十分关键。C5402(主)进行并行装载时,AT29LV1024中的程序数据流要严格按照并行装载的格式依次把C5402从装载程序、C5402(主)自身执行程序和C5402(从)的程序装载到片内DRAM和片外双口SRAM中。

(3)当双端口RAM在两片DSP之间进行数据传递时,要合理分配空间,协调好读写时序,严格避免数据冲突。

5 结束语

本文利用两片TMS320C5402设计了FM-DCSK通信系统的硬件实现方案,给出了系统独立工作时的硬件原理框图和软件设计流程图。实践证明:并行装载模式和HPI装载模式同时使用,可有效利用系统资源、降低成本。

4.2 程序设计应注意的问题

在进行系统软件设计时,应注意以下几个问题:

(1)由于McBSP工作在数据接收中断方式,因此全局中断和串口中断的相应位要合理设置。同时,在设置中断向量表时,中断向量表的位置应与处理器模式状态寄存器PMST中的中断向量指针IPTR相对应,IPTR的9位地址指向128字的中断向量所在的程序页同时,中断向量表也要严格按照C5402规定的格式编写,否则不能正确地产生需要的中断结果。

(2)要实现DSP数据采集系统的脱机独立运行,程序装载十分关键。C5402(主)进行并行装载时,AT29LV1024中的程序数据流要严格按照并行装载的格式依次把C5402从装载程序、C5402(主)自身执行程序和C5402(从)的程序装载到片内DRAM和片外双口SRAM中。

(3)当双端口RAM在两片DSP之间进行数据传递时,要合理分配空间,协调好读写时序,严格避免数据冲突。

5 结束语

本文利用两片TMS320C5402设计了FM-DCSK通信系统的硬件实现方案,给出了系统独立工作时的硬件原理框图和软件设计流程图。实践证明:并行装载模式和HPI装载模式同时使用,可有效利用系统资源、降低成本。

零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南 747HC

747HC

京公网安备 11010802033920号

京公网安备 11010802033920号