1 引言

Philips公司的8XC552单片机以其体积小、功能强、价格低等优势而广泛地使用在工业控制、DCS控制和智能仪器等领域。笔者在智能配电监测仪的研制过程中,虽然采取了相应的抗干扰措施,但由于工业现场环境中电磁场、电网尖峰、谐波、浪涌及雷电辐射等影响,仍有可能出现程序死循环、跑飞等失控现象。为此,笔者采用Watchdog技术保证了系统的正常运行,通常Watchdog技术在单片机应用系统中可分为软件Watchdog和硬件Watchdog。Philips公司的8XC552、Intel的8098、Motorala的68C05以及Microchip的16C5X系列单片机本身已带有软件Watchdog功能,因此,只要硬件接法正确,在软件设计中调用相应语句进行启动即可。

2 硬件组成原理

2.1系统工作原理

图1所示是87C522单片机用于智能型配电仪的连接电路,本智能配电仪中的87C552为主控芯片,该芯片除具有三个16位定时器T0、T1及T2外,还有一个专作监视8位定时器、简称WDT(WatchdogTimer)的T3定时器。因为微控制器有时会受噪音、射频干扰等环境因素的影响而导入错误的运行状态。监视定时器的功能就是在某特定的时限内使微控制器复位,从而将其从错误的状态中恢复过来以重新开始正常运行。当T3用作Watchdog定时器并由软件启动计时后,如果系统已达到所设定的预定时间而仍没有重新启动定时器,此时就会产生溢出信号并停止计时,表明系统出现异常。CPU可以对定时器重新启动、清零、设定计时值等操作。系统正常运行时,CPU将周期性地重新启动定时器,当然其启动周期应小于定时器的设定值,以保证定时器始终不能产生溢出信号。而当系统运行不正常时,由于CPU不能周期性地启动定时器,因而定时器将产生溢出信号,以强迫CPU恢复系统的正常运行。

2.2 Watchdog的内部结构原理

监视定时器的结构原理如图2所示。它的核心为一8位定时器,其前级是一个11位定标器。后者的输入信号为fosc/12,即定标器对机器周期进行递增计数。这样,每过2个机器周期,定时器T3的值便增加1000次。若用16MHz或24MHz晶体振荡器,则监视定时器的增值间隔将分别为1.536ms和1.024ms;其相应的最大溢出周期分别为393.216ms和262.144ms。

当监视定时器溢出时,系统将产生一个内部复位脉冲以使8XC552复位。由图2可以看出,T3溢出时,RST引脚内侧的晶体管因栅极出现一个负脉冲而瞬时导通,从而在RST引脚上输出一个复位正脉冲,其宽度为3个机器周期。如果RST引脚外接电容,则这么窄的输出脉冲可能遭到破坏,因为电容不允许RST引脚电压产生突变,但这不会影响到内部复位操作。

如果将8XC552的 引脚接至低电平,则输入信号至定标器的通路将畅通无阻,于是监视定时器便正常运作。但若将

引脚接至低电平,则输入信号至定标器的通路将畅通无阻,于是监视定时器便正常运作。但若将 引脚接高电平,输入信号则会因与门被封锁而不能通过,这时监视定时器处于关闭状态。应当指出,一旦T3被

引脚接高电平,输入信号则会因与门被封锁而不能通过,这时监视定时器处于关闭状态。应当指出,一旦T3被 开启,则无法用软件使之关闭;同时如果T3被EW禁止,也无法用软件启动。

开启,则无法用软件使之关闭;同时如果T3被EW禁止,也无法用软件启动。

如果 =0,那么PCON寄存器的PD位便不可写入,其初值为0,无法置l,即不可进入掉电方式。故监视定时器和掉电方式两者不可兼得。

=0,那么PCON寄存器的PD位便不可写入,其初值为0,无法置l,即不可进入掉电方式。故监视定时器和掉电方式两者不可兼得。

3 调试中的常见问题及其解决方法

在对系统进行调试时,有可能出现闪屏、无法显示以及显示杂乱等现象,现将这些问题的解决方法介绍如下:

(1)LCD出现闪屏,无法翻屏显示现象

笔者在用仿真器运行编程时,LCD能够翻屏并不断显示采集来的三相用电参数,但离开仿真器处于脱机运行状态时,LCD只能显示第一屏数据。经查仿真器的![]() 引脚接高电平,而脱机时

引脚接高电平,而脱机时![]() 脚悬空,从而引起了

脚悬空,从而引起了![]() 脚的状态不固定,并不断产生内部复位信号使单片机复位而出现了上述现象。后来把

脚的状态不固定,并不断产生内部复位信号使单片机复位而出现了上述现象。后来把![]() 脚接低电平,仍然出现上述现象。而把

脚接低电平,仍然出现上述现象。而把![]() 脚接高电平后(即禁用Watchdog功能),则LCD显示正常。因此,引脚

脚接高电平后(即禁用Watchdog功能),则LCD显示正常。因此,引脚![]() 应严格禁止悬空以避免出现不稳定的状态,同时在未载入Watchdog程序之前,其引脚

应严格禁止悬空以避免出现不稳定的状态,同时在未载入Watchdog程序之前,其引脚![]() 也不能接低电平。

也不能接低电平。

(2)LCD无显示

RST端的电容应确保连接正确,否则在高电平时将无法加到复位端而使CPU不能运行程序,从而出现LCD无显示的现象。

(3)LCD显示数据杂乱无章、数据死锁

把![]() 脚接低电平,可能会出现LCD显示的数据杂乱无章、数据死锁现象。其原因是源程序中未载入Watchdog程序,因此应保证在源程序中加入Watchdog程序,以消除数据的死锁或显示杂乱无章等问题。

脚接低电平,可能会出现LCD显示的数据杂乱无章、数据死锁现象。其原因是源程序中未载入Watchdog程序,因此应保证在源程序中加入Watchdog程序,以消除数据的死锁或显示杂乱无章等问题。

4 软件设计

4.1软件设计

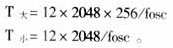

编写监视定时器运行软件时,程序员首先应当确定系统能够在错误状态下支持的时间,也就是设定溢出周期的依据。例如能维持16ms,则把T3的初值设定为10,这样,在16MHz晶振的情况下,溢出周期为15.36ms。此时程序员就可对其软件进行划分,以确定把重写T3值的指令插在什么地方,才能使相邻两次重写操作间隔不超过监视定时器的溢出周期,以保证正常运作时T3不溢出。因此,程序员应当了解所有软件模块的执行时间,同时也要考虑到出现条件跳转、子程序及内外中断等因素所带来的影响。对于那些很难估算其执行时间的程序段落,应按最坏情况估算。为防止误写,监视定时器值的重写可分两步进行。首先将PCON.4(监视定时器装入允许位WLE)置1,以允许对T3进行写入;第二步向T3写入新值。由图2可知,对T3的写信号同时也会加到WLE的清0端,于是每当T3被写入新值时,WLE位便自动复位。因此,当该值为00H时,溢出间隔最大;而FFH值则对应最小溢出周期。若采用12MHz晶振,这两值则分别为524ms和2ms。最大和最小溢出周期的计算公式分别为:

由于在空闲方式下,监视定时器照常运行。因此,该方式与掉电方式是矛盾的,因为前者需要时钟,后者冻结时钟。故当![]() =0而开启T3工作时,8XC552将无法进入掉电方式,此时向PCON.1写l的操作无效,因而它将保持为0。在软件开发调试的早期阶段,可将引脚

=0而开启T3工作时,8XC552将无法进入掉电方式,此时向PCON.1写l的操作无效,因而它将保持为0。在软件开发调试的早期阶段,可将引脚![]() 接高电平以关闭监视定时器,而在后期改接低电平以完成调试过程。

接高电平以关闭监视定时器,而在后期改接低电平以完成调试过程。

4.2定时间隔和访问时间的设定

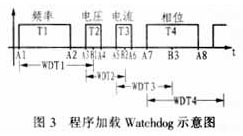

数据采集及处理是程序中的关键部分,也是决定仪器精度的关键所在。本仪器采用电压、电流、频率、相位为主要采集参数,且这些参数是连续变化的,因此采样时间不宜设置得过长,否则会影响仪器的精度。笔者将电流与电压的采样时间定为5ms,频率与相位的采集时间为20ms,这样,Watchdog的定时间隔设置较佳,具体如图3所示。图3中,Watchdog在WDT1时间内完成对采集频率数据的监控,而在WDT2、WDT3、WDT4内分别负责对电压、电流、相位数据采集的监控。在设计程序时,一般取1.1Ts<Tw<2Ts,其中Ts为采样周期,Tw为Watchdog的定时时间,Ts分别为T1、T2、T3、T4的大小,Tw分别为WDT1、WDT2、WDT3、WDT4的大小。Tw设置太小会增加访问频率,影响程序执行效率;而设置太大则会干扰程序的正常运行,且需等待很长时间才可以恢复运行,而采集或控制对象可能已在这一步偏离过大。因此,CPU访问时间原则上小于Tw就可以了,为防止时间估计不准,设计时应小些为好,这样可以防止系统异常而处于每经过Tw时间启动一次的死循环中。

4.3软件程序

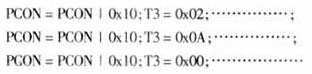

本智能监控仪用C语言编写程序,并采用12MHz晶振时,其溢出时间应分别设置为6ms、20ms、524ms…,这样,在源程序中应适时加入的各Watchdog程序如下:

5结束语

在智能配电仪的源程序中加入Watchdog后,其整个系统运行将更加稳定、可靠,从而有效地克服了来自工业用电现场的各种干扰。

上一篇:基于LabVIEW的远程测控方法

下一篇:开关功率放大器的数字控制方案研究

推荐阅读最新更新时间:2024-03-30 21:21

![[<font color='red'>单片机</font>框架][bsp层][AT32F415][bsp_adc] adc配置和使用](https://6.eewimg.cn/news/statics/images/loading.gif)

- 先到先得双重有礼 成为体验FLUKE新品的先锋者

- 先到先得双重有礼 成为体验FLUKE新品的先锋者

- MPS 隔离式稳压 DC/DC 模块——MIE系列首发,邀你一探究竟!

- 4小时实战+剖析:TI工程师教你快速上手 各种无线产品开发 (限量$14售CC1352R1无线开发板,助你参与动手实验)

- 大联大有奖直播:科技之眼-思特威图像传感器的新视界

- 读PI 汽车电子参考设计,赢京东卡!

- 有奖直播|TI MSP430™民用超声波水表开发指南及其智能模拟组合模块在传感器检测中的应用

- 有奖直播|罗彻斯特电子半导体全周期解决方案 助您应对供应链中断和元器件停产的挑战

- 你吐槽 我送书

- 跟 TI工程师 立下你的金猪Flag!立Flag & 分享赢双重好礼!

深度学习轻松学:核心算法与视觉实践 (冯超)

深度学习轻松学:核心算法与视觉实践 (冯超) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号