1引 言

列车需要传输大量的设备控制和旅客服务信息,随着这些信息的数量和种类不断地增长,迫切需要一种大容量,高速度的信息传输系统。为此,国际电工委员会(IEC)制定了一项用于规范车载设备数据通信的标准——IEC61375(列车通信网标准),即TCN标准,该标准于1999年6月成为国际标准。目前国际上主要的TCN产品供应商是德国西门子和瑞士Duagon公司,国内的株洲电力机车研究所和大连北车集团电力牵引研究所等单位进行了大量的TCN相关研究工作并取得了丰硕的科研成果。

TCN标准推荐在机车上层使用绞线式列车总线WTB,在下层使用多功能车辆总线MVB。MVB总线和机车中的各种电气设备相连,这些设备按性能可以分为5类,其中二类设备的主要特征是具有消息数据通信的功能。为了实现消息数据通信,需要在实时操作系统的支持下采用软件编程,利用应用程序接口API等接口来调用网络协议的各种功能,从而实现消息数据的通信。MVB 2类设备硬件核心采用ARM7内核微处理器NET+50作为主CPU实现系统的总体控制,采用MVBC01芯片作为MVB通信控制器实现链路层的数据处理,软件核心采用嵌入式实时操作系统Nucleus Plus来实现任务管理、中断管理等上层管理。

2 MVB 2类设备系统硬件设计

硬件系统设计主要包括应用处理器模块、通信存储器模块、通信控制器模块、存储器模块、PC104接口模块、物理层接口模块等几部分的设计,其中核心模块是ARM处理器和MVB通信控制器MVBC01。系统硬件设计框图如图1所示。

系统硬件各部分电路的功能和设计方法如下:

2.1 应用处理器模块

应用处理器采用ARM核微处理器NET+50作为核心处理器。NET十50由Netsilicon公司生产,属于ARM7系列。NET+50处理器包括一个ARM7TDMI核,32位内部总线,支持所有SRAM,SDRAM,FLASH,E2PROM,有40个可编程I/O接口引脚,16个输入接口引脚,36个可编程中断,2个完全独立的HDLC/UART/SPI串行口以及完整的以太网控制器。

2.2 存储器模块

存储器模块为ARM处理器NET+50正常工作时提供所需的程序存贮空间,内存空间和数据存储空间。NET+50集成了内存控制器模块(Memory Controller Mod-ule),为存储设备提供无缝连接,系统通过配置内存控制器模块的控制寄存器和片选CS控制寄存器来实现访问相应存储器的信号和逻辑。

本设计中选用大小为16 MB的高速SDRAM为系统提供内存服务,选用大小为512 kB的NVRAM为系统提供数据存储空间,选用大小为4 MB的FLASH为系统提供程序存储空间。使用ARM处理器的地址线、数据线以及相应的片选、读/写、时钟线完成对存储器的寻址。

2.3 通信控制器模块

通信控制器MVBC是MVB总线上的新一代核心处理器,他独立于物理层和功能设备,为在总线上的各个设备提供通讯接口和通讯服务,可通过配置应用在符合TCN标准的1,2,3,4类设备中。MVBC把来自于MVB总线的串行化信号转换为并行的数据字节,也把需发送的字节交由串行化电路发送到传输介质上。MVBC可实现数据链路层以及一部分传输层的数据处理,并通过通讯存储器来与上层软件交互。

本系统中MVB通信控制器采用MVBC01 ASIC专用芯片,符合IEC61375-1国际标准。MVBC01专用芯片采用16位数据总线,提供了丰富的接口控制信号,简化了与各种宿主CPU以及通信存储器的接口设计,支持MVB协议中链路层及以下的功能。[page]

2.4 通信存储器模块

通信存储器地址空间保存MVBC01的所有数据和信息,既可以被MVBC01访问又可以被ARM处理器访问。本系统中采用两片512 kB大小的SRAM cy62148扩展成1 MB的寻址空间。通信存储器的寻址空间划分为4部分,分别为Logical AddreSS Space(LA),Device AddressSpace(DA),Service Area(1 kB)和Miscellany。

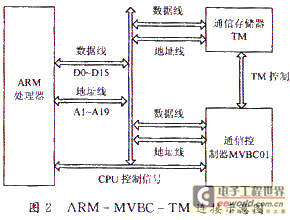

通信存储器分别通过数据线,地址线和ARM处理器以及MVBC01相连,从而实现数据交换和地址寻址,ARM处理器、MVBC01和通信存储器的连接示意图如图2所示。

MVBC01内部集成Traffic Memory Controller(TMC)模块,负责控制通信存储器的访问模式,TMC与仲裁控制器和逻辑地址密切相关。TMC模块负责控制3种存储器访问模式,分别是:ARM CPU访问通信存储器;ARM CPU访问MVBC内部寄存器;MVBC01访问通信存储器。TMC模块还对ARM处理器和MVBC同时访问通信存储器所产生的访问冲突做出仲裁。

2.5 MVB物理层接口电路模块

物理层接口电路模块的设计如图3所示。物理层接口采用电气短距离介质ESD+接口,系统信号通道使用光耦实现主系统与外界得电隔离以提高系统可靠性,使用RS 485芯片作为收发器,并使用过压保护模块来防止瞬问过压对器件的损坏。

图3所示的MVBC端口ICA(MVB Input Data Chan-nel A)和ICB(MVB Input Data Channel B)分别为MVB输入数据通道A和输入数据通道B,来自物理层收发器的MVB信号由此端口送入MVB通信控制器MVBC01中;MVBC端口OC(MVB Output Data Channel)是MVB数据输出端口,数据经由此端口将发送至物理层收发器;MVBC端口SF(Send Frame)为输出端口,输出信号可作为物理层的使能信号,该信号有效时表示一个报文正在通过MVBC端口OC(MVB Output Data Channel)输出。

2.6 其他

在MVB设备正常运行时,可以通过RS 485/RS 232通信接口进行程序的监控和调试。系统可以通过跳线选择RS 485/RS 232接口是工作在RS 485还是RS 232下。

其他还有诸如看门狗、JTAG接口、时钟、电源、PC104接口等模块,本文不再详述。

3 系统软件设计

3.1 系统软件体系结构

MVB 2类设备软件体系采用典型的嵌入式软件体系结构,包括驱动层、操作系统层、应用软件层,其中操作系统层是软件体系的核心。系统的软件结构如图4所示。

系统软件结构各部分功能如下:

3.1.1 驱动层

驱动层是直接和硬件相联系的一层,他对操作系统和应用提供所需的驱动支持。该层主要包括3种类型的程序:板级支持BSP、系统级驱动和应用级驱动。

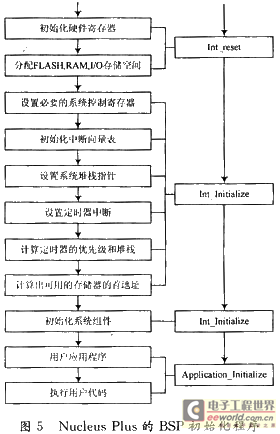

板级支持BSP 在用户的应用程序启动之前,完成对系统的初始化必须有专门的一段启动代码,即板级支持BSP。板级支持BSP介于物理硬件和实时操作系统之间,在系统上电后,初始化系统的硬件环境,包括初始化ARM处理器、初始化中断控制器、初始化存储器、初始化堆栈等。NucleusPlus操作系统的BSP初始化程序流程如图5所示。

系统级驱动 与系统软件相关的驱动,这类驱动是操作系统和中间件等系统软件所需的驱动程序,他们的开发要按照系统软件的要求进行。

应用级驱动 与应用程序相关的驱动,和操作系统无关,由应用决定。

3.1.2 操作系统层

操作系统层足嵌入式软件的核心,是系统的软件支持平台。主要包括实时操作系统内核、文件系统、电源管理、嵌入式GUI系统、嵌入式网络系统。其中嵌入式内核是基础和必备的部分,主要完成任务调度、内存管理、任务间通信、任务的同步与互斥、中断管理、定时器等功能。本系统采用Nucleus Plus嵌入式操作系统,能完全满足MVB对于实时性、可靠性、完整性和有效性的要求。NucleusPlus采用了软件组件的方法,每个组件具有单一而明确的目的,包括任务控制管理、内存控制管理、定时器管理、中断、系统诊断、I/O驱动管理等16个组件。

3.1.3 应用软件层

应用软件层主要由多个相对独立的应用任务组成,每个应用完成一个特定的工作,这里主要包括MVB协议栈软件。MVB协议栈软件在实时操作系统内核的支持下,通过MVB驱动模块完成MVB网络数据通信任务。用户应用可以利用MVB协议栈的接口函数访问需要的数据集,并利用收到或者发送的数据进行相应的控制或其他数据处理工作。

3.2 实时协议

每个网络都要有与之相应的网络软件在其上运行,这些软件被称为协议。在互联网上运行的协议我们称之为TCP/IP协议,在列车通信网上运行的类似TCP/IP的协议我们称之为实时协议(Real Time Protocol,RTP),实时协议为一个应用与另一个应用在列车通信网上的通信提供协议和服务。

实时协议分层结构如图6所示。由图中的分层结构可知MVB实时协议包括过程变量通讯和消息数据通讯两部分。由图可知变量的协议和服务包括过程数据链路层接口(LPI)和变量的应用层接口(AVI)。消息协议和服务包括消息数据链路层接口(LMI)、网络层、传送层、会话层、应用层接口(AMI)。其中链路层接口又称为低层接口,他规定来自总线的服务,应用层接口又称为高层接口,他规定提供给应用的应用层接口。

3.3 消息通信机制及其实现

MVB 2类设备的主要特征是实现消息数据的发送和接收。消息通信中实时协议是由信使执行的,他是作为独立的进程与应用并行运行。实时协议的网络层、传输层、会话层、表示层是由信使来执行并实现的,信使与应用层有一个消息应用层接口(AMI),通过这个接口应用可以调用信使的服务。同时信使与链路层也有一个接口:消息链路层接口(LMI),链路层通过这个接口向信使提供服务。在编程实现消息通信时,只需要使用消息应用层接口。

用户开发程序来实现消息通信,就是使用消息应用层接口中的接口函数来调用信使的各项功能,实现消息通信的应用程序就是按照这个顺序编写和执行的。消息数据的实现程序的流程如图7所示。

4 结 语

使用符合TCN标准的产品是开发下一代新式列车的重要发展趋势,本文通过对IEC61375-1列车通讯网络标准的研究,提出了MVB 2类设备软硬件的设计方案并完成了系统硬件各功能模块设计和上层软件的部分设计,对MVB实时协议RTP和消息通信的机制也做了深入的研究,并给出了消息通信的编程实现方法。通过对基于ARM处理器的MVB 2类设备的深入研究和功能设计实现,不但为以后开发更高类别的MVB设备积累了经验,而且为进一步自主开发其他符合TCN标准的MVB产品提供了借鉴。

上一篇:ARM体系下浮点数Middle-Endian问题的处理

下一篇:基于ARM的智能电子提花机控制系统设计

推荐阅读最新更新时间:2024-03-16 12:38

YAMAHA_rx-v340_rx-v340rds_htr-5630_htr-5630rds_dsp-ax340维修手册

YAMAHA_rx-v340_rx-v340rds_htr-5630_htr-5630rds_dsp-ax340维修手册 Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号