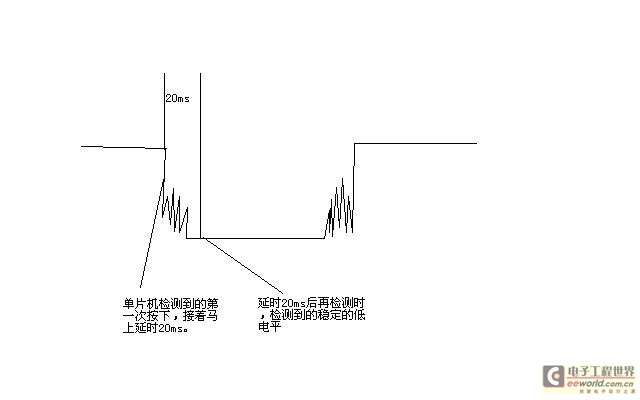

按键在按下时会产生抖动,释放时也会产生抖动,所以在设计键盘扫描程序时必须考虑按键的消抖,我们一般只考虑按下时的抖动,而放弃对释放时抖动的消抖。抖动时间一般为20ms左右。按下的最终结果是低电平。

在单片机设计的的按键去抖思路是:检测到按下时延时20ms,再检测,如果状态仍为按下,则确认是按下的;如果状态为弹起的,则确认是干扰,无按键按下。

有一个概念要理一下,按键按下时会有抖动,也就是说我们其实只按一次,但是实际产生的“按下”却是许多次的,这些许多次集中在这20ms里。我们按的只是一次,而实际却产生了许多次,那么就必须滤除其他的次数。单片机为了得到真正的“按下”,通过延时20ms,把其他的“按下”(也就是抖动)给滤除了。然后再次判断是否有按下,因为有的时候干扰很大。

而在FPGA中,基于下面的程序,理解如下:在这个程序里检测按键是否按下的方法是脉冲边沿检法。而在单片机里是判断是否为低电平的方法(那么在FPGA中可不可以也用这个方法呢?)第一次检测到后,启动20ms计数器,时间到后再检测。这里的检测方法跟脉冲边沿检测法有异曲同工之处,FPGA过20ms检测按键是否按下,存储检测到的值,并且按位取反与前一个20ms检测的值相与,得到一个值,如果为1,则判断按键按下,否则则无按下。所以跟单片机按键扫描的原理是一样的,不同的是检测方法不一样。 图2 FPGA按键的理解示意图

图2 FPGA按键的理解示意图

其中key_an寄存器的功能是检测第一次的“按下”,是cnt的启动标志位。通过也能滤除干扰信号。

led_ctrl是确实有按键按下的信号,维持一个时钟周期。

特权同学的Verilog键盘扫描程序

//说明:当三个独立按键的某一个被按下后,相应的LED被点亮;

// 再次按下后,LED熄灭,按键控制LED亮灭

module sw_debounce(

clk,rst_n,

sw1_n,sw2_n,sw3_n,

led_d1,led_d2,led_d3

);

input clk; //主时钟信号,50MHz

input rst_n; //复位信号,低有效

input sw1_n,sw2_n,sw3_n; //三个独立按键,低表示按下

output led_d1,led_d2,led_d3; //发光二极管,分别由按键控制

//----------------------------------

reg[2:0] key_rst;

always @(posedge clk or negedge rst_n)

if (!rst_n) key_rst <= 3'b111;

else key_rst <= {sw3_n,sw2_n,sw1_n};

reg[2:0] key_rst_r; //每个时钟周期的上升沿将low_sw信号锁存到low_sw_r中

always @ ( posedge clk or negedge rst_n )

if (!rst_n) key_rst_r <= 3'b111;

else key_rst_r <= key_rst;

//当寄存器key_rst由1变为0时,led_an的值变为高,维持一个时钟周期

wire[2:0] key_an = key_rst_r & ( ~key_rst); //检测到按下的第一次(cnt的启动信号)

//-------------------------------------------

reg[19:0] cnt; //计数寄存器

always @ (posedge clk or negedge rst_n)

if (!rst_n) cnt <= 20'd0; //异步复位

else if(key_an) cnt <=20'd0;

else cnt <= cnt + 1'b1;

reg[2:0] low_sw;

always @(posedge clk or negedge rst_n)

if (!rst_n) low_sw <= 3'b111;

else if (cnt == 20'hfffff) //满20ms,将按键值锁存到寄存器low_sw中 cnt == 20'hfffff

low_sw <= {sw3_n,sw2_n,sw1_n};

//-----------------------------------------------

reg [2:0] low_sw_r; //每个时钟周期的上升沿将low_sw信号锁存到low_sw_r中

always @ ( posedge clk or negedge rst_n )

if (!rst_n) low_sw_r <= 3'b111;

else low_sw_r <= low_sw;

//当寄存器low_sw由1变为0时,led_ctrl的值变为高,维持一个时钟周期

wire[2:0] led_ctrl = low_sw_r[2:0] & ( ~low_sw[2:0]);

reg d1;

reg d2;

reg d3;

always @ (posedge clk or negedge rst_n)

if (!rst_n) begin

d1 <= 1'b0;

d2 <= 1'b0;

d3 <= 1'b0;

end

else begin //某个按键值变化时,LED将做亮灭翻转

if ( led_ctrl[0] ) d1 <= ~d1;

if ( led_ctrl[1] ) d2 <= ~d2;

if ( led_ctrl[2] ) d3 <= ~d3;

end

assign led_d3 = d1 ? 1'b1 : 1'b0; //LED翻转输出

assign led_d2 = d2 ? 1'b1 : 1'b0;

assign led_d1 = d3 ? 1'b1 : 1'b0;

endmodule

上一篇:Cortex M3S811学习笔记-TIMER32

下一篇:c语言模块化编程的方法

推荐阅读最新更新时间:2024-03-16 13:08

深入浅出玩转FPGA - 第4版 (吴厚航)

深入浅出玩转FPGA - 第4版 (吴厚航) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号