0 引言

石英晶体谐振器(以下简称石英晶体)广泛用作时间频率基准和为时序逻辑电路提供同步脉冲。石英晶体的测试方法主要有阻抗计法、π网络最大传输法、π网络零相位法,其中π网络零相位法是国际电工委员会(IEC)推荐的标准方法。π网络零相位法石英晶体测试设备在发达国家已广泛使用。典型仪器是美国S&A公司生产的250B零相位测试系统,其测试频率范围为0.5~200 MHz,串联谐振频率测试精度±2 ppm。阻抗计型石英晶体测试设备在中国仍然占主导地位。阻抗计型石英晶体测试设备具有制造成本较低,操作简单的特点。但其串联谐振频率测量范围较小,测量精度较低。因此,研制宽范围、高精度的石英晶体频率测试系统,具有服务生产的实际意义。

π网络零相位法石英晶体测试系统所能测量的频率范围和精度直接依赖于π网络的扫频信号源,为了使石英晶体测试系统的测量范围达到20 kHz~400 MHz,需要研究设计一个信号源,该信号源的输出频率范围为0~400 MHz,并且输出频率精度高、稳定度高、频率分辨率高、频率切换速度快。

1 π网络零相位法高频石英晶体测试系统设计

1.1 石英晶体电参数等效模型

石英晶体具有压电效应,当外加交变电场的频率等于其固有频率时,石英晶体将产生机械谐振,该机械振动通过压电效应与振荡电路相耦合产生电谐振,这种情况下石英晶体可以等效为图1所示的RLC谐振电路。其中,C0是静电容,L1为动态电感,Rr是串联谐振电阻,C1为动态电容。

1.2 π网络零相位法石英晶体频率测试原理

IEC推荐的π网络模型如图2所示,π网络由对称的双π型回路组成,R1,R2和R3构成输入衰减器,R4,R5和R6构成输出衰减器,它们的作用是使π网络的阻抗与测量仪表的阻抗相匹配,并衰减来自测量仪器的反射信号。Y为被测石英晶体。VA为π网络输入信号,VB为π网络输出信号,实际测量对,不断改变输入信号的频率,测量输入信号和输出信号的相位差,当石英晶体处在谐振状态时,整个π网络呈纯电阻性,输入信号和输出信号之间相位差为零。因此,π网络零相位法可通过检测π网络两端信号的相位差是否为零来判断待测石英晶体是否谐振,从而测出石英晶体的串联谐振频率。当π网络两端信号的相位差为零时,石英晶体处在谐振状态,石英晶体串联谐振频率等于π网络输入信号频率。

1.3 测试系统设计

本系统基于霄网络零相位法设计而成,由DDS电路、π网络电路、鉴相电路、模拟信号处理电路、串口电路、LCD电路、触摸屏电路、键盘电路、512 MB NANDFLASH存储器电路等组成。图3是晶体频率测试系统原理框图。

高频石英晶体测试系统以一款ARM芯片STM32F103作为核心单元。STM32F103内核为32 b的Cortex-M3 CFU,最高可达72 MHz工作频率。STM 32F103通过内置高速SPI总线与DDS芯片AD9912相连,控制AD9912输出扫频信号。

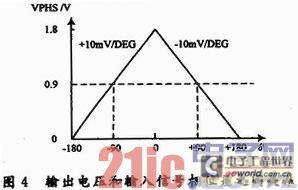

当被测晶体放入π网络电路后,在不同的扫频信号作用下,π网络两端输入和输出信号的相位差不同。π网络两端的输入信号和输出信号分别送入鉴相电路,在鉴相电路的输出端得到与π网络两端输入和输出信号的相位差成正比的电压信号。鉴相电路的输出电压信号和输入信号相位差之间的关系如图4所示。

鉴相电路的输出电压信号经过信号调理电路转变为适合于进行ADC采集的信号。信号通过STM32F103内置的12位ADC通道采集到处理器内部。测量过程时,DDS输出信号的频率由小变大,π网络两端输入信号和输出信号的相位差绝对值由大变小并逐渐接近于零,之后又由小变大。而ADC采集的结果则由小变大,到达最大值后,又由大变小。因此,这个最大值1.8 V处对应的DDS输出信号频率即为石英晶体的串联谐振频率。

2 DDS技术在测试系统中的应用

2.1 DDS技术

DDS有2个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的范围宽,频率分辨率高。与传统的频率合成器相比,DDS具有低成本、低功耗、高分辨率和频率快速转换等优点,广泛应用于电子仪器仪表领域。

AD9912是ADI公司于2007年新推出的一款DDS芯片,内部时钟速度可高达1 GSPS,并集成了14位数模转换器,因此可以直接输出400 MHz信号。AD9912采用48位频率控制字,输出频率分辨率小于4μHz。AD9912兼容多种系统时钟输入方式,石英晶体、晶体振荡器和外部时钟都可以作为其系统时钟输入。由于具有片上系统时钟锁相环(PLL),允许系统时钟输入低至25 MHz。

2.2 信号源硬件设计

笔者选择ADI公司的AD9912作为信号源的核心。STM32F103通过内置高速SPI总线控制AD9912输出0~400 MHz的扫频信号。AD9912的工作原理如图5所示。

AD9912的外围电路主要由5大模块组成:电源、时钟源、SPI通信接口、启动配置逻辑、输出信号处理电路。

AD9912的电源分为模拟3.3 V、数字3.3 V、模拟1.8 V和数字1.8 V四大类。模拟3.3 V和数字3.3 V经过滤波器互相隔离。模拟1.8 V和数字1.8 V经过滤波器互相隔离。AD9912的参考时钟选用25 MHz的高性能恒温石英晶体,AD9912内部的PLL电路对该参考时钟进行40倍倍频得到1 000 MHz时钟信号作为AD9912的系统时钟。32管脚CLKMODESEL为时钟模式选择管脚,如果使用石英晶体作为系统时钟输入,该管脚应该接地,如果使用振荡器或者外部时钟源作为系统时钟输入,该管脚应被上拉至1.8 V。由于选用的是石英晶体,该管脚接地。

SPI通信接口硬件连接如图6所示。[page]

启动配置逻辑包含S1,S2,S3,S4四个管脚。其中S4为逻辑0时,选择时钟模式:使用石英晶体作为系统时钟输入,并且由AD9912内部的PLL电路进行倍频得到时钟信号;S4为逻辑1时,选择时钟模式:由外部直接输入时钟信号。因此,把S4设置为逻辑0。S1、S2和S3的8种不同逻辑组合,用来选择8组预置的16位频率控制字。允许在未配置I/O寄存器的情况下,产生8种频率不同的信号。由于本测试系统需要的是扫描信号,不需要某固定频率的信号,因此,把S1,S2和S3设置为逻辑0,使DDS在启动时不输出信号。

AD9912的输出信号为差分信号,采用射频变压器将差分信号转换为单端信号,并经过低通滤波电路和功率放大电路后输入至π网络和补偿网络。AD9912输出信号处理电路如图7所示。其中,DAC_OUT和DAC_OUTB是AD9912输出的差分信号。

2.3 信号源软件设计

处理器STM32F103控制AD9912输出频率信号,主要是通过SPI向AD9912的寄存器中写入对应的值。

由于选用25 MHz的高性能恒温石英晶体作为参考时钟,需要使能系统时钟PLL,应将寄存器0x0010的第4位设置为逻辑0。

寄存器0x01A0~0x01AD为输出信号控制字,其中0x01A0~0x01A5为保留寄存器,0x01A6~0x01AB为频率控制字,0x01AC~0x01AD为相位控制字。

输出信号频率与频率控制字关系为:

fDDS=(FTW/248)fs (1)

式中:fDDS为AD9912输出信号频率;FTW为频率控制字;fs为AD9912的系统时钟频率。

由式(1)得到:

FTW=round[248(fDDS/fs)] (2)

例如,当fs=1 GHz,fDDS=19.44 MHz,则FTW=5 471 873 547 255(即0x04FA05143BF7)。

输出信号相位与相位控制字关系为:

△φ=2П(△phase/214) (3)

式中:△φ为AD9912输出信号相位;△phase为相位控制字。由于信号源需要应用于高频石英晶体测试系统中,所以,不能只输出一个固定频率的信号,必须输出扫频信号。测试之前,通过健盘或触摸屏输入待测晶体的标称频率、起始扫描频率、终止扫描频率、扫描步进频率,处理器根据式(2)算法,由扫描步进频率计算出扫描步进控制字(以下称为FTWstep)。图8所示为信号源应用于高频石英晶体测试系统的软件流程图。

3 实验结果

信号源的精度和稳定度直接影响到测试系统测量石英晶体频率的精度和稳定度。因此,使用CNT-90型频率计测量本系统信号源输出的信号频率。实验结果表明,信号源输出信号频率的精度高于±0.1 ppm,频率的稳定度高于±0.1ppm,实验数据如表1所示。

表中,f为设定的频率值;f为实际测量的频率平均值;△f/f为相对偏差。

4 结语

本设计成功地把DDS技术应用到高频石英晶体测试系统中。实现了基于DDS技术的宽带信号源。该信号源具有输出频率范围宽、精度高、稳定度高、频率分辨率高,频率切换速度快的特点,从而满足了高频石英晶体测试系统对信号源的要求。

上一篇:利用ARM处理器LPC1112设计LED电子胸牌

下一篇:基于FFmpeg的远程视频监控系统编解码

推荐阅读最新更新时间:2024-03-16 13:47

设计资源 培训 开发板 精华推荐

- 有奖直播:ADI在中国能源互联网应用中的技术及产品 1月8日上午10:00-11:30 准时开启!

- 安世半导体新能源应用探索站,闯关赢好礼!

- ADI•世健工业嘉年华—有奖直播:ADI赋能工业4.0—助力PLC/DCS技术创新

- 【EE团】抢先体验 ST最新STM32F0308-DISCOVERY开发工具!

- TE可穿戴解决方案助你打造暖心大白,答题赢TTI好礼

- 瑞萨电子100套开发套件等你来抢

- 有奖直播:万物互联 -世健公司携手Microchip专家,共同探讨IoT解决方案

- 看视频赢京东卡 | PI无刷直流电机学习中心正式上线

- 下载有礼:看“智””造“热”侦探 FLIR ETS320 红外热像仪如何纠错!

- 为你点赞——我最爱有“干货”的博文

模拟集成电路应用基础 (诸林裕)

模拟集成电路应用基础 (诸林裕) 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号