#include "msp430f2272.h"

int yu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,

0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

int i,j,k,temp,dat,ms;

void delay(int ms)

{

while(ms--)

for(i=0;i<2;i++);

}

int main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

P1DIR |=0x0f;

P2DIR =0xff;

P1IE |=0xf0;

P1IES |=0xf0;

P2OUT=yu[0];

P1IFG =0x00;

_EINT();

temp=0xfe;

while(1)

{

temp=0xfe;

P1OUT=temp;

delay(5);

temp=0xfd;

P1OUT=temp;

delay(5);

temp=0xfb;

P1OUT=temp;

delay(5);

temp=0xf7;

P1OUT=temp;

delay(5);

}

}

#pragma vector=PORT1_VECTOR

__interrupt void Port_ISR(void)

{

switch(temp)

{

case 0xfe:

{

if(P1IFG==BIT4)dat=0;

if(P1IFG==BIT5)dat=1;

if(P1IFG==BIT6)dat=2;

if(P1IFG==BIT7)dat=3;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfd:

{

if(P1IFG==BIT4)dat=4;

if(P1IFG==BIT5)dat=5;

if(P1IFG==BIT6)dat=6;

if(P1IFG==BIT7)dat=7;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfb:

{

if(P1IFG==BIT4)dat=8;

if(P1IFG==BIT5)dat=9;

if(P1IFG==BIT6)dat=10;

if(P1IFG==BIT7)dat=11;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xf7:

{

if(P1IFG==BIT4)dat=12;

if(P1IFG==BIT5)dat=13;

if(P1IFG==BIT6)dat=14;

if(P1IFG==BIT7)dat=15;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

default:break;

}

}

/*********************************************************/

#include "msp430f2272.h"

int yu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,

0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

int i,j,k,temp,dat,ms;

void delay(int ms)

{

while(ms--)

for(i=0;i<2;i++);

}

int main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

P1DIR |=0x0f;

P2DIR =0xff;

P1REN |=0xf0;

P1IE |=0xf0;

P1IES |=0xf0;

P2OUT=~yu[6];

P1IFG =0x00;

_EINT();

temp=0xfe;

while(1)

{

temp=0xfe;

P1OUT=temp;

delay(5);

temp=0xfd;

P1OUT=temp;

delay(5);

temp=0xfb;

P1OUT=temp;

delay(5);

temp=0xf7;

P1OUT=temp;

delay(5);

}

}

#pragma vector=PORT1_VECTOR

__interrupt void Port_ISR(void)

{

switch(temp)

{

case 0xfe:

{

if((P1IFG|0xef)==0xff)dat=0;

if((P1IFG|0xdf)==0xff)dat=1;

if((P1IFG|0xbf)==0xff)dat=2;

if((P1IFG|0x7f)==0xff)dat=3;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfd:

{

if((P1IFG|0xef)==0xff)dat=4;

if((P1IFG|0xdf)==0xff)dat=5;

if((P1IFG|0xbf)==0xff)dat=6;

if((P1IFG|0x7f)==0xff)dat=7;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfb:

{

if((P1IFG|0xef)==0xff)dat=8;

if((P1IFG|0xdf)==0xff)dat=9;

if((P1IFG|0xbf)==0xff)dat=10;

if((P1IFG|0x7f)==0xff)dat=11;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xf7:

{

if((P1IFG|0xef)==0xff)dat=12;

if((P1IFG|0xdf)==0xff)dat=13;

if((P1IFG|0xbf)==0xff)dat=14;

if((P1IFG|0x7f)==0xff)dat=15;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

default:break;

}

}

#include "msp430f2272.h"

int yu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,

0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

int i,j,k,temp,dat,ms;

void delay(int ms)

{

while(ms--)

for(i=0;i<2;i++);

}

int main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

P1DIR |=0x0f;

P2DIR =0xff;

P1REN |=0xf0;

P1IE |=0xf0;

P1IES |=0xf0;

P2OUT=~yu[6];

P1IFG =0x00;

_EINT();

temp=0xfe;

while(1)

{

temp=0xfe;

P1OUT=temp;

delay(5);

temp=0xfd;

P1OUT=temp;

delay(5);

temp=0xfb;

P1OUT=temp;

delay(5);

temp=0xf7;

P1OUT=temp;

delay(5);

}

}

#pragma vector=PORT1_VECTOR

__interrupt void Port_ISR(void)

{

if(temp==0xfe)

{

if((P1IFG|0xef)==0xff)dat=0;

if((P1IFG|0xdf)==0xff)dat=1;

if((P1IFG|0xbf)==0xff)dat=2;

if((P1IFG|0x7f)==0xff)dat=3;

P2OUT =~yu[dat];

P1IFG=0x00;

}

if(temp==0xfd)

{

if((P1IFG|0xef)==0xff)dat=4;

if((P1IFG|0xdf)==0xff)dat=5;

if((P1IFG|0xbf)==0xff)dat=6;

if((P1IFG|0x7f)==0xff)dat=7;

P2OUT =~yu[dat];

P1IFG=0x00;

}

if(temp==0xfb)

{

if((P1IFG|0xef)==0xff)dat=8;

if((P1IFG|0xdf)==0xff)dat=9;

if((P1IFG|0xbf)==0xff)dat=10;

if((P1IFG|0x7f)==0xff)dat=11;

P2OUT =~yu[dat];

P1IFG=0x00;

}

if(temp==0xf7)

{

if((P1IFG|0xef)==0xff)dat=12;

if((P1IFG|0xdf)==0xff)dat=13;

if((P1IFG|0xbf)==0xff)dat=14;

if((P1IFG|0x7f)==0xff)dat=15;

P2OUT =~yu[dat];

P1IFG=0x00;

}

}

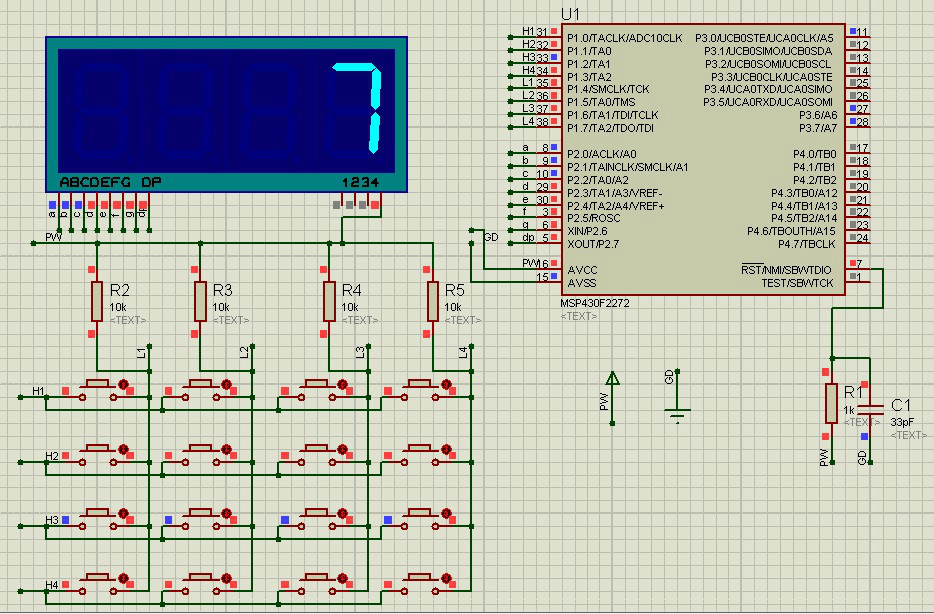

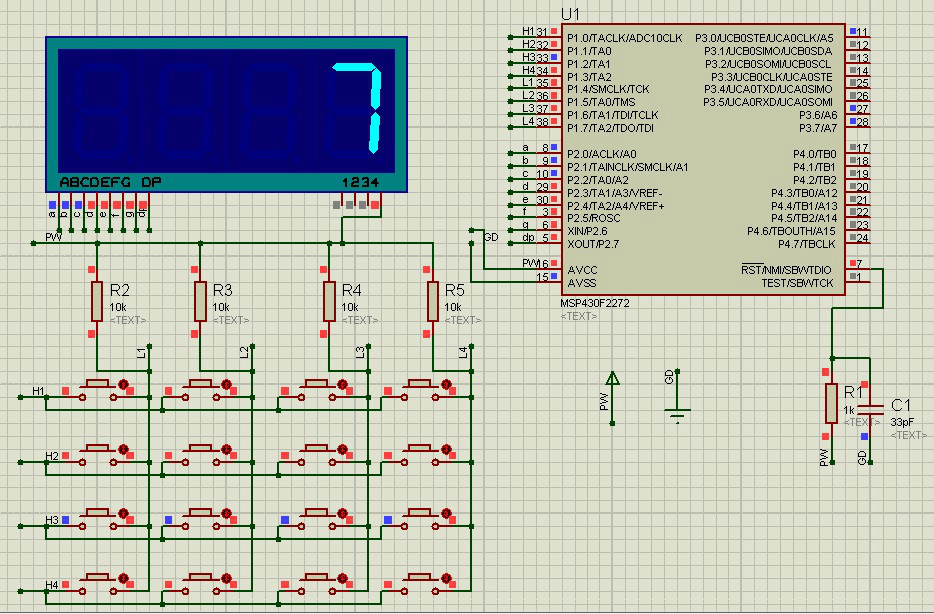

关键字:MSP430f2272 单片机 中断控制

引用地址:MSP430f2272单片机中断控制4X4键盘程序

int yu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,

0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

int i,j,k,temp,dat,ms;

void delay(int ms)

{

while(ms--)

for(i=0;i<2;i++);

}

int main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

P1DIR |=0x0f;

P2DIR =0xff;

P1IE |=0xf0;

P1IES |=0xf0;

P2OUT=yu[0];

P1IFG =0x00;

_EINT();

temp=0xfe;

while(1)

{

temp=0xfe;

P1OUT=temp;

delay(5);

temp=0xfd;

P1OUT=temp;

delay(5);

temp=0xfb;

P1OUT=temp;

delay(5);

temp=0xf7;

P1OUT=temp;

delay(5);

}

}

#pragma vector=PORT1_VECTOR

__interrupt void Port_ISR(void)

{

switch(temp)

{

case 0xfe:

{

if(P1IFG==BIT4)dat=0;

if(P1IFG==BIT5)dat=1;

if(P1IFG==BIT6)dat=2;

if(P1IFG==BIT7)dat=3;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfd:

{

if(P1IFG==BIT4)dat=4;

if(P1IFG==BIT5)dat=5;

if(P1IFG==BIT6)dat=6;

if(P1IFG==BIT7)dat=7;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfb:

{

if(P1IFG==BIT4)dat=8;

if(P1IFG==BIT5)dat=9;

if(P1IFG==BIT6)dat=10;

if(P1IFG==BIT7)dat=11;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xf7:

{

if(P1IFG==BIT4)dat=12;

if(P1IFG==BIT5)dat=13;

if(P1IFG==BIT6)dat=14;

if(P1IFG==BIT7)dat=15;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

default:break;

}

}

/*********************************************************/

#include "msp430f2272.h"

int yu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,

0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

int i,j,k,temp,dat,ms;

void delay(int ms)

{

while(ms--)

for(i=0;i<2;i++);

}

int main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

P1DIR |=0x0f;

P2DIR =0xff;

P1REN |=0xf0;

P1IE |=0xf0;

P1IES |=0xf0;

P2OUT=~yu[6];

P1IFG =0x00;

_EINT();

temp=0xfe;

while(1)

{

temp=0xfe;

P1OUT=temp;

delay(5);

temp=0xfd;

P1OUT=temp;

delay(5);

temp=0xfb;

P1OUT=temp;

delay(5);

temp=0xf7;

P1OUT=temp;

delay(5);

}

}

#pragma vector=PORT1_VECTOR

__interrupt void Port_ISR(void)

{

switch(temp)

{

case 0xfe:

{

if((P1IFG|0xef)==0xff)dat=0;

if((P1IFG|0xdf)==0xff)dat=1;

if((P1IFG|0xbf)==0xff)dat=2;

if((P1IFG|0x7f)==0xff)dat=3;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfd:

{

if((P1IFG|0xef)==0xff)dat=4;

if((P1IFG|0xdf)==0xff)dat=5;

if((P1IFG|0xbf)==0xff)dat=6;

if((P1IFG|0x7f)==0xff)dat=7;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xfb:

{

if((P1IFG|0xef)==0xff)dat=8;

if((P1IFG|0xdf)==0xff)dat=9;

if((P1IFG|0xbf)==0xff)dat=10;

if((P1IFG|0x7f)==0xff)dat=11;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

case 0xf7:

{

if((P1IFG|0xef)==0xff)dat=12;

if((P1IFG|0xdf)==0xff)dat=13;

if((P1IFG|0xbf)==0xff)dat=14;

if((P1IFG|0x7f)==0xff)dat=15;

P2OUT =~yu[dat];

P1IFG=0x00;

break;

}

default:break;

}

}

#include "msp430f2272.h"

int yu[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,

0x7f,0x6f,0x77,0x7c,0x39,0x5e,0x79,0x71};

int i,j,k,temp,dat,ms;

void delay(int ms)

{

while(ms--)

for(i=0;i<2;i++);

}

int main( void )

{

// Stop watchdog timer to prevent time out reset

WDTCTL = WDTPW + WDTHOLD;

P1DIR |=0x0f;

P2DIR =0xff;

P1REN |=0xf0;

P1IE |=0xf0;

P1IES |=0xf0;

P2OUT=~yu[6];

P1IFG =0x00;

_EINT();

temp=0xfe;

while(1)

{

temp=0xfe;

P1OUT=temp;

delay(5);

temp=0xfd;

P1OUT=temp;

delay(5);

temp=0xfb;

P1OUT=temp;

delay(5);

temp=0xf7;

P1OUT=temp;

delay(5);

}

}

#pragma vector=PORT1_VECTOR

__interrupt void Port_ISR(void)

{

if(temp==0xfe)

{

if((P1IFG|0xef)==0xff)dat=0;

if((P1IFG|0xdf)==0xff)dat=1;

if((P1IFG|0xbf)==0xff)dat=2;

if((P1IFG|0x7f)==0xff)dat=3;

P2OUT =~yu[dat];

P1IFG=0x00;

}

if(temp==0xfd)

{

if((P1IFG|0xef)==0xff)dat=4;

if((P1IFG|0xdf)==0xff)dat=5;

if((P1IFG|0xbf)==0xff)dat=6;

if((P1IFG|0x7f)==0xff)dat=7;

P2OUT =~yu[dat];

P1IFG=0x00;

}

if(temp==0xfb)

{

if((P1IFG|0xef)==0xff)dat=8;

if((P1IFG|0xdf)==0xff)dat=9;

if((P1IFG|0xbf)==0xff)dat=10;

if((P1IFG|0x7f)==0xff)dat=11;

P2OUT =~yu[dat];

P1IFG=0x00;

}

if(temp==0xf7)

{

if((P1IFG|0xef)==0xff)dat=12;

if((P1IFG|0xdf)==0xff)dat=13;

if((P1IFG|0xbf)==0xff)dat=14;

if((P1IFG|0x7f)==0xff)dat=15;

P2OUT =~yu[dat];

P1IFG=0x00;

}

}

上一篇:STC12系列读取DS1302间断乱码

下一篇:verilog同步复位PK异步复位

推荐阅读最新更新时间:2024-03-16 13:51

8051单片机基础7:函数的特殊用法

参考来源:Keil Help uVision Help Cx51 Compiler User’s Guide Language Extensions Function Declarations 函数声明/定义时,与标准C语言存在一定差异,主要为以下几个方面: 声明函数为中断处理函数入口 选择函数使用的8051通用寄存器组 配置函数的内存模型 声明可重入的函数 函数声明/定义规范 return_type funcname ( args ) small / compact / large reentrant interrupt x

[单片机]

液晶显示模块DMF-50081在单片机系统中的应用

摘要:通过一个小型监控单元的设计实践,详细介绍了一种使用89C51单片机和大屏幕液晶显示模块DMF-50081,进行图形和文本混合显示的软硬件设计思路和编程技巧。给出了DMF-50081与单片机的硬件连接电路和部分程序代码。

关键词:单片机 SED1335控制器 图形汉字 DMF-50081

香港精电公司的DMF-50081点阵图形液晶显示模块是由大屏幕LCD液晶显示器、SED1335控制器、CCFL背光逆变器和DC-DC显示驱动电源四部分组成。它与同类液晶显示模块相比,具有显示信息量大、亮度高、微功耗、体积小、质量轻、超薄等诸多优点,在移动通讯、仪器仪表、电子设备、家用电器等各方面有着十分广泛的用途。

下面以DMF-50

[应用]

SPCE061A型单片机在土木工程测温仪中的应用与设计

1 引言 在土木工程中,许多大型的桥梁和大坝都是采用现场浇注的钢筋混凝土结构。在此类工程中混凝土浇注以后,由于水泥的水化热作用,混凝土内温度将逐渐上升,混凝土厚度的差异导致不同的温升,形成温度梯度并产生温度应力。与外力作用于结构时引起的应力不同,混凝土的温度应力是由变形引起的;混凝土的导热性能较差,浇注初期其强度和弹性模量都较低,温度变化引起的变形不明显。随着龄期的增长,混凝土的强度和弹性模量提高,对混凝土变形的约束越来越大,以致产生很大的拉应力,当混凝土的抗拉强度不足以抵抗这种拉应力时,开始出现温度裂纹。这将严重影响土木工程的质量,所以很有必要对混凝土浇注后的一段时期内的温度参数进行监测,可为其合理的浇注和养护提供可靠的数据

[单片机]

用51单片机做一个电子钟

学了一个多月51了,终于整了个电子钟出来,个人感觉还是比较有趣的。 需要注意的是我用的是普中的板子,板子类型不同,io口的功能可能会有所差异。然后我这个k1开关和k2开关是接反了的,原本k1应该是接P3^0,k2接P3^1的,结果我一测试才知道k1接到了P3^1,k2接到P3^0了,不过这不要紧,用sbit定义位变量时注意换一下就可以了。然后大概讲讲功能,用8个数码管显示目前时间和闹铃时间,然后用4个独立按键对目前时间和闹铃时间进行调整(k2是加,k3是减 ,k4是用来停止闹铃的),第一次按k1是对目前时间秒数调整,第2次按k1是对目前时间分钟数调整,第三次按k1是对目前时间小时数调整,第4次按k1是对闹铃秒数调整,第5次按k

[单片机]

用AT89C51单片机控制步进电机的汇编源程序

下面程序完成的主要功能:实现步进电机的正反转,加速、减速;显示电机转速(转速级别)和工作状态(正转、反转、不转)。 源程序 SPEED EQU 10H ;SPEED为转速等级标志,共7级,即1~7 FX EQU 11H ;FX 为方向标志 COUNT EQU 12H ;COUNT中断次数标志 ORG 0000H AJMP MAIN ORG 0003H ;外部中断0入口地址,加速子程序 AJMP UP ORG 0013H ;外部中断1入口地址,减速子程序 AJMP DOWN ORG 000BH ;定时器0中断入口地址,控制中断次数来达到控制转速 AJMP ZDT0

[单片机]

单片机与单片机串口通讯程序

单片机 与单片机串口通讯程序 #include reg51.h #define uchar unsigned char #define SLAVE 0x00 #define BN 16 uchar idata tdata ; uchar idata rdata ; bit trdy; bit rrdy; void main(void) { TMOD=0x20; //定时器T1为模式2 TL1=0xfd; //定时器初值 TH1=0xfd; PCON=0x00; TR1=1; SCON=0xf0; //串行口方式3 ES=1;EA=1;

[单片机]

51单片机基础之DS1302

代码: main.c 文件 /* DS1302时钟 */ #include smg.h #include ds1302.h void main() { u8 time_buf ; //这个数组用来存储需要现实的内容 ds1302_init();//初始化DS1302 while(1) { ds1302_read_time(); //虽然不知道这个是干嘛的,但是知道怎么改。 time_buf =gsmg_code /16]; time_buf =gsmg_code &0x0f]; time_buf =0x40; //显示一杠 time_buf =gs

[单片机]

单片机实验-数据传送

#include reg52.h #define LENTH 16 unsigned char idata dADDR _at_ 0x30; // 定义数组dADDR,大小为16 Byte, 首地址为 0x30 unsigned char xdata xADDR _at_ 0x3000; // 定义数组xADDR,大小为16 Byte, 首地址为 0x3000 void main() { unsigned int i; // 利用循环,将i循环加一,并赋值给0x30~0x3F单元 for (i = 0; i LENTH; i++) dADDR = i + 1; // 利用循环,将dADDR数组中的值赋值

[单片机]

设计资源 培训 开发板 精华推荐

最新单片机文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

厂商技术中心

随便看看

单片机创新实践应用.

单片机创新实践应用.

京公网安备 11010802033920号

京公网安备 11010802033920号