1. PHASE LOCKED LOOP(PLL)

S3C6410里包含三个PLL(锁相环),APLL, MPLL, EPLL,通过设置它们将输入时钟同步输出达到操作CPU的工作频率的目的。如图1-1所示。

Voltage Controlled Oscillator (VCO)P[5:0]位来设置FIN进行分频。通过设置Main-Divider分频数,分频压控振荡器产生的输出时钟频率,分频之后的低频进入鉴相器ScalerS[2:0]位设置PLL的输出时钟频率都可以通过

PLL的时钟选择和输入参照时钟

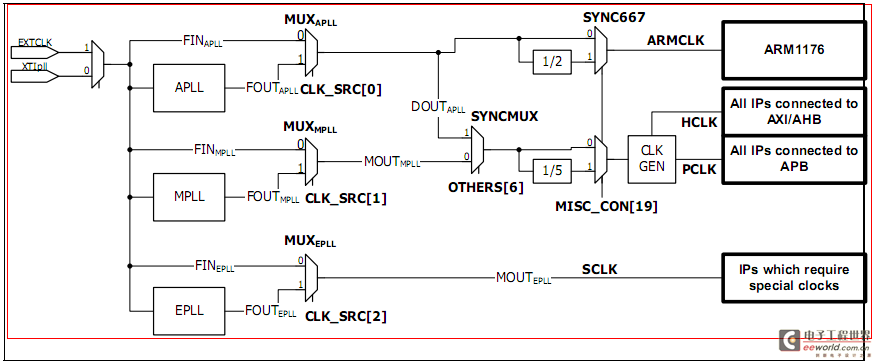

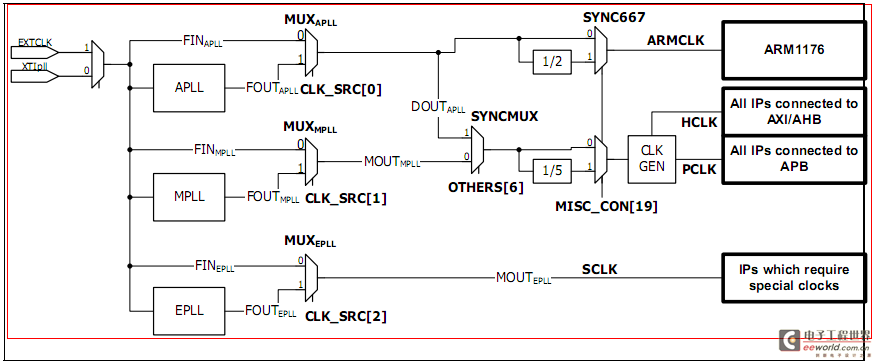

图1-2描述了时钟产生逻辑。S3C6410有三个PLL锁相环,工作时钟也分为三组,APLL用来为ARM芯片提供工作时钟,MPLL为AXI,AHB,APB总线上设备提供工作时钟,EPLL为特殊外设,如:视频解码器,图片编码器等,提供工作时钟。

图1-2时钟产生逻辑单元

CLK_SRC寄存器的低三位CLK_SRC[2:0]分别控制三种工作时钟。当对应位被置位,则产生对应PLL的工作时钟。否则,不会产生对应的PLL工作时钟。

3. 三种工作时钟的产生

ARM1176最高产生667Mhz的工作频率。用户可以通过设置内部时钟分频器的值来控制输出工作时钟,而不用修改PLL的工作频率。分频器可以选择1~16的分频数。ARM内核可以通过修改分频器的值来减少系统电源的损耗。

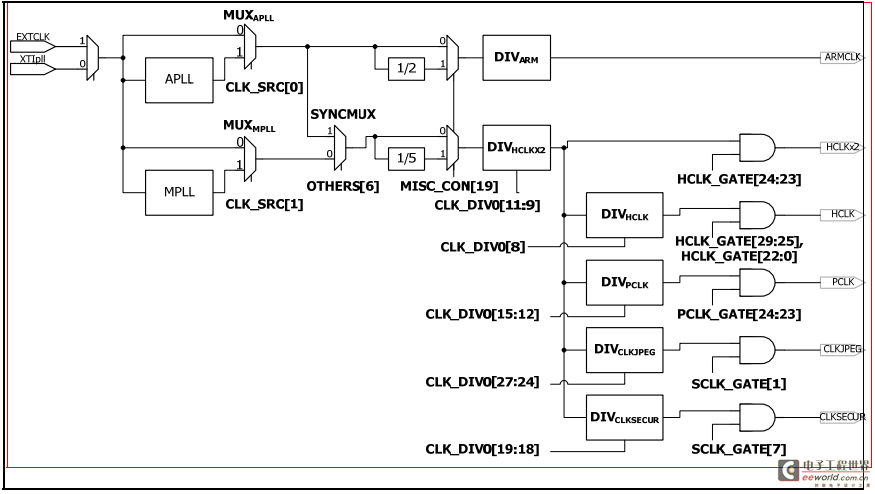

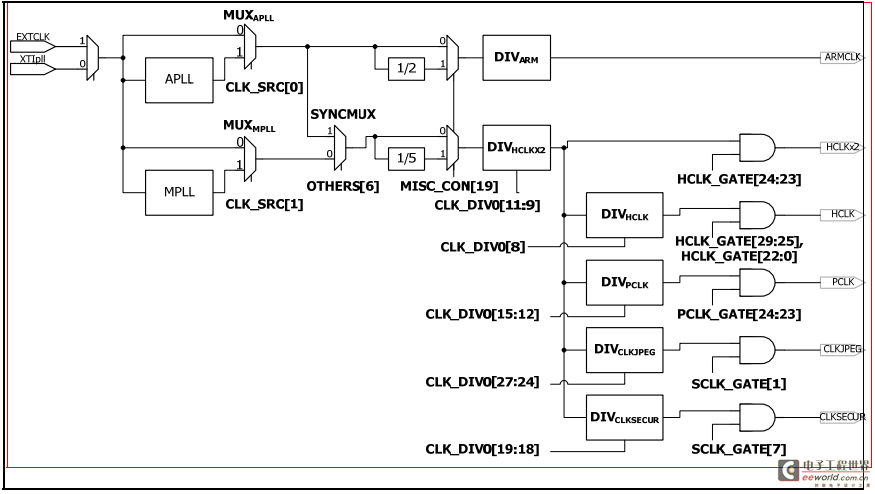

S3C6410内部含有AXI,AHB和APB总线,通过不同的总线控制不同的外设,关闭总线上的时钟频率可以达到系统节能的目的。AXI,AHB总线最高工作在133MHz频率下,APB总线最高工作在66MHz频率下。由于APB和AXI,AHB总线上二者工作频率不一致,在这两种总线上进行数据同步传输时会采用特殊逻辑单元,如图1-3所示。

图1-3系统总线工作频率设置

HCLKX2时钟由DDR0,DDR1两个DDR控制器产生,其最高可以以266MHz频率发送和接收数据。每个HCLKX2时钟可以根据用户需要分别被关闭掉来减少系统损耗。AHB总线上的时钟由DIV(HCLK)分频器分频后输出,同样AHB总线上的外设也可以被关闭掉以节省电源消耗。HCLK_GATE寄存器用来关闭工作在HCLKX2和HCLK时钟上的外设。

慢速设备连接在APB总线上。APB时钟最高工作在66MHz,通过DIV(PCLk)分频器来进行分频设置,通过设置PCLK_GATE寄存器来关闭对应的APB总线上的外设。根据S3C6410硬件手册说明,AHB总线和APB总线上的频率必须是偶数,例如,如果DIV(HCLK)对应控制位CLK_DIV[8]设置为1,则DIV(PCLK)对应位CLK_DIV0[15:12]必须设置为1,3,5,…等奇数。否则,APB总线上的外设不能正解的进行数据传输。

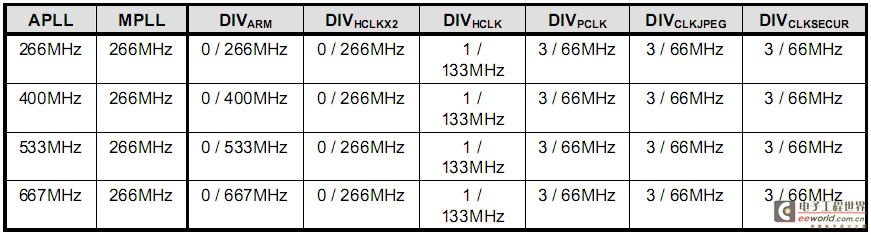

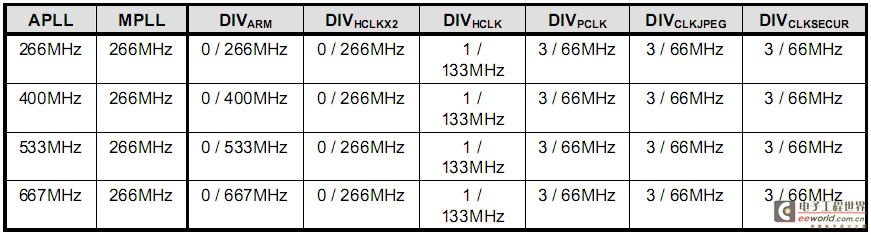

AHB总线上的JPEG和安全相关子系统不能工作在133MHz,AHB总线专门为这样低频子系统提供低频工作时钟,通过设置DIV(CLKJPEG)和DIV(CLKSECUR)分频位来设置其工作频率。因此,同样在APB总线上也有类似的这种限制设定,DIV(CLKJPEG)和DIV(CLKSECUR)对应的CLK_DIV0[27:24]分频位和CLK_DIV0[19:18]分频位必须是奇数,二者的和是偶数。如表1-1所示,官方给出了推荐的设置参数。

表1-1官方推荐参数

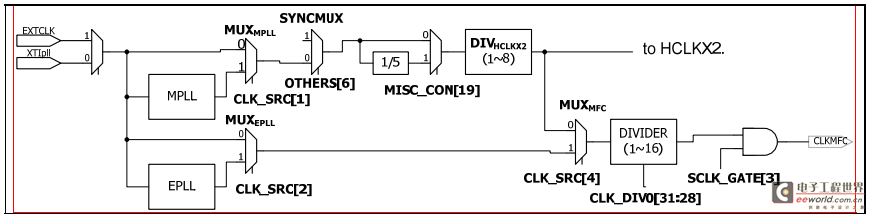

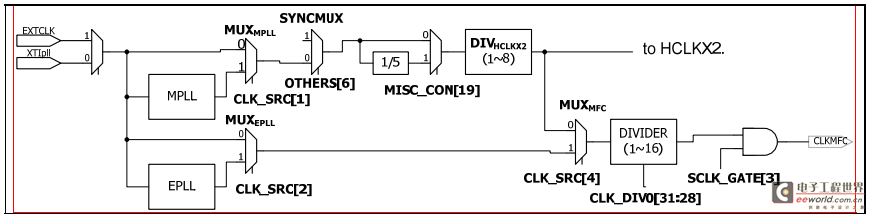

4. MFC模块时钟的产生

MFC模块需要特殊的时钟,如图1-5所示。

图1-5 MFC时钟产生逻辑

MFC时钟源可以从HCLKX2和MOUT(EPLL)中选择。MFC的工作时钟使用HCLKX2来分频。默认HCLKX2时钟频率为266MHz。因此,CLK_DIV0[31:28]必须设置为b0001来产生MFC工作的133MH时钟。当MFC模块不需要工作在高性能模式下时,有两种方式可以减少MFC模块工作频率来达到减少MFC模块的功耗。第一种方式是设置CLK_SRC[4]使用EPLL的输出时钟,另外一种方式是设置CLK_DIV0[31:28]的分频数,同时,设置CLK_SRC[4]位,这样低频工作时钟就可以提供给MFC模块。EPLL输出时钟是与HCLKX2和HCLK独立的。

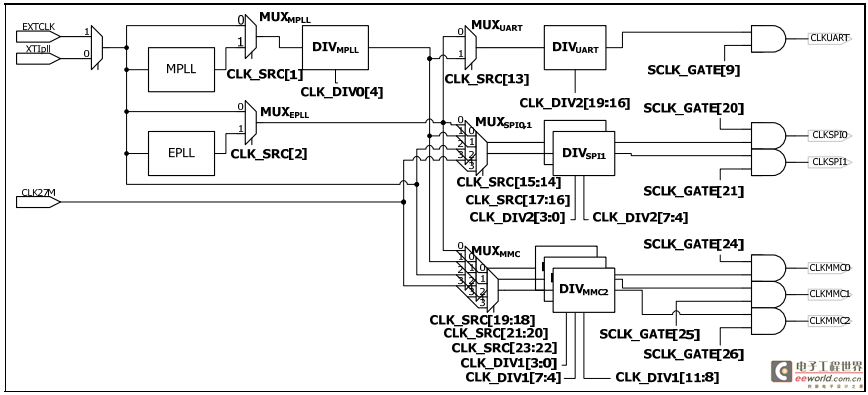

5. UART,SPI,MMC工作时钟的产生

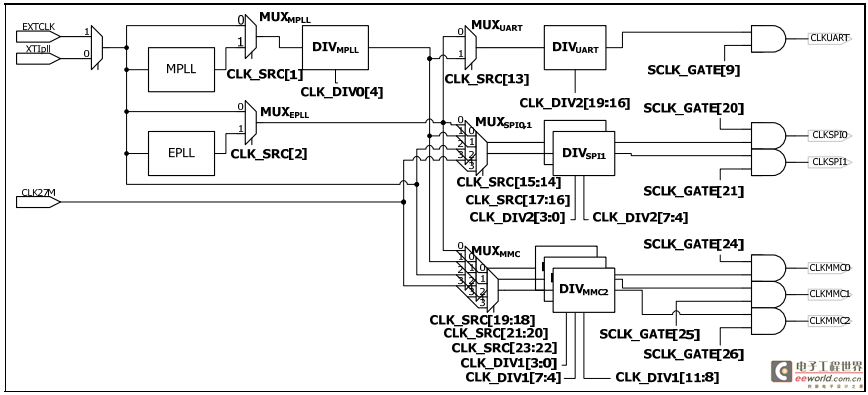

如图1-6所示,是上述三种外设工作时钟逻辑。

图1-6 UART,SPI,MMC工作时钟逻辑模块

通过设置CLK_DIV2[19:16]位来设置UART的工作频率的分频数,通过SCLK_GATE[9]来开启关闭UART时钟源。

该模块中有一个额外的时钟源CLK27M,使用该时钟源可以提供更多的可选工作时钟。

6. 时钟的开启/关闭控制

HCLK_GATE,PCLK_GATE和SCLK_GATE用来控制三种时钟源的产生,如果对应的位被设置,对应时钟就会产生。

HCLK_GATE控制HCLK总线上的外设工作时钟的产生,PCLK_GATE控制PCLK总线上的外设工作时钟的产生,PCLK总线上的外设需要特定的时钟,它们通过SCLK_GATE来设置。

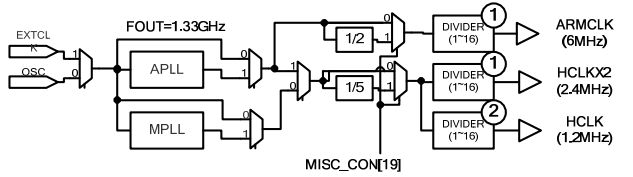

7. 同步667MH操作模式

根据S3C6410硬件手册,ARMCLK和HCLK的时钟比必须是整数,用来同步ARM内核和AXI总线接口二者的时钟。S3C6410没有对CPU工作在533MHz做限制,ARMCLK = 533MHz,HCLKX2=266MHz,HCLK=133MH,不过,对于工作在533MHz以上时,例如667Mhz时,只能支持1:2.5:5的时钟比(ARMCLK = 667MHz,HCLKX2=266MHz,HCLK=133MH)

8. 时钟分频

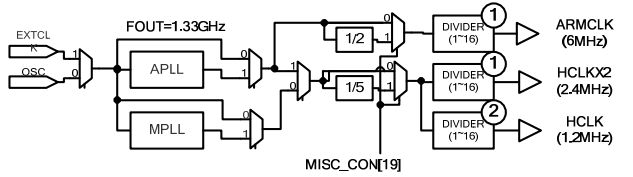

图1-7时钟分频模块

如图1-7所示,时钟分频模块产生三种时钟,ARMCLK,HCLKX2,HCLK。时钟分频器包含两部分,预分频器组和后分频器组,预分频器包含一个1/2预分频器和1/5预分频器,这两个分频器是固定的不能被软件配置,而后分频器可以通过配置CLK_DIV0寄存器方式进行配置。当MISC_CON的SYNC667MHz位被设置时,两个预分频器同时工作,产生APLL的分频经过预分频器分频的时钟,如果APLL的FOUT输出频率为1.33GHz,预分频器ARMCLK的输出为667Mhz,预分频器HCLK的输出为266MHz。这样经过分频的时钟可以通过CLK_DIV0寄存器进行配置。

我们打算将ARM内核时钟设置为官方推荐的稳定的533MHz,让APLL为AHB,APB输出工作频率。让MPLL为UART等外设提供工作频率,EPLL不工作。同时设置HCLKX2为266MHz,HCLK为133MHz,PCLK为66.5MHz,UART工作时钟为66.5MHz。

1. 选择HCLKX2, HCLK, PCLK的时钟源,由图1-2可知其时钟源可以通过OTHER[6]选择是由DOUT_APLL还是MOUT_MPLL,我们选择从DOUT_APLL。

2. 设置变频锁定时间,当系统时钟修改之后要经过段LOCK时间

3. 设置ARMCLK, HCLKX2, HCLK, PCLK的分频

各种频率的关系如图1-3所述:

APLL或MPLL产生的输出频率经过OTHER[6]选择之后再经过MISC_CON[19]选择是否被1/5分频,产生的输出频率进入DIV_HCLKx2,根据CLK_DIV0的不同位设置HCLKX2,HCLK,PCLK,CLKJPEG,CLKSECUR的输出频率。其值设置情况如CLK_DIV0寄存器描述内容所述。

l 我们将MPLL选择DOUT_APLL,MISC_ON[19]不进行分频,DOUT_APLL产生的时钟(533MHz)直接进入到DIV_HCLKX2分频器中。

l 根据硬件手册可知,HCLKX2的频率固定为266MHz,所以HCLKX2_RATIO设置为0b1

l HCLK上挂接有内存,Mobile DDR内存最高工作在133MHz,所以HCLK最高主频设置为HCLKX2的1/2,即:HCLK_RATIO = 0b1

l 设置PCLK上的工作频率为66.5MHz,即:PCLK_RATIO = 0b11

l 设置ARM内核工作频率为553MHz,即:ARM_RATIO = 0b0

l 设置DOUT_MPLL为266MHz,为后面UART提供时钟源,即:MPLL_RATIO = 0b0

l 其它时钟频率保持默认值

4. 设置UART工作时钟

由图1-6可知,通过设置CLK_SRC[1]选择DOUT_MPLL的工作时钟是否进行倍频,通过设置CLK_DIV0[4]对时钟进行分频,再通过CLK_SRC[13]选择UART的工作时钟源,设置CLK_DIV2[19:16]位用于分频UART工作时钟。由前面可知DOUT_MPLL = 266MHz,UART选择其作为自己工作时钟源,则对其进行1/4分频可以得到66.5MHz。

如下表可知:设置寄存器CLK_DIV2[19:16] = 0b11,同时还要设置CLK_SRC[13] = 0b1即可。

5. 使能APLL,EPLL锁相环

根据硬件手册上的说明设置APLL, EPLL的M,D,S分频数。

APLL产生533MHz的FOUT_APLL

EPLL产生266MHz的MOUT_EPLL

6. 设置对应时钟源寄存器,为各种外设提供时钟频率

关键字:S3C6410 时钟初始化

引用地址:S3C6410 时钟初始化

S3C6410里包含三个PLL(锁相环),APLL, MPLL, EPLL,通过设置它们将输入时钟同步输出达到操作CPU的工作频率的目的。如图1-1所示。

Voltage Controlled Oscillator (VCO)P[5:0]位来设置FIN进行分频。通过设置Main-Divider分频数,分频压控振荡器产生的输出时钟频率,分频之后的低频进入鉴相器ScalerS[2:0]位设置PLL的输出时钟频率都可以通过

PLL的时钟选择和输入参照时钟

图1-2描述了时钟产生逻辑。S3C6410有三个PLL锁相环,工作时钟也分为三组,APLL用来为ARM芯片提供工作时钟,MPLL为AXI,AHB,APB总线上设备提供工作时钟,EPLL为特殊外设,如:视频解码器,图片编码器等,提供工作时钟。

图1-2时钟产生逻辑单元

CLK_SRC寄存器的低三位CLK_SRC[2:0]分别控制三种工作时钟。当对应位被置位,则产生对应PLL的工作时钟。否则,不会产生对应的PLL工作时钟。

3. 三种工作时钟的产生

ARM1176最高产生667Mhz的工作频率。用户可以通过设置内部时钟分频器的值来控制输出工作时钟,而不用修改PLL的工作频率。分频器可以选择1~16的分频数。ARM内核可以通过修改分频器的值来减少系统电源的损耗。

S3C6410内部含有AXI,AHB和APB总线,通过不同的总线控制不同的外设,关闭总线上的时钟频率可以达到系统节能的目的。AXI,AHB总线最高工作在133MHz频率下,APB总线最高工作在66MHz频率下。由于APB和AXI,AHB总线上二者工作频率不一致,在这两种总线上进行数据同步传输时会采用特殊逻辑单元,如图1-3所示。

图1-3系统总线工作频率设置

HCLKX2时钟由DDR0,DDR1两个DDR控制器产生,其最高可以以266MHz频率发送和接收数据。每个HCLKX2时钟可以根据用户需要分别被关闭掉来减少系统损耗。AHB总线上的时钟由DIV(HCLK)分频器分频后输出,同样AHB总线上的外设也可以被关闭掉以节省电源消耗。HCLK_GATE寄存器用来关闭工作在HCLKX2和HCLK时钟上的外设。

慢速设备连接在APB总线上。APB时钟最高工作在66MHz,通过DIV(PCLk)分频器来进行分频设置,通过设置PCLK_GATE寄存器来关闭对应的APB总线上的外设。根据S3C6410硬件手册说明,AHB总线和APB总线上的频率必须是偶数,例如,如果DIV(HCLK)对应控制位CLK_DIV[8]设置为1,则DIV(PCLK)对应位CLK_DIV0[15:12]必须设置为1,3,5,…等奇数。否则,APB总线上的外设不能正解的进行数据传输。

AHB总线上的JPEG和安全相关子系统不能工作在133MHz,AHB总线专门为这样低频子系统提供低频工作时钟,通过设置DIV(CLKJPEG)和DIV(CLKSECUR)分频位来设置其工作频率。因此,同样在APB总线上也有类似的这种限制设定,DIV(CLKJPEG)和DIV(CLKSECUR)对应的CLK_DIV0[27:24]分频位和CLK_DIV0[19:18]分频位必须是奇数,二者的和是偶数。如表1-1所示,官方给出了推荐的设置参数。

表1-1官方推荐参数

4. MFC模块时钟的产生

MFC模块需要特殊的时钟,如图1-5所示。

图1-5 MFC时钟产生逻辑

MFC时钟源可以从HCLKX2和MOUT(EPLL)中选择。MFC的工作时钟使用HCLKX2来分频。默认HCLKX2时钟频率为266MHz。因此,CLK_DIV0[31:28]必须设置为b0001来产生MFC工作的133MH时钟。当MFC模块不需要工作在高性能模式下时,有两种方式可以减少MFC模块工作频率来达到减少MFC模块的功耗。第一种方式是设置CLK_SRC[4]使用EPLL的输出时钟,另外一种方式是设置CLK_DIV0[31:28]的分频数,同时,设置CLK_SRC[4]位,这样低频工作时钟就可以提供给MFC模块。EPLL输出时钟是与HCLKX2和HCLK独立的。

5. UART,SPI,MMC工作时钟的产生

如图1-6所示,是上述三种外设工作时钟逻辑。

图1-6 UART,SPI,MMC工作时钟逻辑模块

通过设置CLK_DIV2[19:16]位来设置UART的工作频率的分频数,通过SCLK_GATE[9]来开启关闭UART时钟源。

该模块中有一个额外的时钟源CLK27M,使用该时钟源可以提供更多的可选工作时钟。

6. 时钟的开启/关闭控制

HCLK_GATE,PCLK_GATE和SCLK_GATE用来控制三种时钟源的产生,如果对应的位被设置,对应时钟就会产生。

HCLK_GATE控制HCLK总线上的外设工作时钟的产生,PCLK_GATE控制PCLK总线上的外设工作时钟的产生,PCLK总线上的外设需要特定的时钟,它们通过SCLK_GATE来设置。

7. 同步667MH操作模式

根据S3C6410硬件手册,ARMCLK和HCLK的时钟比必须是整数,用来同步ARM内核和AXI总线接口二者的时钟。S3C6410没有对CPU工作在533MHz做限制,ARMCLK = 533MHz,HCLKX2=266MHz,HCLK=133MH,不过,对于工作在533MHz以上时,例如667Mhz时,只能支持1:2.5:5的时钟比(ARMCLK = 667MHz,HCLKX2=266MHz,HCLK=133MH)

8. 时钟分频

图1-7时钟分频模块

如图1-7所示,时钟分频模块产生三种时钟,ARMCLK,HCLKX2,HCLK。时钟分频器包含两部分,预分频器组和后分频器组,预分频器包含一个1/2预分频器和1/5预分频器,这两个分频器是固定的不能被软件配置,而后分频器可以通过配置CLK_DIV0寄存器方式进行配置。当MISC_CON的SYNC667MHz位被设置时,两个预分频器同时工作,产生APLL的分频经过预分频器分频的时钟,如果APLL的FOUT输出频率为1.33GHz,预分频器ARMCLK的输出为667Mhz,预分频器HCLK的输出为266MHz。这样经过分频的时钟可以通过CLK_DIV0寄存器进行配置。

我们打算将ARM内核时钟设置为官方推荐的稳定的533MHz,让APLL为AHB,APB输出工作频率。让MPLL为UART等外设提供工作频率,EPLL不工作。同时设置HCLKX2为266MHz,HCLK为133MHz,PCLK为66.5MHz,UART工作时钟为66.5MHz。

1. 选择HCLKX2, HCLK, PCLK的时钟源,由图1-2可知其时钟源可以通过OTHER[6]选择是由DOUT_APLL还是MOUT_MPLL,我们选择从DOUT_APLL。

ldr r0, =CLOCK_BASE ;0x7e00f000

ldr r1, [r0, #OTHERS_OFFSET] ; 选择MPLL的时钟源

movr2, #0x40

orr r1, r1, r2

str r1, [r0, #OTHERS_OFFSET]

nop

nop

nop

nop

; 选择CPU的同步工作模式

ldr r2, =0x80

orr r1, r1, r2

str r1, [r0, #OTHERS_OFFSET]

;测试是否已经工作在同步模式下

check_syncack

ldr r1, [r0, #OTHERS_OFFSET]

ldr r2, =0xf00

and r1, r1, r2

cmpr1, #0xf00

bne check_syncack

ldr r1, [r0, #OTHERS_OFFSET] ; 选择MPLL的时钟源

movr2, #0x40

orr r1, r1, r2

str r1, [r0, #OTHERS_OFFSET]

nop

nop

nop

nop

; 选择CPU的同步工作模式

ldr r2, =0x80

orr r1, r1, r2

str r1, [r0, #OTHERS_OFFSET]

;测试是否已经工作在同步模式下

check_syncack

ldr r1, [r0, #OTHERS_OFFSET]

ldr r2, =0xf00

and r1, r1, r2

cmpr1, #0xf00

bne check_syncack

2. 设置变频锁定时间,当系统时钟修改之后要经过段LOCK时间

; 设置变频锁定时间

movr1, #0xff00

orr r1, r1, #0xff

str r1, [r0, #APLL_LOCK_OFFSET]

str r1, [r0, #MPLL_LOCK_OFFSET]

str r1, [r0, #EPLL_LOCK_OFFSET]

movr1, #0xff00

orr r1, r1, #0xff

str r1, [r0, #APLL_LOCK_OFFSET]

str r1, [r0, #MPLL_LOCK_OFFSET]

str r1, [r0, #EPLL_LOCK_OFFSET]

3. 设置ARMCLK, HCLKX2, HCLK, PCLK的分频

各种频率的关系如图1-3所述:

APLL或MPLL产生的输出频率经过OTHER[6]选择之后再经过MISC_CON[19]选择是否被1/5分频,产生的输出频率进入DIV_HCLKx2,根据CLK_DIV0的不同位设置HCLKX2,HCLK,PCLK,CLKJPEG,CLKSECUR的输出频率。其值设置情况如CLK_DIV0寄存器描述内容所述。

l 我们将MPLL选择DOUT_APLL,MISC_ON[19]不进行分频,DOUT_APLL产生的时钟(533MHz)直接进入到DIV_HCLKX2分频器中。

l 根据硬件手册可知,HCLKX2的频率固定为266MHz,所以HCLKX2_RATIO设置为0b1

l HCLK上挂接有内存,Mobile DDR内存最高工作在133MHz,所以HCLK最高主频设置为HCLKX2的1/2,即:HCLK_RATIO = 0b1

l 设置PCLK上的工作频率为66.5MHz,即:PCLK_RATIO = 0b11

l 设置ARM内核工作频率为553MHz,即:ARM_RATIO = 0b0

l 设置DOUT_MPLL为266MHz,为后面UART提供时钟源,即:MPLL_RATIO = 0b0

l 其它时钟频率保持默认值

; MPLL_RATIO = 0<<4, ARM_RATIO = 0

; DOUT_MPLL = MOUT_MPLL/(MPLL_RATIO + 1)

; 即 ARMCLK = DOUT_APLL / (ARM_RATIO + 1)

; 即 ARMCLK = 533MHz, DOUT_MPLL = 266MHz

; HCLKX2_RATIO = 1<<9 , HCLK_RATIO = 1<<8, PCLK_RATIO = 3<<12, HCLKX2IN = 533

; 即 HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) = 266

; 即 HCLK = HCLKX2 / (HCLK_RATIO + 1) = 133

; 即 PCLK = HCLKX2 / (PCLK_RATIO + 1) = 66.5

ldr r1, [r0, #CLK_DIV0_OFFSET]

bic r1, r1, #0xff00

bic r1, r1, #0xff

ldr r2, =0x3300

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET]

; DOUT_MPLL = MOUT_MPLL/(MPLL_RATIO + 1)

; 即 ARMCLK = DOUT_APLL / (ARM_RATIO + 1)

; 即 ARMCLK = 533MHz, DOUT_MPLL = 266MHz

; HCLKX2_RATIO = 1<<9 , HCLK_RATIO = 1<<8, PCLK_RATIO = 3<<12, HCLKX2IN = 533

; 即 HCLKX2 = HCLKX2IN / (HCLKX2_RATIO + 1) = 266

; 即 HCLK = HCLKX2 / (HCLK_RATIO + 1) = 133

; 即 PCLK = HCLKX2 / (PCLK_RATIO + 1) = 66.5

ldr r1, [r0, #CLK_DIV0_OFFSET]

bic r1, r1, #0xff00

bic r1, r1, #0xff

ldr r2, =0x3300

orr r1, r1, r2

str r1, [r0, #CLK_DIV0_OFFSET]

4. 设置UART工作时钟

由图1-6可知,通过设置CLK_SRC[1]选择DOUT_MPLL的工作时钟是否进行倍频,通过设置CLK_DIV0[4]对时钟进行分频,再通过CLK_SRC[13]选择UART的工作时钟源,设置CLK_DIV2[19:16]位用于分频UART工作时钟。由前面可知DOUT_MPLL = 266MHz,UART选择其作为自己工作时钟源,则对其进行1/4分频可以得到66.5MHz。

如下表可知:设置寄存器CLK_DIV2[19:16] = 0b11,同时还要设置CLK_SRC[13] = 0b1即可。

; 设置UART串口的分频数寄存器CLK_DIV2

ldr r1, [r0, #CLK_DIV2_OFFSET]

bic r1, r1, #0x70000

orr r1, r1, #0x30000 ; 设置其值为3,即CLKUART = CLKUARTIN / 4

str r1, [r0, #CLK_DIV2_OFFSET]

ldr r1, [r0, #CLK_DIV2_OFFSET]

bic r1, r1, #0x70000

orr r1, r1, #0x30000 ; 设置其值为3,即CLKUART = CLKUARTIN / 4

str r1, [r0, #CLK_DIV2_OFFSET]

5. 使能APLL,EPLL锁相环

根据硬件手册上的说明设置APLL, EPLL的M,D,S分频数。

APLL产生533MHz的FOUT_APLL

EPLL产生266MHz的MOUT_EPLL

;使能APLL锁相环,配置M,D,S分频数, according to Datasheet FOUT_APLL = 533 then

; APLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 1

ldr r1, = 0x810a0301

str r1, [r0, #APLL_CON_OFFSET]

; 使能MPLL锁相环,配置M,D,S分频数

; MPLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 2

ldr r1, = 0x810a0302

str r1, [r0, #MPLL_CON_OFFSET]

; APLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 1

ldr r1, = 0x810a0301

str r1, [r0, #APLL_CON_OFFSET]

; 使能MPLL锁相环,配置M,D,S分频数

; MPLL_EN = 1<<31, MDIV = 266<<16, PDIV = 3<<8, SDIV = 2

ldr r1, = 0x810a0302

str r1, [r0, #MPLL_CON_OFFSET]

6. 设置对应时钟源寄存器,为各种外设提供时钟频率

; UART_SEL = 0b1

; MPLL_SEL = 0b1, APLL_SEL = 0b1

ldr r1, [r0, #CLK_SRC_OFFSET]

ldr r2, =0x2005 ; 同时设置UART的时钟源来自MPLL

orr r1, r1, r2

str r1, [r0, #CLK_SRC_OFFSET]

; MPLL_SEL = 0b1, APLL_SEL = 0b1

ldr r1, [r0, #CLK_SRC_OFFSET]

ldr r2, =0x2005 ; 同时设置UART的时钟源来自MPLL

orr r1, r1, r2

str r1, [r0, #CLK_SRC_OFFSET]

上一篇:S3C2440 SDRAM内存驱动

下一篇:ARM9(2440)对nand flash的读写操作

推荐阅读最新更新时间:2024-03-16 14:51

s3c6410的UART设备驱动(2)

上一篇说到了第一部分,这一篇说第二部分,如下这部分: 在模块初始化是调用uart_register_driver和uart_add_port注册UART驱动并添加端口,在模块卸载时调用uart_unregister_driver和uart_remove_one_port以注销UART驱动并移除端口。 1、先说uart_register_driver函数,这个函数在 static int __init s3c24xx_serial_modinit(void) module_init(s3c24xx_serial_modinit);中被调用。 列出其源码,在Serial_core.c (linux2.6.28drive

[单片机]

S3C6410 移植Android 内核

主要过程: . 安装lunux 环境 . 安装编译工具 . 下载Linux kernel . 安装 Android SDK . 获得root file system . 修改Linux kernel 源码 . 配置Linux kernel . 修改root file system . 编译Linux kernel . 下载kernel Image 1.安装linux 环境 安装Ubuntu Linux 系统,从网站上下载操作系统安装光盘映像,地址: http://mirror.lupaworld.com/ubuntu/releases/8.04/ 下载ubuntu-8.04.2-desktop-i386.iso,刻录成光盘安装,

[单片机]

linux中LCD设备驱动(4)——基于s3c6410平台

我们这一篇来说与具体的TFT显示器有关的部分,当遇到具体的显示器是我们应该设置什么参数,怎样设置这些参数。 1、在s3cfb_WXCAT43.c (linux2.6.28driversvideosamsung)文件中是有关具体显示器的设置。我们一段一段来看。 #include linux/wait.h #include linux/fb.h #include linux/delay.h #include linux/platform_device.h #include plat/regs-gpio.h #include plat/regs-lcd.h #include s3cfb.h #define S3C

[单片机]

基于ARM的家用智能垃圾桶设计

随着人们生活水品的不断提高,在人们购买各种家具或家电时越来越重视其智能化和人性化。人们在生活中产生的生活垃圾都需用垃圾桶放置,考虑到老人、孕妇或者残疾人,放置垃圾时存在的不便、费时、费力等问题。设计针对这些问题,提出了具有语音识别功能的智能垃圾桶设计方案,当用户想要扔垃圾时,只要一声令下,垃圾桶就会快速准确地来到你身边。 1 系统硬件设计 系统硬件包括垃圾桶车体机械结构和硬件控制电路两个部分。其中车体机械结构为一部三轮小车车体,能按照在不同地点处用户发出的声音指令,自动行驶到用户所在地。系统硬件电路总体结构框图如图1所示,包括电源模块、ARM最小系统、声源定位模块、语音识别模块、避障模块和电机驱动模块。

[单片机]

STM32时钟初始化函数SystemInit()详解

花了一天的时间,总算是了解了SystemInit()函数实现了哪些功能,初学STM32,,现记录如下(有理解错误的地方还请大侠指出): 使用的是3.5的库,用的是STM32F107VC,开发环境RVMDK4.23 我已经定义了STM32F10X_CL,SYSCLK_FREQ_72MHz 函数调用顺序: startup_stm32f10x_cl.s(启动文件) → SystemInit() → SetSysClock () → SetSysClockTo72() 初始化时钟用到的RCC寄存器复位值: RCC_CR = 0x0000 xx83; RCC_CFGR = 0x0000 0000;RCC_CIR = 0x0000 0000;

[单片机]

S3C2440,S3C2450和S3C6410的区别

作为GPS、PDA、数字电视等手持设备的主要方案处理器提供方韩国Sumsung公司,最近又新推出ARM处理器S3C2450、S3C6410芯片。这些平台又与S3C2440处理器有哪些区别优势。 S3C2440: 主频400MHz; SDRam内存控制器; 支持Nor Flash和Nand Flash(SLC) 支持2种Flash启动; 内部LCD、I2C、Camera等控制器。 S3C2450: 主频533MHz; 双总线架构,一路用于内存总线、一路用于Flash总线; DDRII内存和DDR内存控制器; 支持Nor Flash和Nand Flash两种Flash,其中Nand Flash支持SLC和MLC两

[单片机]

飞思卡尔单片机 时钟初始化及配置

系统时钟可选择内部或外部时钟,时钟频率可倍频,总线时钟为系统时钟的1/2,定时器时钟可选择时钟源,时钟源可选择总线时钟或者是外部时钟等(我程序里选择的为总线时钟),并可以进行分频。 如我选择的为外部时钟,时钟频率为8M,进行4倍频,则系统时钟为32M,总线时钟为16M,定时器采用该总线时钟,分频系数为32,则定时器计数周期(即0x0001代表时间)为:1/(16/32)us=2us。

[单片机]

S3C6410使用---7uboot中SD初始化及读写分析

一、uboot中SD卡的初始化 二、读取扇区 三、 写变量到SD卡中 四、 一、uboot中SD卡的初始化 1.1 硬件连线 MMC0_CDN -- GPG6 -- SD卡检测引脚 MMC0_WPN -- GPGL13 -- SD卡写保护引脚 MMC0_DATA -- GPG -- MMC0_CMD -- GPG1 -- SD命令线 MMC0_CLK -- GPG0 -- SDIO/SD卡时钟线 1.2 uboot中初始化过程 uboot lib_arm/board.c中 void start_armboot (void) { #if de

[单片机]

小广播

热门活动

换一批

更多

设计资源 培训 开发板 精华推荐

最新单片机文章

更多精选电路图

更多热门文章

更多每日新闻

更多往期活动

11月14日历史上的今天

厂商技术中心

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号