1、什么是时钟脉冲信号,起什么作用?

时钟脉冲信号时有一定电压幅度和一定的时间间隔并连续发出的脉冲信号。时钟脉冲信号是时序逻辑的基础,它用于决定逻辑单元中的状态何时更新。数字芯片中的众多晶体管都工作在开关状态,它们的导通和关断动作都是按照时钟信号的节奏进行的。也就是说嵌入式系统是按照时钟来安排CPU的任务。

2、时钟脉冲信号的频率是指单位时间内产生的时钟脉冲个数。

3、如何产生时钟信号?

时钟信号一般有晶振或晶振与PLL产生。

晶振的制造就是用石英晶体经精密切割磨削并镀上电极焊上引线就做成了。这种晶体如果给它通上电,它就会产生机械振荡,其频率和他们的形状,材料,切割方向等密切相关。

由于石英晶体化学性能非常稳定,热膨胀系数非常小,其振荡频率也非常稳定,由于控制几何尺寸可以做到很精密,因此,其谐振频率也很准确。

4、晶振和锁相环(PLL)

晶体振荡器时钟的优点:结构简单,噪声低。缺点:由于其频率仅由晶体决定,通常是特定晶体被制成客户所需要的振荡器,导致生产成本高、交货周期较长,不利于客户加快产品上市时间,而且难以获得非标准的频率。

PLL(锁相环)合成器是一种更为复杂的系统时钟源。通用的PLL合成器需要一个外部晶体并包含一个能够对晶体的特定频率加倍或分频的集成锁相环(PLL)电路。

5、信号产生对比

5.1、对于特定的时钟频率,采用PLL合成器可以使用较便宜以及较低频率晶振来代替昂贵的高频晶振;

5.2、对于需要多个时钟频率的系统,采用PLL合成器通过分频即可实现,而此时采用晶振模块则需要多个不同频率的晶振。

因此相对于晶体振荡器模块,通过PLL合成器提供精确时钟具有成本更低、占板面积更小等一系列优点。

二、时钟体系

学习时钟体系学什么

1、晶振频率 2、PLL 3、PLL产生了哪些时钟 4、产生的时钟是提供给谁的

2440:

1、12MHZ晶振

2、MPLL、UPLL

3、MPLL(FCLK,HCLK,PCLK)

UPLL(UCLK)

4、

| 时钟 | 应用场合 | 应用举例 |

| FCLK | 处理器 | ARM9 |

| HCLK | AHB BUS | LCD DMA |

| PCLK | APB BUS | UART GPIO |

| UCLK | USB | USB主从口 |

APB是低带宽的周边外设之间的连接总线

DMA的概念:DMA(Direct memory access)是在专门的硬件( DMA)控制下,实现高速外设和主存储器之间自动成批交换数据尽量减少CPU干预的输入/输出操作方式。

6410:

1、12MHZ

2、APLL、MPLL、EPLL

3、APLL(ARMCLK) MPLL(HCLK PCLK) EPLL(SCLK)

4、

| 时钟 | 应用场合 | 应用举例 |

| ARMCLK | ARM | ARM11 |

| HCLK | AHB BUS | LCD DMA |

| PCLK | APB BUS | UART GPIO |

| SCLK | 特殊情况 | USB主从口 |

210:

1、24MHZ

2、4个PLL:APLL,MPLL,EPLL,VPLL

3、210与2440和6410都有所不同:

| 时钟体系 | 所属时钟 | 应用举例 | 锁相环 |

| MSYS | ARMCLK HCLK_MSYS PCLK_MSYS |

ARM核

内存控制器 中断

|

APLL |

| DSYS | HCLK_DSYS PCLK_DSYS | 显示相关部件,如FIMC | MPLL |

| PSYS |

HCLK_PSYS

CLK_DPM

|

外设,如Uart,i2C | EPLL |

| 视频相关 | VPLL |

三、思维导图的设计

软件设计指导:

1、时钟初始化流程

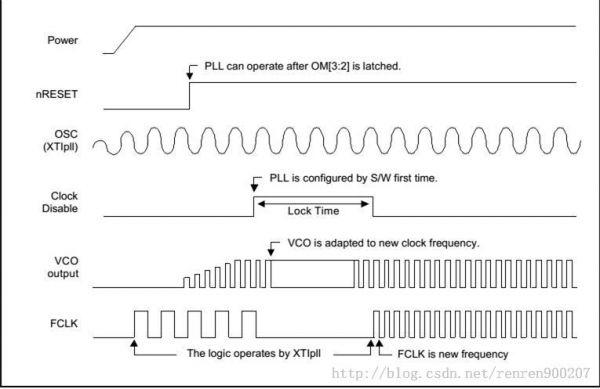

从上图的时序我们可以看到

1、上电几毫秒后,晶振输出稳定,FCLK=晶振频率,nRESET信号恢复高电平后,CPU开始执行指令。

2、我们的程序开头启动MPLL,设置MPLL的寄存器

3、在设置MPLL的寄存器后,需要等待一段时间(Lock Time),MPLL的输出才稳定。在这段时间(Lock Time)内,FCLK停振,CPU停止工作。Lock Time的长短由寄存器LOCKTIME设定。

4、Lock Time之后,MPLL输出正常,CPU工作在新的FCLK下。

时钟初始化流程(芯片手册):

1、设置Lock Time

2、设置分频系数

3、设置CpU到异常模式

4、设置FCLK

开始写代码

2440:

1、在芯片手册查找Locktime -register,一般我们都使用默认值,所以可以忽略不做

2、设置分频系数

参考Uboot中的分频系数为FCLK:HCLK:PCLK = 1:4:8

时钟初始化程序要位于led点亮程序之前,这样便于调试。

#define CLKDIVN 0x4c0000004

clock_init:

ldr r0, =CLKDIVN

mov r1, 0x5

str r1, [r0]

3、设置CPU到异步工作模式

mrc p15, 0, r0, c1, c0, 0

orr r0, r0, 0xc0000000

mcr p15, 0, r0, c1, c0, 0

4、设置FCLK

#define MPLLCON 0x4c000004

#define MPLL_405MHZ ((127<<12) | (2<<4) | (1<<0))

ldr r0, =MPLLCON

mov r1, =MPLL_405MHZ

str r1, [r0]

mov pc, lr

6410:

1、同样,Lock time不变,保持原来值。

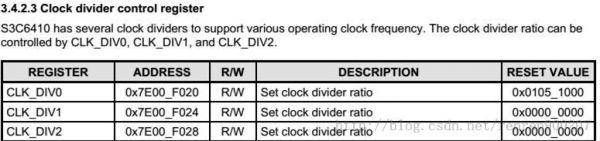

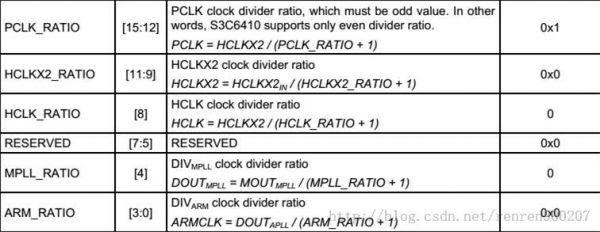

2、设置分频系数

ARMCLK = APLLout/(DIVARM+1) HCLKX2 = MPLLout/(DIVHCLKX2+1) HCLK = HCLKX2/(DIVHCLK+1) PCLK = HCLKX2/(DIVPCLK+1)

参考Uboot可以设置DIVpclk = 3 DIVhclk = 1 DIVhclkX2 = 1 DIVARM = 0

代码如下:

#define CLK_DIV0 0x7e00f020 #define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12)) init_clock: ldr r0, =CLK_DIV0 ldr r1, = DIV_VAL str r1, [r0]

3、设置CPU工作在异常模式下

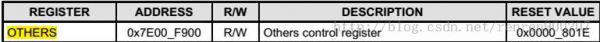

#define OTHERS 0x7e00f900

ldr r0, =OTHERS

ldr r1, [r0]

bic r1, r1, #0xc0

str r1, [r0]

4、设置FCLK为533MHZ

#define MPLL_CON, 0x7e00f010 #define APLL_CON, 0x7e00f00c #define PLL_Val ((1<<31)|(266<<16)|(3<<8)|(1<<0)) ldr r0, =APLL_CON ldr r1, =PLL_Val str r1, [r0] ldr r0, =MPLL_CON ldr r1, =PLL_Val str r1, [r0]

5、6410还有个特殊性就是设置一下选择器CLK_SRC设置PLL产生时钟为时钟源。

#define CLK_SRC 0x7e00f01c

ldr r0, =CLK_SRC

mov r1, #0x3

str r1, [r0]

然后运行后下载到开发板运行

全代码为:

.text .global _start _start: b reset ldr pc, _undefined_instruction ldr pc, _software_interrupt ldr pc, _prefetch_abort ldr pc, _data_abort ldr pc, _not_used ldr pc, _irq ldr pc, _fiq _undefined_instruction: .word undefined_instruction _software_interrupt: .word software_interrupt _prefetch_abort: .word prefetch_abort _data_abort: .word data_abort _not_used: .word not_used _irq: .word irq _fiq: .word fiq undefined_instruction: nop software_interrupt: nop prefetch_abort: nop data_abort: nop not_used: nop irq: nop fiq: nop reset: bl set_peri_port bl set_svc bl disable_watchdog bl disable_interrupt bl disable_mmu bl init_clock bl light_led set_peri_port: ldr r0, =0x70000000 orr r0, r0, #0x13 mcr p15,0,r0,c15,c2,4 mov pc, lr set_svc: mrs r0, cpsr bic r0, r0, #0x1f orr r0, r0, #0xd3 msr cpsr, r0 mov pc, lr #define pWTCON 0x7E004000 disable_watchdog: ldr r0, =pWTCON /*mov的操作数最多为8位*/ mov r1, #0x0 str r1, [r0] mov pc, lr disable_interrupt: mvn r1, #0x0 ldr r0, =0x71200014 str r1, [r0] ldr r0, =0x71300014 str r1, [r0] mov pc, lr disable_mmu: mcr p15, 0, r0, c7, c7, 0 mrc p15, 0, r0, c1, c0, 0 bic r0, r0, #0x00000007 mcr p15, 0, r0, c1, c0, 0 mov pc, lr #define CLK_DIV0 0x7e00f020 #define DIV_VAL ((0x0<<0)|(0x1<<9)|(0x1<<8)|(0x3<<12)) #define OTHERS 0x7e00f900 #define MPLL_CON 0x7e00f010 #define APLL_CON 0x7e00f00c #define PLL_Val ((1<<31)|(266<<16)|(3<<8)|(1<<0)) #define CLK_SRC 0x7e00f01c init_clock: ldr r0, =CLK_DIV0 ldr r1, =DIV_VAL str r1, [r0] ldr r0, =OTHERS ldr r1, [r0] bic r1, r1, #0xc0 str r1, [r0] ldr r0, =APLL_CON ldr r1, =PLL_Val str r1, [r0] ldr r0, =MPLL_CON ldr r1, =PLL_Val str r1, [r0] ldr r0, =CLK_SRC mov r1, #0x3 str r1, [r0] mov pc, lr #define GPKCON0 0x7f008800 #define GPKDAT 0x7f008808 light_led: ldr r0, =GPKCON0 ldr r1, =0x11110000 str r1, [r0] ldr r0, =GPKDAT ldr r1, =0xa0 str r1, [r0] mov pc, lr

上一篇:ARM裸机开发中内存管理库RT_HEAP的使用

下一篇:ARM裸机开发bootloader交叉工具链

推荐阅读最新更新时间:2024-03-16 14:56

ARM Cortex-M0权威指南(中文)

ARM Cortex-M0权威指南(中文)

京公网安备 11010802033920号

京公网安备 11010802033920号