ARM和Thumb状态

RISC技术

流水线技术

超标量技术

ARM和Thumb状态

V4版以后有:

(1)32位ARM指令集

(2)16位Thumb指令集,功能是ARM指令集的功能子集。

ARM7TDMI核以后,T变种的ARM微处理器有两种工作状态:

(1)ARM状态

(2)Thumb状态。

当ARM微处理器执行32位的ARM指令集时,工作在ARM状态;

当ARM微处理器执行16位的Thumb指令集时,工作在Thumb状态

Thumb技术介绍

ARM7体系结构被广泛应用的时候,嵌入式控制器的市场仍然由8位、16位处理器占领。这些产品不能满足高端应用。这些应用需要32位RISC处理器的性能和更优于16位CISC处理器的代码密度。

为了解决代码密度的问题,ARM增加了T变种。

Thumb从32位ARM指令集中抽出来的36条指令格式,可重新编成16位的操作码。

在运行时,16位的Thumb指令又由处理器解压成32位指令。

Thumb核有2套独立的指令集,它使设计者得到ARM32位指令性能的同时,又能享有Thumb指令集产生的代码方面的优势,在性能和代码大小之间取得平衡。

和ARM指令集相比,Thumb指令集具有以下的局限:

完成相同的操作,Thumb指令通常需要更多的指令,因此在对系统运行时间要求苛刻的场合,ARM指令集更为合适。

Thumb指令集没有包含进行异常处理时需要的一些指令,因此在异常中断时,还是需要使用ARM指令,这种限制决定了Thumb指令需要与ARM指令配合使用。

ARM与Thumb状态转换

在程序的执行过程中,微处理器可以随时在两种工作状态之间切换,并且该转变不影响处理器的工作模式和相应寄存器中的内容。

进入Thumb状态:当操作数寄存器的状态位(位[0])为1时,执行BX指令。

进入ARM状态:当操作数寄存器的状态位(位[0])为0时,执行BX指令。

RISC技术

嵌入式微处理器可以分为两类:CISC和RISC;

CISC(Complex Instruction Set Computer):复杂指令系统计算机;随着计算机技术的发展而不断引入新的复杂的指令集,计算机的体系结构会越来越复杂。

大约有20%的指令会被反复使用,占整个程序代码的80%,而余下的80%的指令却不经常使用,在程序设计中只占20% 。

RISC(Reduced Instruction Set Computer):精简指令系统计算机;- 采用固定长度的指令格式

- 使用单周期指令

- 大量使用寄存器

- 可用加载/存储指令批量传输数据

- 在循环处理中使用地址的自动增减

RISC技术与CISC技术比较

RISC技术

ARM处理器采用加载/存储(Load/Store)体系结构是典型的RISC处理器,即只有Load/Store的存/取指令可以访问存储器,其余指令都不允许进行存储器操作。

RISC体系结构基本特点:

(1)大多数指令只需要执行简单和基本的功能,其执行过程在一个机器周期内完成。

(2)只保留加载/存储指令。操作数由加载/存储指令从存储器取出放寄存器内操作。

(3)芯片逻辑不采用或少采用微码技术,而采用硬布线逻辑。

(4)减少指令数和寻址方式。

(5)指令格式固定,指令译码简化。

(6)优化编译。

RISC技术

ARM体系结构还采用了一些特别的技术:

所有的指令都可根据前面的执行结果决定是否被执行,提高了指令的执行效率。

可用Load/Store指令批量传输数据,以提高数据的传输效率。

可在一条数据处理指令中同时完成逻辑处理和移位处理。

RISC和CISC各有优势,界限并不那么明显。

现代的CPU往往采用CISC的外围,内部加入了RISC的特性,如超常指令集CPU就是融合了RISC和CISC的优势,成为未来的CPU发展方向之一。

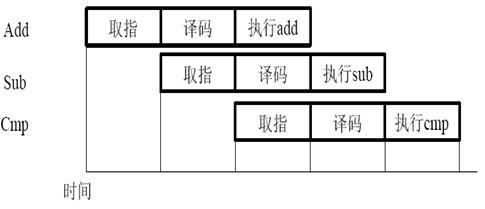

流水线技术

是一种将每条指令分解为多步,并让各步操作重叠,从而实现几条指令并行处理的技术;

程序中的指令仍是一条条顺序执行,但可以预先取若干条指令,并在当前指令尚未执行完时,提前启动后续指令的另一些操作步骤,从而可加快程序的运行速度;

开发和设计嵌入式系统的过程中,CPU的性能是一个非常重要的考虑因素。

流水线技术是在本质上影响程序执行速度的因素。

由于计算机中一条指令的各个执行阶段相对独立,因此,现代CPU大多设计成流水线型的机器,在这种类型机器中几个指令可以并行执行。采用流水线的重叠技术大大提高了CPU的运行效率。

当流水线内部的信息通畅流动时,CPU流水线能够工作得最好。

但实际应用中,指令各执行阶段的操作时间长短不同,有一些指令序列可能会打断流水线内的信息流,所以有时流水线操作不十分通畅,会暂时降低CPU的执行速度。

单周期指令的执行过程

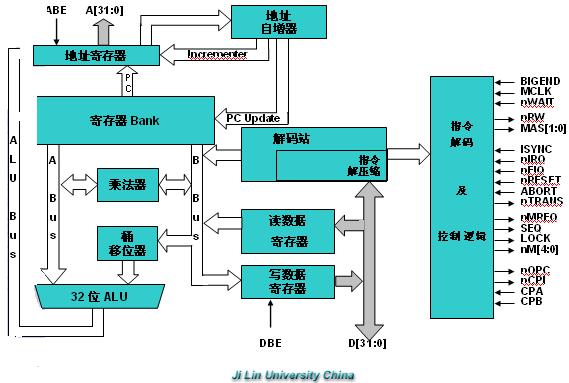

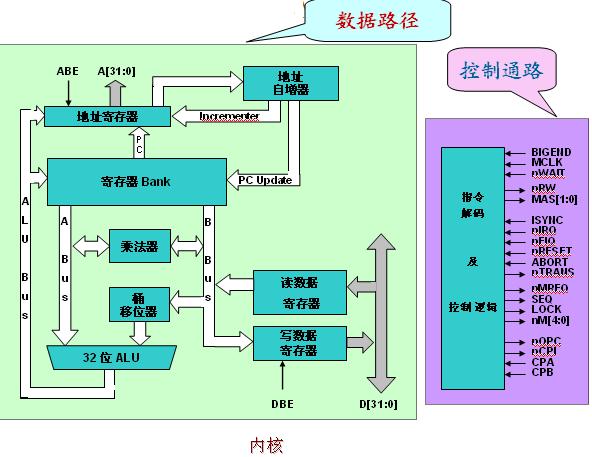

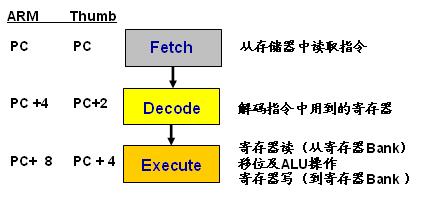

ARM的3级流水线

ARM7架构采用了一个3段的流水线:

(1)取指:将指令从内存中取出来。

(2)译码:操作码和操作数被译码以决定执行什么功能。为下一周期准备数据路径需要的控制信号。这一级指令”占有“译码逻辑,而不是”占有”数据路径

(3)执行:执行已译码的指令。指令占有数据路径,寄存器堆栈被读取,操作数在桶行移位器中被移位。ALU产生运算结果并回写到目的寄存器中,ALU结果根据指令需求更改状态寄存器的条件位。

流水线模式下PC的更改过程

多周期ARM指令的3级流水线操作

数据路径涉及到所有执行周期、地址计算和数据传送。译码逻辑总是产生数据路径在下一个周期使用的控制信号,因此除译码周期以外,在STR地址计算周期也产生数据传送所需的控制信号。

取指的存储器访问和执行的数据路径占用都是不可同时共享的资源,对于多周期指令来说,如果指令复杂以至于不能在单个时钟周期内完成执行阶段,就会产生流水线阻塞。

ARM的流水线设计问题

1)缩短程序执行时间:

Tprog:执行一个程序所需时间;

Ninst:执行该程序的指令条数;

CPI:执行每条指令的平均时钟周期数;

Fclk:处理器的时钟频率。

措施:

提高时钟频率fclk(导致流水线的级数增加 )。

减少每条指令的平均时钟周期数CPI(需要解决流水线的相关问题 )

2)解决流水线相关:

结构相关:某些指令在流水线中重叠执行时,产生资源冲突 。

措施:1)采用分离式指令Cache和数据Cache。2)ALU中采用单独加法器来完成地址计算。

数据相关:当一条指令需要前面指令的执行结果,而这些指令均在流水线中重叠执行时,就可能引起流水线的数据相关。

数据相关有“写后读”、“写后写”和“读后写”等。

措施:1)旁路技术。2)流水线互锁技术。

控制相关:当流水线遇到分支指令和其他会改变PC值的指令时,就会发生控制相关。

措施:1)引入延时分支。2)尽早计算出分支转移成功时的PC值(即分支的目标地址)。

ARM的5级流水线

ARM9和StrongARM架构都采用了5级流水线.

增加了I-Cache和D-Cache,把存储器的取指与数据存取分开;

增加了数据写回的专门通路和寄存器;

把指令的执行过程分割为5部分:

取指:将指令从指令存储器中取出,放入指令流水线中。

指令译码:对指令进行译码,从寄存器堆中读取寄存器操作数。

执行:把一个操作数移位,产生ALU结果。如果指令是Load或Store,在ALU中计算存储器的地址。

数据缓存:如果需要,访问数据存储器;否则,ALU的结果只是简单地缓冲一个时钟周期,以便使所有指令具有同样地流水线流程。

写回 :将指令产生地结果写回到寄存器堆。

流水线对比

超标量执行

通过重复设置多套指令执行部件,同时处理并完成多条指令,实现并行操作,来达到提高处理速度的目的。

所有ARM内核,包括流行的ARM7、ARM9和ARM11等,都是单周期指令机。

ARM公司下一代处理器将是每周期能处理多重指令的超标量机。

超标量处理机:一个时钟周期内同时执行多条指令的处理机。

超标量处理器中的多指令单元

超标量与流水线技术是兼容的,为了能够在一个时钟周期内同时发射多条指令,超标量处理机必须有两条或两条以上能够同时工作的指令流水线。但与此同时,也带来了多流水线的调度问题和操作部件的资源冲突问题。

超标量处理器在执行的过程中必须动态地检查指令相关性。

如果代码中有分支指令,必须将分支被执行和分支不被执行这两种情况分开考虑。

计算执行时间几乎是不可能的。

上一篇:ARM平台的地址对齐问题

下一篇:基于Android的ARM汇编语言系列之四:ARM处理器的寻址方式

推荐阅读最新更新时间:2024-03-16 14:59

设计资源 培训 开发板 精华推荐

- 【已结束】直播|Microchip MPU解决方案及典型应用

- 【说出你的故事】跨平台转换——你做?还是不做?

- 拆惊喜抽奖:泰克全新3系列MDO和4系列MSO示波器来啦

- 意法半导体工业峰会2023 直播结束

- TI 最新电容式触控套件,免费尝鲜中

- ADI 全新中文资料(2019 年 11 月)

- ADI和\"西北模电王\"邀您一起下载研读《新概念模拟电路》系列第一本电子书《晶体管》

- 有奖直播:安森美电感式位置传感器接口 NCS32100

- 【MPS有奖分享】便携式多功能电工台的核“芯”功能测试与结构设计

- 有奖直播:安世半导体先进 SiC MOSFET 助力提升 EV-Charger 和 OBC 应用能效

ARM Cortex-M0权威指南(中文)

ARM Cortex-M0权威指南(中文) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号