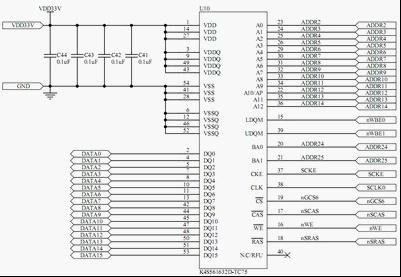

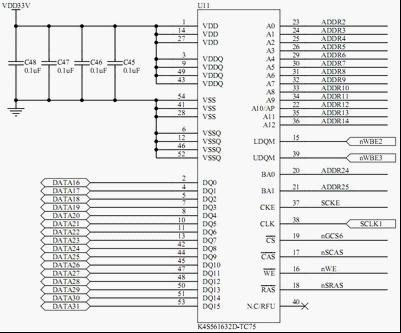

由于S3C2410是32位处理器(指令一次能够操作32位数据(运算器一次可以处理32位数据);通用寄存器多是32位寄存器;处理器内部数据通道也是32位的;处理器外部数据总线宽度通常是32位的,地址总线宽度只是代表CPU寻址范围大小,与CPU是多少位的无关,也即32位CPU的地址总线不一定是32根的,例如对于s3c2410,每一个Bank对应27根地址线,寻址能力为128MB,全部8个Bank总的寻址能力为1GB),所以为了最大限度的发挥其性能,内存最好也是32位(指数据宽度)的,(当然,在s3c2410的8个bank中,除了Bank0只能选择16/32数据位宽外,其余的7个Bank均可以单独选择8/16/32位宽的存储系统)然而市面上很少有32位宽度的单片SDRAM,所以一般都采取两片16位的SDRAM进行位扩展得到32位的SDRAM。

由上两图可见,本系统扩展后的内存系统为16M×32Bit的(此处32Bit是指数据位宽度,而非地址位,可以理解SDRAM数据位宽度与地址线的条数无关,明白数据线和地址线的区别,对于下面地址线的连接方式的理解非常重要)。

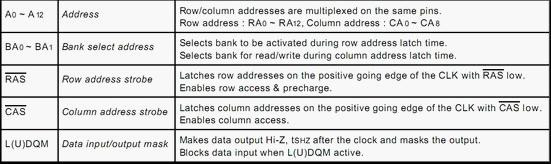

一、A0~A12地址线

首先要明白这一点,在CPU的寻址空间中,字节(8位)是表示存储容量的唯一单位。(所以为什么对于51单片机来说,其16根地址线的寻址能力为64KB,注意:其单位是Byte—字节)

而对于上述已经进行扩展了的32位SDRAM存储系统,可以认为它的每一个存储单元都是4个字节的(单位是4个字节=1个字),因此当它的地址线A1:A0=01时,处理器上对应的地址线应为A3:A2=01(因为CPU的寻址空间是以Byte为单位的)。

正因为如此,SDRAM的A0引脚接到了S3C2410的A2地址线上。

以此类推,SDRAM的A12~A1引脚依次接到了2410的A14~A3地址线上。

可以认为将CPU地址线左移两位,即乘以4(32/8)。

同样的,对于16位数据位宽的SDRAM系统而言,需要将SDRAM的A0引脚连接到2410的A1地址线上面。

二、BA0~BA1地址线

K4S561632D是4M×16Bit×4Banks,共32MB

DRAM芯片在构造上的特点是,芯片上的地址引脚是复用的。(在存取DRAM芯片的某单元时,其操作过程是将存取的地址分两次输入到芯片中,每一次都由同一组地址线输入。两次送到芯片上去的地址分别称为行地址和列地址,它们被锁存到芯片内部的行地址锁存器和列地址锁存器中。可以想象,在芯片内部,各存储单元是按照矩阵结构排列的。行地址信号通过片内译码选择一行,列地址信号通过片内译码选择一列,这样就决定了选中的单元)。 /RAS是行地址锁存信号,该信号将行地址锁存在芯片内部的行地址锁存器中;/CAS是列地址锁存信号,该信号将列地址锁存在芯片内部的列地址锁存器中。

K4S561632D共有13根地址线(A0~A12)。行地址线为A0~A12,共13根;列地址线为A0~A8,共9根,可见K4S561632D一个Bank的存储容量为213×29=222=4M。(对于DRAM来说,13根地址线的最大编址空间为226=64M,可见此处K4S561632D还是留有余量的,其最大容量可以扩充到64M)

BA0~BA1是Bank选择地址线。Banks可以理解为一片16M×16Bit 的K4S561632D内部是由4片容量为4M的16Bit SDRAM扩展而成的,即16M×16Bit =4M×4Banks×16Bit。 BA0~BA1即为该4片SDRAM的片选信号。可见BA0~BA1代表了K4S561632D的最高位。

K4S561632D芯片管脚说明

综上,BA0~BA1代表了SDRAM的最高地址位。因为CPU的寻址空间是以字节(Byte)为单位的,本系统SDRAM容量为16MWord=64MByte,那就需要A25~A0(64M=226)地址线来寻址,所以BA1~BA0地址线应该接到2410的A25~A24引脚上。

当然,由上面分析可知,DRAM内存的地址线是行地址线与列地址线复用的,所以地址线的数目并不需要26条。

三、DQM信号

如前所述,32位的SDRAM存储单元以4Byte为单位进行数据访问的时候,内存会忽略CPU的A1和A0地址线(事实上,2410的A1和A0地址线也根本没接到SDRAM的芯片上)。

但是处理器如果需要访问地址偏移量为01的单个字节,就需要DQM(Data Mask)信号进行帮助,这个信号接在2410的nWEB线上。DQM信号由处理器根据当前的访问情况发出,如果当前的访问只需要低16字节,那么nWEB0和nWEB1线就会有效。

上一篇:Linux-2.6.12移植到斯道s3c2410

下一篇:S3C2410-SDRAM

推荐阅读最新更新时间:2024-03-16 15:22

ESP32-C6 系列芯片手册

ESP32-C6 系列芯片手册 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号