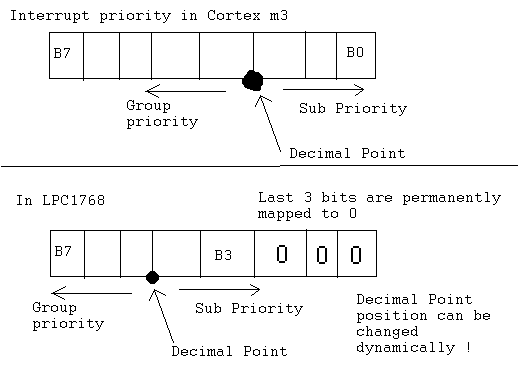

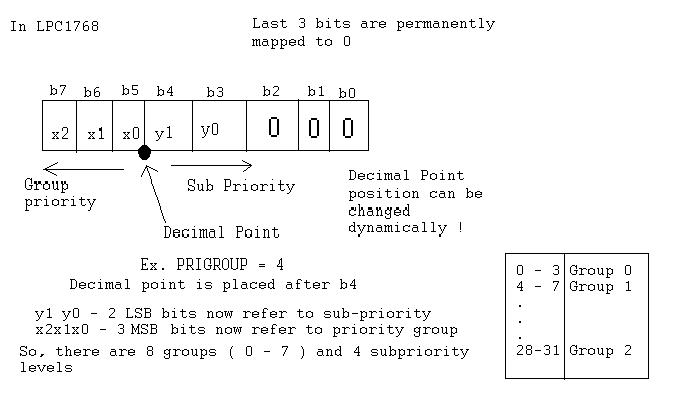

一、背景 USB在持续通信几十万次后,会出现USB IN中断丢失几次的情况,分析是中断优先级不够高,导 致USB中断在排队,然而排队还未完成,又有新的USB中断发生,致使其中断丢失。LPC1769的所有中 断默认为最高优先级"0"(数字越低,优先级越高),因此能想到的第一个解决办法既是降低除USB外所 有中断的优先级。 本篇即对LPC1769的中断优先级及优先级分组做个概述。 附:LPC1768/LPC1769除支持最高主频不同外,其他暂时没发现有什么差别。 二、正文 首先,说说中断优先级,所有中断均有一个优先级, 1、 更低的优先级数字代表着更高优先级 2、 除了RESET, Hard fault, NMI等系统级中断,其他所有中断优先级均可配置为"0~31"。 如果软件没有配置这些中断的优先级,那么所有中断的优先级默认为最高优先级"0"。此处 实例说明这个中断优先级的概念,假设三个外部中断"A,B,C","A,B"配置为"0","C"配置为"1", 1、 如果三个中断同时产生,那么"A,B"中断优先"C"中断运行。 2、 "A,B"中断同时产生,谁更优先执行呢?那就根据中断向量表的排号,低的优先执行。 3、 若是"C"的中断正在运行,此时"A"的中断发生,那么"A"的中断会抢占"C"的执行权限,优先 执行。 4、 若是"A"的中断正在运行,此时"B"的中断发生,那么新产生的"B"中断会进入等待状态,等 待"A"执行完毕再执行。 以上,只是单纯的判断优先级值来控制中断的顺序,为了增强中断的控制逻辑,ARM新增了优先级 组的概念。即相同的优先级等级可以分配在一组优先级内,在这一组优先级内再来定义次优先级,具 体是怎么一个概念呢?还是假设有四个中断"A,B,C,D","A,B,C"配置在优先级组"0"内,"A,B"中断配 置次优先级"0","C"配置为次优先级"1","D"则配置为优先级组"1" 1、 若"A,D"中断同时产生,则优先级高的"A"会优于"D"中断执行。 2、 若"A,C"中断同时产生,则优先级次优先级高的"A"会优先执行。 3、 若"A,B"中断同时产生,则根据中断向量表的位置,排号低的优先执行。 4、 若"D"正在执行中断,此时"A"中断来了,那么"A"中断会抢占"D"中断优先执行。因为"A"所 在的优先级组高于"D"。 5、 若"C"正在执行中断,此时"A"中断来了,那么"A"中断会等待"C"执行完毕再执行。因为属于 同一优先级组。 ARM用了一个8位寄存器来定义优先级组和次优先级的概念。中间可以选择一个端点,高位表示有 多少个主优先级,低位表示有多少个次优先级。 而LPC1769只用了其中5位。具体如下图:

**********************************************************************************

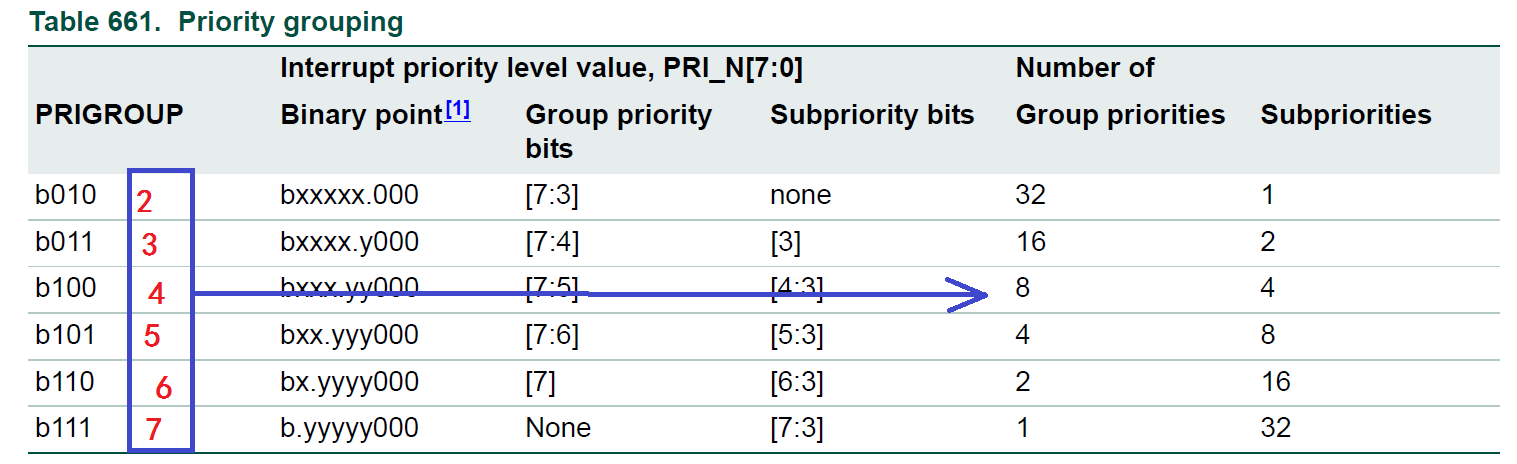

以上图的1768选定的端点为例,上图表示有"2^3=8"个优先级组,因为高三位用来定义优先级 组,同理,低二位用来定义次优先级有"2^2=4"个。 接着用实例来解释: 在LPC1769提供的"core_cm3.h"提供了定义优先级组和次优先级的函数。 定义优先级组函数: __STATIC_INLINE void NVIC_SetPriorityGrouping(uint32_t PriorityGroup) // PriorityGroup参数按上文所写,由于LPC1769只用了5位,所以传入的参数范围为"2~7" // 对应的优先级组与次优先级如下图

// 我选择的优先级组为8个,次优先级为4个。代码如下:

NVIC_SetPriorityGrouping(0x04);

接着,定义次优先级函数:

__STATIC_INLINE void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority) // 参数IRQn代表中断向量值,该值定义在文件"LPC17xx.h"内

/** @brief IRQ interrupt source definition */

typedef enum IRQn

{ /****** Cortex-M3 Processor Exceptions Numbers ********************/

...

Reset_IRQn = -15,

...

/****** LPC17xx Specific Interrupt Numbers *************************/

...

USB_IRQn = 24,

...

} IRQn_Type; // 参数priority // 代表中断优先级值,范围还是为"0~31",因此需要我们自己算好优先级组所处的位置 // 以我定义的8个优先级组来说,那么值"0~3"为优先级组"0",..."28~31"为优先级组"7"。

NVIC_SetPriority(USB_IRQn,0); //处于优先级组"0"

NVIC_SetPriority(TIMER0_IRQn,4); // 处于优先级组"1"

至此,记录完毕。

上一篇:Stm32 debug停留在"BKPT 0xAB"或者"SWI 0xAB"的解决办法

下一篇:LPC1769 CAN的自测试模式

推荐阅读最新更新时间:2024-03-16 15:27

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 Electric Motor Control: DC, AC, and BLDC Motors

Electric Motor Control: DC, AC, and BLDC Motors

京公网安备 11010802033920号

京公网安备 11010802033920号