ARM® Cortex®-M23采用TrustZone®技术,是尺寸最小、能效最高的处理器。小型嵌入式应用对芯片的安全性能有严格要求,基于ARMv8-M基线架构的Cortex-M23处理器则是最佳解决方案。

本文中,我将带各位领略全新Cortex-M23处理器的强大特色:

Cortex-M23最重要的特色是加入了TrustZone安全基础技术

极紧凑的架构与布线

强化的调试纠错和追溯能力(对开发商的生产力提高至关重要)

存储保护单元获得改善(该单元定义软件组件的访问许可,全新设计提升编程的效率,重新定义存储区域)

新增多条增强性能的指令

1. 为ARMv8-M量身打造的TrustZone技术:安全实现的基础

TrustZone技术为ARMv8-M度身优化,可以在每一台搭载Cortex-M23处理器的设备上以硬件形式实现可信软件和非可信软件强制隔离。因此,采用TrustZone,设计师只需一个处理器就可以设计嵌入式应用,此前则必须使用多个处理器才能在可信区域和非可信区域之间实现物理隔离。仅需Cortex-M23处理器,既可出色实现多项安全需求,如设备识别管理、高价值固件保护、软件认证、安全根等等。

采用TrustZone技术的Cortex-M23处理器具备以下两种安全状态:

安全状态 – 可以访问安全和非安全资源(存储、周边设备等)

非安全状态 – 只可访问非安全资源

两种安全状态下的代码执行转换和代码访问均由硬件监管,最大限度地降低转换管理成本并保证确定性——这也是所有Cortex-M处理器的标志性功能。

2. 紧凑二阶布线处理器

Cortex-M23是一款简单的二阶布线冯诺依曼处理器(Von Neumann processor),但却足以支持全套ARMv8-M基线指令集。熟悉Cortex-M0+的用户一定可以迅速指出Cortex-M23使能效最大化的众多相似特色:WFI(等待中断)/WFE(等待事件)和睡眠/深度睡眠模式、退出时睡眠、SysTick定时器和选配的单循环IO等。

指令集共包含80条左右的拇指指令,其中大多数都是16位指令(为了尽可能提高代码的紧凑度),但仍有一些为了提升效率而设置的32位指令。Cortex-M23支持所有的ARMv6-M指令,以帮助设计师轻而易举地将代码从Cortex-M0和Cortex-M0+处理器转移至Cortex-M23。此外ARMv8-M基线指令集中还加入了多条新指令以提升条件运算、互斥访问、硬件划分运算和即时移动的效率。

3. 强化的调试纠错与追溯能力

仅凭一台高效安全的32位处理器,尚无法成功实现字段部署,软件开发的成本通常超过生产和硬件IP的总和。Cortex-M23引入更多可配置的硬件断点和数据观测点,对比其他ARMv6-M处理器,可以助设计师更轻松地实现软件开发与调试。除了Cortex-M0+ 处理器中也配置的微型跟踪缓冲器(MTB),Cortex-M23还包括选配的嵌入式跟踪宏单元(ETM)。有了这些选配功能,设计师可以自行判断,究竟选择更加丰富全面的指令追溯能力;还是性价比更高、更加精简的指令追溯能力。

4. 用于任务隔离的存储保护单元

Cortex-M23还包括选配存储保护单元(MPU),基于全新PMSAv8架构打造,设计师使用起来非常方便。它可以在安全和非安全状态的任何一个状态下最多“保护”16个区域。每个区域都有一个基础地址、结束地址、访问许可和存储属性设置。在多任务环境下,操作系统可以在任务情境切换的过程中重新编程MPU,定义每个任务的存储许可,比如允许应用任务访问全部或部分应用数据和特定的周边设备。通过保护许可之外的数据免遭污染,并阻止未授权来源访问许可之外的周边设备,该MPU可以显著提升系统可靠性。

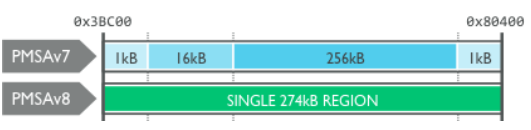

更易设置的存储区域

Cortex-M23的存储保护架构采用基线和限值比较器,用以定义存储区域,而此前使用的是二次方尺寸对齐比较器。这项改进简化了软件研发的复杂程度,而且在某些情况下,当区域尺寸不是完美的二次方尺寸时,还能减少存储浪费。

5. 全新ARMv8-M基线指令

对比ARMv6-M,Cortex-M23加入了许多全新指令,但丝毫没有折损Cortex-M系列处理器的超高能效。大多数新指令(除用于安全拓展外)都继承自ARMv7-M的架构指令集,进一步拓展Cortex-M23的功能,并与Cortex-M0+ 处理器形成鲜明区分。

5.1安全拓展

ARMv8-M采用的TrustZone安全技术为基线指令集补充了全新指令,包括安全网关(SG)、非安全支路(BXNS、BLXNS)以及测试目标(TT)指令。欲知详情,请参阅Yiu撰写的《ARMv8-M 架构介绍》。

5.2 仅执行代码生成

对仅执行(Execute-Only)代码存储区的支持也获得改善,新增加的即时移动指令(从ARMv7-M继承的MOV/MOVT)可以在仅执行代码中生成即时数据,让设计师仅凭2条指令便能生成32位值,且无需运行实际负载。

5.3代码优化

条件比较和支路指令(从ARMv7-M继承的CBNZ/CBZ)可以提高多项条件控制代码序列的性能。长偏移即时支路(从ARMv7-M继承的)可以将支路指向遥远的目标地址;硬件整数划分指令(从ARMv7-M继承的SDIV/UDIV)则可以减少除法运算的处理循环。

5.4排斥存取

Cortex-M23还从ARMv7-M继承了负载和储存的专用指令,提升Cortex-M23在多核系统中的一贯性,确保多个处理器以同样的机制处理信号。此外,为了对C11/C++11提供稳定支持,Cortex-M23还新增ARMv8-A(Thumb 32版本)的负载获取与储存释放指令,并包括这些指令的排斥存取变种。

上一篇:ARM发布M33处理器白皮书 具五大优势

下一篇:MCU产业“钱”景向好 进入市场可用哪些招式?

推荐阅读最新更新时间:2024-03-16 15:30

ESP32-C6 系列芯片手册

ESP32-C6 系列芯片手册

京公网安备 11010802033920号

京公网安备 11010802033920号