在开始之前先解释几个名词:

HSI: High Speed Internal clock, 高速内部时钟, STM32F429xx默认为16MHz.

HSE: High Speed External clock, 高速外部时钟, 最大可接受50MHz时钟(可外接最大的晶振为26MHz).

LSI: Low Speed Internal clock, 低速内部时钟, 32KHz.

LSE: Low Speed External clock, 低速外部时钟, 一般为32.768KHz.

PLL: Phase-Locked loops, 锁相环, 用于倍频时钟.

VCO: Voltage-Controlled Oscillator, 压控振荡器, PLL的组成部分.

AHB: Advanced High Performance Bus, 高性能总线, 用于高性能模块之间的连接, 如CPU, DMA.

APB: Advanced Peripheral Bus, 外设总线, 用于连接低速设备, 如UART, Timer.

STM32有两条APB总线, APB1和APB2, APB2的工作频率大于APB1.

APB2最高工作频率为84MHz, APB1最高工作频率为42MHz, AHB最高工作频率同系统时钟, 168MHz.

SYSCLK: 系统时钟.可被HSI, HSE, Main PLL直接驱动, 最大168MHz.

HCLK: CPU, AHB, DMA, 存储器的时钟, 经AHB预分频器得到.

PCLK1: APB1时钟.

PCLK2: APB2时钟.

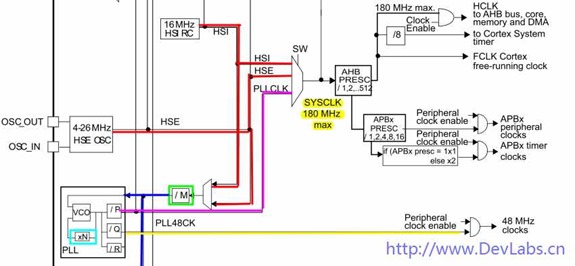

下图是STM32时钟树的一部分, 这里注要研究一下STM32F4系统时钟和PLL配置相关的东西.

从图中可以看出, HSI和HSE可以直接向SYSCLK提供时钟(红线), 它们经过一个预分频器 /M(绿色方框) 后向PLL提供时钟, 同时这个时钟(蓝线)也提供给PLLI2S和PLLSAI(图中未标出).

从VCO倍频出来后的时钟一路经过预分频器 /P 就是PLLCLK(紫色), 可以提供给系统时钟SYSCLK.

一路经过预分频器 /Q 后就是PLL48CK(黄色线), 这个时钟提供给USB OTG FS, SDIO, 一般这个时钟需要固定48MHz.

水绿色方框里的 xN 是VCO倍频的倍数, VCO输出的频率为HSE/HSI的频率经过 /M 分频后的数值乘以N.

接下来看一下ST固件库中提供的PLL配置函数:

1 2 3 4 5 | void RCC_PLLConfig(uint32_t RCC_PLLSource, uint32_t PLLM, uint32_t PLLN, uint32_t PLLP, uint32_t PLLQ); |

RCC_PLLSource为PLL的时钟源选择, 可选择为RCC_PLLSource_HSE或者RCC_PLLSource_HSI.

这里的PLLM, PLLN, PLLP, PLLQ便指的是上述的几个分频器的分频因子.

并且这些分频因子取值是有限制如下:

2 <= PLLQ <= 15

2 <= PLLM <= 63

192 <= PLLN <= 432

PLLP 只能是2, 4, 6, 8其中之一.

其中PLLN就是PLL的倍频倍数N.

并且, PLL之后得到的频率不得超过器件的限制频率.

举个实际的例子, 外部晶振为8MHz, 我们想让CPU运行于168MHz, 该怎么配置?

因为PLLM最小只能是2, 所以选择PLLM为2.

这里8MHz的HSE被PLLM二分频后只有4MHz了.

PLLP最小也只能是2, 我们所需要的SYSCK为168MHz, 所以从VCO出来的频率为168 * 2 = 336MHz.

则倍频倍数N为336 / 4 = 84, 所以PLLN为84.

PLLQ是USB OGT FS的时钟, 固定为48MHz, 所以预分频因子为336 / 48 = 7.

则PLL配置函数应该为:

1 | RCC_PLLConfig(RCC_PLLSource_HSE, 2, 84, 2, 7); |

当然只使用这一句就不可能让PLL工作的, 还需要配合其它配置才行.

(全文完)

上一篇:浅谈STM32的端口输出方式

下一篇:stm32笔记:Systick系统滴答定时器

推荐阅读最新更新时间:2024-03-16 15:33

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号