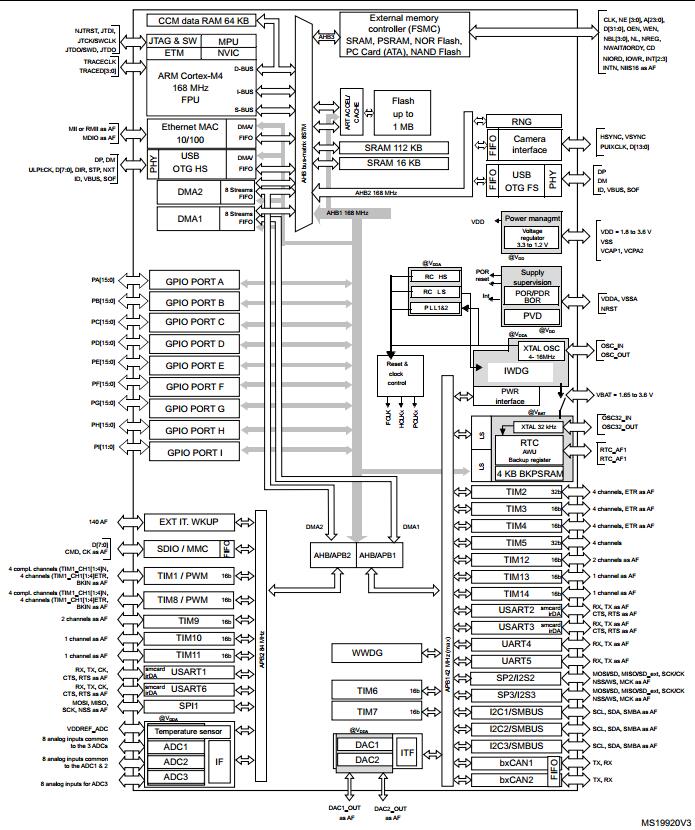

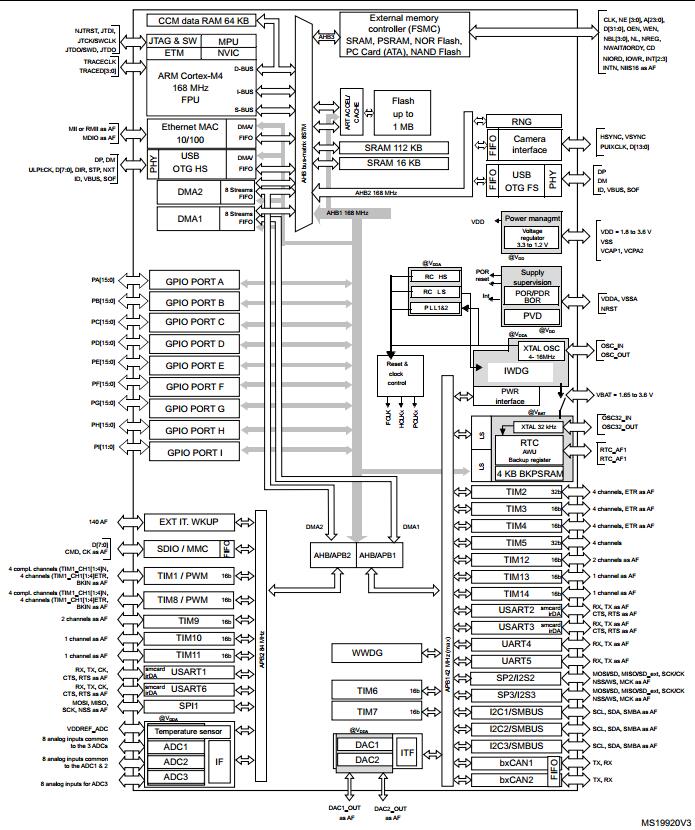

时钟系统是CPU的脉搏,就像人的心跳一样。STM32F4 的时钟系统比较复杂,不像简单的51 单片机一个系统时钟就可以解决一切。STM32F4 的框图如下(可以看到相应的时钟):

1. 连至 APB2 的定时器从 TIMxCLK 提供时钟 (最高 168 MHz) ,连至 APB1 的定时器从 TIMxCLK 提供时钟 (取决于

RCC_DCKCFGR 寄存器中 TIMPRE 位的配置,最高 84 MHz 或 168 MHz)。

2. 摄像头接口和网络接口仅适用于 STM32F407xx 设备。

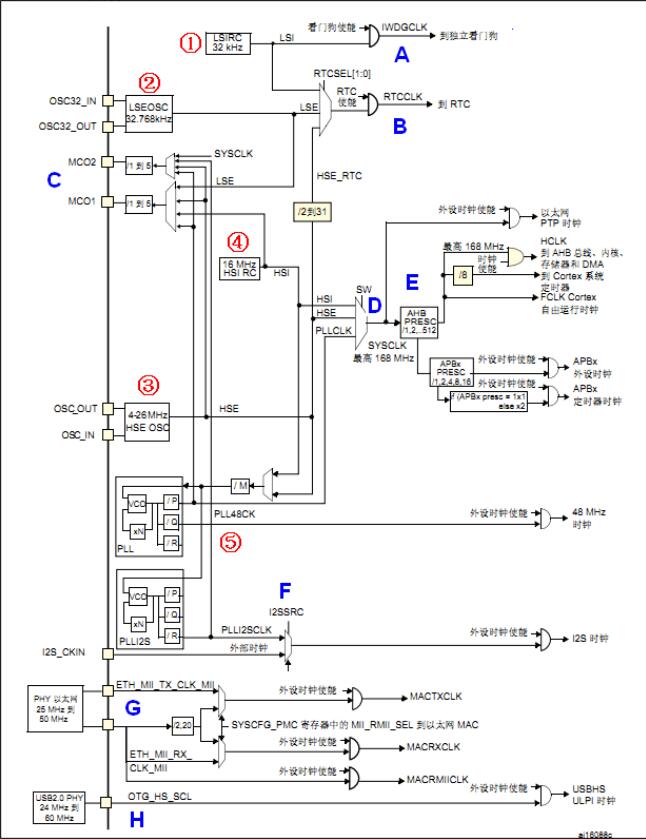

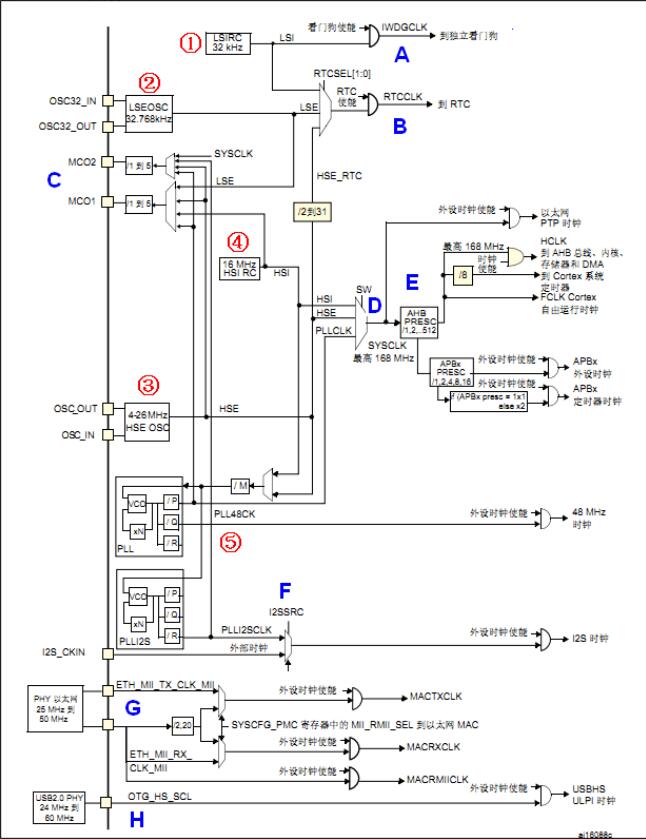

系统时钟图:

在STM32F4中,有5个重要的时钟源,为 HSI、 HSE、 LSI、 LSE、 PLL。 其中 PLL 实际是分为两个时钟源,分别为主 PLL 和专用 PLL。 从时钟频率来分可以分为高速时钟源和低速时钟源,在这 5 个中 HSI, HSE 以及 PLL 是高速时钟, LSI 和 LSE 是低速时钟。从来源可分为外部时钟源和内部时钟源,外部时钟源就是从外部通过接晶振的方式获取时钟源,其中 HSE 和LSE 是外部时钟源,其他的是内部时钟源。下面我们看看 STM32F4 的这 5 个时钟源,我们讲解顺序是按图中红圈标示的顺序:

①、 LSI 是低速内部时钟, RC 振荡器,频率为 32kHz 左右。供独立看门狗和自动唤醒单元使用。

②、 LSE 是低速外部时钟,接频率为 32.768kHz 的石英晶体。 这个主要是 RTC 的时钟源。

③、HSE 是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,频率范围为 4MHz~26MHz。核心板接的是 8M 的晶振。 HSE 也可以直接做为系统时钟或者 PLL 输入。

④、 HSI 是高速内部时钟, RC 振荡器, 频率为 16MHz。 可以直接作为系统时钟或者用作 PLL输入。

⑤、 PLL 为锁相环倍频输出。 STM32F4 有两个 PLL:

1) 主 PLL(PLL)由 HSE 或者 HSI 提供时钟信号,并具有两个不同的输出时钟。

第一个输出 PLLP 用于生成高速的系统时钟(最高 168MHz)

第二个输出 PLLQ 用于生成 USB OTG FS 的时钟( 48MHz),随机数发生器的时钟和 SDIO时钟。

2) 专用 PLL(PLLI2S)用于生成精确时钟,从而在 I2S 接口实现高品质音频性能。

给常见的外设提供时钟:

A. 这里是看门狗时钟输入。从图中可以看出,看门狗时钟源只能是低速的 LSI 时钟。

B. 这里是 RTC 时钟源,从图上可以看出, RTC 的时钟源可以选择 LSI, LSE,以及HSE 分频后的时钟, HSE 分频系数为 2~31。

C. 这里是 STM32F4 输出时钟 MCO1 和 MCO2。 MCO1 是向芯片的 PA8 引脚输出时钟。它有四个时钟来源分别为: HSI,LSE,HSE 和 PLL 时钟。 MCO2 是向芯片的PC9 输出时钟,它同样有四个时钟来源分别为: HSE,PLL, SYSCLK 以及 PLLI2S时钟。 MCO 输出时钟频率最大不超过 100MHz。

D. 这里是系统时钟。从图可以看出, SYSCLK 系统时钟来源有三个方面:HSI,HSE 和 PLL。在我们实际应用中,因为对时钟速度要求都比较高我们才会选用 STM32F4 这种级别的处理器,所以一般情况下,都是才用 PLL 作为 SYSCLK时钟源。根据前面的计算公式,大家就可以算出你的系统的 SYSCLK 是多少。

E. 这里我们指的是以太网 PTP 时钟, AHB 时钟, APB2 高速时钟, APB1 低速时钟。这些时钟都是来源于 SYSCLK 系统时钟。其中以太网 PTP 时钟是使用系统时钟。AHB,APB2 和 APB1 时钟是经过 SYSCLK 时钟分频得来。这里大家记住, AHB最大时钟为 168MHz, APB2高速时钟最大频率为 84MHz,而 APB1低速时钟最大频率为 42MHz。

F. 这里是指 I2S 时钟源。从图 可以看出, I2S 的时钟源来源于 PLLI2S 或者映射到 I2S_CKIN 引脚的外部时钟。 I2S 出于音质的考虑,对时钟精度要求很高。

G. 这是 STM32F4 内部以太网 MAC 时钟的来源。对于 MII 接口来说,必须向外部PHY 芯片提供 25Mhz 的时钟,这个时钟,可以由 PHY 芯片外接晶振,或者使用STM32F4 的 MCO 输 出 来 提 供 。 然 后 , PHY 芯 片 再 给 STM32F4 提 供ETH_MII_TX_CLK 和 ETH_MII_RX_CLK 时钟。对于 RMII 接口来说,外部必须提供 50Mhz 的时钟驱动 PHY 和 STM32F4 的 ETH_RMII_REF_CLK,这个 50Mhz时钟可以来自 PHY、有源晶振或者 STM32F4 的 MCO。

H. 这里是指外部 PHY 提供的 USB OTG HS( 60MHZ)时钟。

关键字:STM32F407ZGT6 时钟系统

引用地址:

STM32F407ZGT6之时钟系统介绍

推荐阅读最新更新时间:2024-03-16 15:38

基于DS1307的多功能时钟系统设计方案

以AT89S52单片机为控制核心,通过实时时钟芯片DS1307和数字温度传感器DS18B20构成了一个多功能的数字时钟系统。详细介绍了整个系统的硬件组成结构、工作原理和系统的软件程序设计。系统采用液晶LCD1602作为显示器,具有实时时间与日历显示、环境温度显示、按键调时、闹铃定时等功能。软件程序采用均采用C语言编写,便于移植与升级。 0 引言 目前家用的数字电子钟,多数只能显示小时、分钟等信息,功能单一,而且大都采用LED数码管作为显示器件,功耗大,不能令消费者满意。为此,笔者开发了一款多功的数字式电子钟,它可以显示年、月、日、小时、分钟等时间信息,同时可以显示环境的温度信息。还具有按键调时、设定闹铃等功能。时钟采用LCD作为显

[模拟电子]

一种基于MSP430单片机的时钟系统设计与实现

MSP430单片机的时钟系统 MSP430根据型号的不同最多可以选择使用3个振荡器。我们可以根据需要选择合适的振荡频率,并可以在不需要时随时关闭振荡器,以节省功耗。这3个振荡器分别为: (1)DCO 数控RC振荡器。它在芯片内部,不用时可以关闭。DCO的振荡频率会受周围环境温度和MSP430工作电压的影响,且同一型号的芯片所产生的频率也不相同。但DCO的调节功能可以改善它的性能,他的调节分为以下3步:a:选择BCSCTL1.RSELx确定时钟的标称频率;b:选择DCOCTL.DCOx在标称频率基础上分段粗调;c:选择DCOCTL.MODx的值进行细调。 (2)LFXT1 接低频振荡器。典型为接32768HZ的时钟振荡器,此

[单片机]

基于DS1307的可调实时时钟系统设计

利用实时时钟芯片 DS1307 设计一个能够调节时间的实时时钟。 介绍采用 I2C 总线接口实时时钟芯片 DS1307 进行准确定时的设计原理, 提出实时时钟芯片 DS1307 与单片机接口电路的设计方法,同时给出几个典型程序实例,通过 Proteus 软件进行仿真实现。 先来说说实时时钟DS1307的使用! DS1307 是一款十分常用的实时时钟芯片,它可以记录年、月、日、时、分、秒等信息,提供至2100年的记录。可使用电池供电,也就是说,即使Arduino 在断电状态下,时钟芯片仍然是在运行的。它使用十分常用的两线式串行总线(I2C),只要两根线即可和Arduino 通信。 电控单元的时钟基准通常可利用 CPU 内部定

[单片机]

ATmega48 时钟系统及其分布

Figure12为ATmega48 的主要时钟系统及其分布。这些时钟并不需要同时工作。为了降低功耗,可以通过使用不同的睡眠模式来禁止无需工作的模块的时钟,详见 P32” 电源管理及休眠模式 ” 。下面为时钟系统的详细描述。 CPU 时钟- clkCPU CPU时钟与操作AVR内核的子系统相连,如通用寄存器文件、状态寄存器及保存堆栈指针的数据存储器。终止CPU 时钟将使内核停止工作和计算。 I/O 时钟- clkI/O I/O时钟用于主要的I/O 模块,如定时器/ 计数器、SPI 和USART。I/O 时钟还用于外部中断模块。要注意的是有些外部中断由异步逻辑检测,因此即使I/O 时钟停止了这些中断仍然可以得到监控。此外, USI

[单片机]

单片机系统中日历时钟自动校准及调整

1、概述 在各类检测控制系统中,需要通过日历时钟进行时间上的控制或对事件所发生的时间进行记录。如电网检测系统,路灯控制系统等。但日历时钟时常跑快跑慢的缺陷不可避免。经过日积月累,就会产生较大的误差,这会影响控制与检测的准确性。为了解决日历时钟的准确度问题,我们设计了能够自动校准和调整运行速度的日历时钟。它在每天的12:00和00:00都会自动校准一次,并根据12个小时运行的误差大小自动调整时钟的运行速度。可使时钟运行的准确度相当高。 我们设计的思路是:利用小型收音机中接收部分电路接收中央人民广播电台播出的中心频率为106.1MHz的调频信号,并解调出音频信号,将音频信号输入两个锁相环路。这两个锁相环路分别跟踪800

[单片机]

s3c2440硬件篇之六:系统时钟和定时器

S3C2440有三种时钟:FCLK(用于CPU核),HCLK(用于主机模块),PCLK(用于外设).两种PLL(锁相环):MPLL(用于设置FCLK,HCLK,PCLK),UPLL(用于设置USB设备),. S3C2440的CPU核工作电压为1.2V时,主频FCLK可以达到300M,CPU核工作电压为1.3V时,主频FCLK可以达到400M.为了降低电磁干扰,降低板间的布线要求,s3c2410/s3c2440外接的晶振通常很小,一般为12M,那么如何达到主频FCLK的400M的呢?------PLL倍频。 一.设置主频FCLK主要是通过MPLL来软件实现倍频。MPLL主要由3个值MDIV,PDIV,SDIV来决定。而这3个值是

[单片机]

普通交换机在IEEE 1588时钟同步系统中的应用

引言 随着信息技术和微电子技术的迅猛发展,在电力系统、制造业、过程控制等领域中出现了越来越多的建立在网络环境下的分布式测控系统,时钟同步技术因而成为确保分布式系统性能的必要手段。IEEE 1588精确时钟同步协议(Precision Time Protocol,PTP)由于所具有的高精度(可实现亚微秒级时钟同步)、高可靠性以及基于以太网(UDP/IP)的同步方式,必将在分布式控制领域得到广泛的应用。但是在现有条件下,IEEE 1588协议还远未发挥其应用的潜能。由于该协议定义的时钟同步网络中,需要使用价格很高的透明时钟交换机作为网络连接设备。因此,IEEE 1588目前主要是在类似数字化变电站这样的重要设施中发挥作用。而对于大多

[单片机]

GPS时钟系统在综自变电站中的应用

近几年来,随着变电站自动化水平的提高,在综自变电站中计算机监控系统、微机保护装置、微机故障录波装置以及各类数据管理机得到了广泛的应用,而这些自动装置的配合工作需要有一个精确统一的时间。当电力系统发生故障时,既可实现全站各系统在统一时间基准下的运行监控和事故后故障分析,也可以通过各保护动作、开关分合的先后顺序及准确时间来分析事故的原因及过程。随着电网的日益复杂、装机容量的提高和电网的扩大,提供标准时间的时钟基准成为电厂、变电站乃至整个电力系统的迫切需要,时钟的统一是保证电力系统安全运行,提高运行水平的一个重要措施,是综自变电站自动化系统的最基本要求之一。

一.GPS时钟系统的优越性

变电站采用不同厂家的计算机监控

[嵌入式]

独辟蹊径品内核: Linux 内核源代码导读

独辟蹊径品内核: Linux 内核源代码导读 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号