系统的应用场合及意义

在一个大型会议系统或多媒体电教室系统中往往通过中央控制系统,实现整个系统的集中控制。点击LCD触摸屏,就能实现各种视像信号的快速切换(视频信号、电脑信号)、灯光系统的调光或自动快速模式设定,以及各种音响系统调节,摄像、监控、大屏幕投放、窗帘收放等一系列功能的程序化控制。

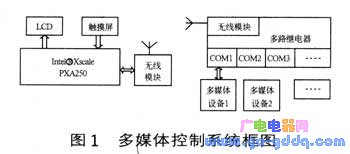

这里的中央控制系统实际上是由一个带处理器的智能控制平台和带多媒体设备接口的多路继电器组成,前台控制器可以设计成固定的台式模式,也可以设计成便于携带的手持设备,它往往是通过无线方式控制多路继电器主机,进而控制各种多媒体设备的开关及运行。嵌入式系统的发展为这一媒体控制器提供了一个可靠的平台,而嵌入式处理器的更新换代则意味着这个平台将更加智能化,体积更小,功耗更低。 Intel公司推出的个人用户端架构(PCA)是一个开放的嵌入式系统开发应用平台,它以XSCALE系列嵌入式处理器为核心,处理器时钟可达1GHz,并可达到1200MIPS,同时支持Linux、WinCE.NET和VxWorks等操作系统,是一个理想的面向无线互连的应用平台。

我们设计的手持式媒体控制器就是在PCA架构下,选用Intel PXA250的硬件平台。媒体控制器所实现的主要功能都是在一个多媒体控制软件上实现的,这个应用软件把多媒体设备的各种操作解析为各个操作码,并提供了一个前台界面可进行编程操作。这些编程命令以无线方式传到一个多路继电器主机,最终实现多媒体设备的智能控制。系统对实时性要求并不很高,我们采用的是微软的Windows CE嵌入式操作系统,它提供了windows程序员熟悉的开发环境,如API函数、ActiveX控件、消息队列、COM接口、ATL和MFC,不仅提高了开发效率,更重要的是,还有利于移植从其它Windows平台上已开发好的应用程序。

设计思路与系统硬件框图

Intel R Xscale PXA250/210处理器是一个具有高集成度的通讯控制芯片,内部集成了一个32bit XscaleRISC处理器内核,并具有逻辑单元、多个通讯信道、LCD控制器、内存PCMCIA控制器和通用的I/O口。它共有3个通用异步串行接口(UART),其中包括一个蓝牙串行口。每个串行口除了通用UART功能外,还包含一个低速红外编解码器,可直接与市售的红外数据协会(IrDA)兼容的LED收发器相连。

从手持设备的无线选择方式来看,主要有三种方案:一是在蓝牙串行口后接一个蓝牙模块;二是选择红外无线遥控;三是用短距离的无线数传芯片。对于蓝牙方案,无线传输距离和芯片价格是值得考虑的地方:蓝牙主要用于短距离传输(最多10米),且芯片价格一直偏高,虽然目前也有使蓝牙传输距离进一步加大的方案(可达100米),但不幸的是,其价格也会比原来贵许多。红外传输则没有价格问题,但从手持设备所能提供的功耗来看,它能传输的距离实在太近,只有几米,且对红外发射角度有一定的要求,存在"必须保证传输信息的两个设备正对,且中间不能有障碍物"等致命的缺陷。与前两种方案相比,采用短距离的无线数传芯片进行无线传输则灵活得多,价格上从低端到高端选择余地很大,传输距离从几十米到几百米都有,功耗毫瓦级的也很多。

考虑到多媒体控制系统的某些应用场合,如多媒体语音教室、多媒体会议室的面积,故对无线设备的传输距离有一定的要求,最好在百米范围内并有一定穿透力为宜,且由于属于手持设备,功耗应尽可能小。无线设备主要传输的是继电器动作及媒体控制命令,因此无线通信的数据量不大,对无线模块的速度要求不高。综合以上分析,媒体控制手持设备的无线模块最好采用第三种方案,即选用短距离低功耗的无线射频芯片。无线模块与INTEL PXA250连接也有多种选择,如GPIO、IIC、USB、串口等,从硬件连接及通信协议最简化来看,选择串口与无线模块相连是最佳的。

媒体控制手持设备主要功能描述如下:

1.CPU

采用Intel的Xscale PXA250处理器,运行于400MHz(Xscale core);

32Bit RISC处理器,具有32K指令缓冲,32K数据缓冲,MMU单元,Mini cache;

很低的电源要求,可由锂电池或AA/AAA电池供电;

内部PCMCIA控制器;

2.内存

采用三星SDRAM,32M字节SDRAM内存(最大可到64Mbytes);

采用Intel的快速页面读取模式的StrataFlash,16M字节Flash内存(最大可到32Mbytes);

3.外没

TFT 640 ×480 LCD,真彩色,带触摸屏;

AD触摸屏控制器及四线电阻式触摸屏接口;

用户定义的多功能按键;

串行接口; 以太网接口;

DC-DC高效率的电源转换或低价位的电源转换;

直流电源输入接口;

JTAG接口;

射频无线模块;

多个LED指示灯;

锂电池的充电和供电系统;

无线数传模块设计

市面上的射频芯片很多,除了距离、功耗上的考虑外,选择射频波段也很重要:这个频段不会影响其它无线设备的正常工作,如手机、电器等;它的频段要合适,避免是国家管制的波段。基于以上几点,我们选择挪威norDIC公司的nRF401。

nRF401是采用FSK方式的为433MHz ISM频段设计的半双工无线收发芯片。传输速率最高可达19.6K,发射功率可调,最大发射功率+10dBm,还有待机模式,以便更加省电。实测的传输距离超过200米,工作电压从2.7V到5V,符合系统所需的要求。

芯片主要管脚说明如表1所示:

芯片采用SSOIC20的封装,外围电路设计非常简单。它不需要对芯片进行初始化和配置,数据可以透明传输,不用专门进行编码解码。发射、接收宇数据接口采用串行形式,发射器以及接收器完全独立进行操作,并具有休眠功能。芯片具有载波检测,发射、接收以及载波检测路径包含通带滤波器,以使信号在调制解调器各部分得到完善。在信号条件比较差的情况下具有优良的灵敏度,使产品的性能在高噪声环境下完善。布线时,RP电路对电源噪声很敏感,要给RP电源加滤波电路,以减小电源噪声对RF电路的干扰,最好在芯片电源引脚加旁路电容。射频电路的元件面以nRF401为中心,各元件紧靠其周围,尽可能减少分布参数的影响。数字信号只能在电路板的数字部分布线,模拟信号只能在电路板的模拟部分布线,并且模拟电源和数字电源要分割,要注意大面积地的连续性。

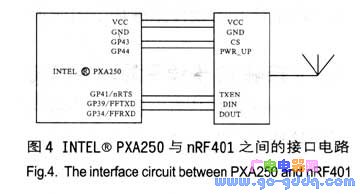

由图3可见,嵌入式CPU对无线模块的控制接口主要由5根信号线组成,分另U是DIN、DOUT、TXEN、PWR_UP、CS。其中PWR_UP是节能控制端,利用IntelPXA250的一个GPIO对其进行编程,以实现无线模块的工作模式与休眠状态的切换。工作时手持设备仅与继电器主机进行半双工通信,因此频道选择信号CS可以任意选择,或亦用GPIO设置。Intel PXA250的全功官臣串口(FullFunction UART)支持MODEM信令,可以利用这个串口控制DIN、DOUT、TXEN信号,串口的nRTS接TXEN。这里需要注意的是要对nRTS进行延时处理,因为nRF401发送到接收的转换时间为5ms,所以延时要大于5ms。

无线模块软件设计

无线模块通过UART与系统连接,包括GUI用户应用程序也通过访问串口驱动程序来访问设备,所以必须对UART进行初始化。INTEL R PXA250的UART符合RS-232标准,也支持16550工业标准的大部分功能,通讯的最高速度可以达到230.4kbps。

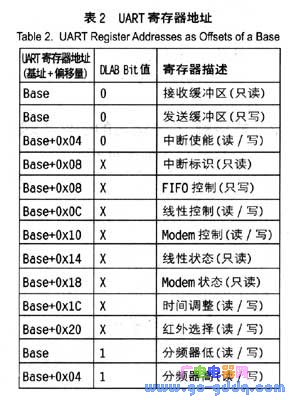

PXA250共有3个通用异步串行接口(UART),启动时UART默认状态是无法使用,必须通过编程GPIO寄存器来使能它们。每个UART有一个64 ×8位的FIFO用于缓冲输出数据,一个64 × 1l位的FIFO用于缓冲输入数据(其中的3位存放每个接收字符的帧、奇偶校验和接收FIFO溢出出错标志)。当UART单元被禁止时,发送器和接收器完成当前操作后停止任何数据传送。此时FIFO中的数据并没有被清空,一旦UART再次使能,发送接收可以重新开始。此外,将中断允许寄存器(IER)的位5置高,UART还可以进行NRZ译码操作。

每个UART共有13个寄存器:其中12个用于UART操作,1个用于低速红外调制功能。寄存器是32位,但只有最低的8位装载的是有效数据。12个UART寄存器共享了I/O地址空间中的9个地址,基地址也是32位。各控制寄存器决定着UART各种模式、传送方式以及波特率分频系数,状态寄存器可以反映芯片目前的读写状态以及错误类型,数据寄存器分别对应于发送FIFO顶部和接收FIFO底部:读出RBRll位接收FIF0底部的8位数据、3位出错标志;写入TBR发送FIFO顶部8位数据。对这些寄存器的正确配置和读写是初始化UART的必要条件。寄存器SLDR[DLAB]位的状态决定着一些UART寄存器的选择模式,为了能对分频器寄存器进行操作,必须通过软件对SLDR[DLAB]位置高。

对这些寄存器的正确配置和读写是初始化UART的必要条件。除此以外还需要一些串行口的接口函数,它们包括:

1 void Uart_Init(int Uartnum,int mclk,int baud)

功能:初始化串行口,设置串行口通讯的波特率

参数说明:Uartnum:所设定的串行口号

mclk:系统的主时钟频率

band:所设定的串行口通讯的波特率

2 void Uart_Printf(Char*FMt,…)

功能:输出字符串到串口0

参数说明:fmt:输出到串行口的字符串

3 char Uart_etch(int Uartnum)

功能:接收指定串口的数据,收到数据时返回,返回串口接收到的数据

参数说明:Uartnum:所设定的串行口号

4 void Uart_SendByte(int Uartnum,int data)

功能:向指定的串口发送数据

参数说明:Uartnum:所设定的串行口号

data:发送的数据

在操作系统环境下,系统启动时会自动初始化串行口,所以应用程序调用串行口资源将变得更容易。值的注意的是,应用程序往往是多任务系统,为了实时监测串行口信息,在操作环境中一般单开一个串行口扫描任务,保证信息不丢失。在一个已有的工程文件的主函数MAIN中添加串行口的寄存器初始化代码,并添加串行口扫描任务。由于对无线模块的控制还有系统的GPl0,所以扫描程序中还要包括对10的操作。当系统收到串行口信息时,将会自动向主任务发送一个串行口消息。主任务接收到该消息,将会调用响应函数,响应该消息。

结束语

这种无线手持设备除了应用于媒体控制系统外,还可以用于无线遥控系统、机器人控制、信息家电、无线PDA点菜系统等等。在高达400MHz的时钟速度运行的PXA250应用处理器将为许多全功能的手持通信设备、信息通信系统和PDA提供先进的集成度、领先的多媒体性能和更好的节能性。在Intel功能强大的PCA平台(个人用户端架构)下,系统设计人员可以不必过多的考虑CPU的处理瓶颈而把更多的精力放在应用开发上。

上一篇:基于嵌入式Linux系统的3G/4G路由器

下一篇:Reset在嵌入式系统中应用的稳定性

推荐阅读最新更新时间:2024-03-16 15:54

现代操作系统(原书第4版)

现代操作系统(原书第4版) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号