通过给晶体管增加一些电容、二极管和电阻,使用保持时间可调的复位IC,将纯手动复位转换为自动复位。

在大多数应用中,![]() (手动复位)引脚通常与开关相连,为管理芯片制造手动复位信号。随后,在预先设定的有效延时时间后,其从低电平有效复位回到高电平状态。手动复位适用于大多数应用;然而,它需要人为干涉产生复位信号。在一些应用中,手动复位存在争议,因为系统每次上电时都要执行。

(手动复位)引脚通常与开关相连,为管理芯片制造手动复位信号。随后,在预先设定的有效延时时间后,其从低电平有效复位回到高电平状态。手动复位适用于大多数应用;然而,它需要人为干涉产生复位信号。在一些应用中,手动复位存在争议,因为系统每次上电时都要执行。

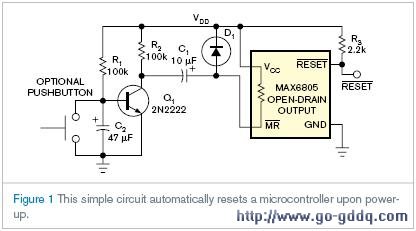

更进一步,包括 嵌入式 处理器在内的应用需要复位输出为保持高电平——也就是说,非有效——在应用复位或低有效之前的某个时期。如图1电路在设备上电时无需按下复位键的情况下,被证实是有效的,因为在复位的低信号到来之前,复位自动以预先设定的保持时间发生。

电路使用带![]() 引脚和低有效输出

引脚和低有效输出![]() 的复位管理芯片。通常

的复位管理芯片。通常![]() 输入的内部上拉电阻为20到50kΩ。上电期间,

输入的内部上拉电阻为20到50kΩ。上电期间,![]() 内部电阻将电容C1充电到正向最大值VDD。为管理芯片产生

内部电阻将电容C1充电到正向最大值VDD。为管理芯片产生![]() 复位输入,其

复位输入,其![]() 输入必须接收低有效的地信号,需要晶体管Q1导通。这个导通的时间长度取决于R1和C2的RC时间常数。这两个器件决定Q1什么时候导通,从而为

输入必须接收低有效的地信号,需要晶体管Q1导通。这个导通的时间长度取决于R1和C2的RC时间常数。这两个器件决定Q1什么时候导通,从而为![]() 输出提供保持时间可调的高电平。为增加保持时间,增加R1和C2的RC时

输出提供保持时间可调的高电平。为增加保持时间,增加R1和C2的RC时

间常数即可。

复位管理芯片只在![]() 管脚的电压超过触发阈值电压和管理器内部复位周期结束时,产生

管脚的电压超过触发阈值电压和管理器内部复位周期结束时,产生![]() 输出。这个延时时间滤除了所有输入电压的毛刺。因为Q1的导通,使C1的负向变为地。而C1的正向不能立即改变极性,其被拉低并通过

输出。这个延时时间滤除了所有输入电压的毛刺。因为Q1的导通,使C1的负向变为地。而C1的正向不能立即改变极性,其被拉低并通过![]() 输入的内部上拉电阻,缓慢的再次充电。当达到复位芯片的阈值电压时,一旦达到芯片的延时时间便输出复位信号。C1的选择并不严格。然而,它的值应该尽量大——例如0.1到10µF——使C1和内部上拉电阻所得的RC时间常数足够大。这个值确保C1在

输入的内部上拉电阻,缓慢的再次充电。当达到复位芯片的阈值电压时,一旦达到芯片的延时时间便输出复位信号。C1的选择并不严格。然而,它的值应该尽量大——例如0.1到10µF——使C1和内部上拉电阻所得的RC时间常数足够大。这个值确保C1在![]() 引脚上保持了至少1us的低电平。

引脚上保持了至少1us的低电平。

C2充电到Q1的偏置电压后,晶体管仍然导通。在下一次上电或手动按键复位电路时,晶体管C2放电。这个动作一旦发生,Q1关闭。R1将C1的负向充电到供电电压VDD。因为电容C1的正向不能立即改变,其表现为充电到2VDD。然而,保护二极管D1将C1的电压箝位到仅为VDD加上二极管的导通电压。一旦C2充电足够使Q1再次导通时,重复循环。

英文原文:

IC performs delayed system reset upon power-up

By adding a transistor with some caPACitors, diodes, and resistors, you CAN transform a pure-manual reset to an automatic reset with adjustable hold time for the reset IC.

Goh Ban Hok, Infineon Technologies Asia Pacific Ltd, Singapore; Edited by Charles H Small and Fran Granville -- EDN, 2/7/2008

In most applications, the (manual-reset) PIN usually connects to a switch to create a manual-reset signal to the supervisory Chip. Subsequently, after a predetermined time-out-active period, it goes back to the high state in an active-low reset. A manual reset is a good feature for most applications; however, it requires human intervention to create the reset. In some applications, a manual reset could be a hassle because you must perform it each time the system powers up.

Further, applications involving embedded microprocessors can require the reset output to hold high—that is, inactive—for a certain period of time before you can apply the reset, or active low. The circuit in Figure 1 proves usefulduring power-up when there is no need to press the reset button once the device powers up, because reset oCCurs automatically with the predetermined hold time before you apply the reset-low signal.

上一篇:同步与异步复位以及相关的亚稳态状况与设计可靠性

下一篇:5x系列芯片的复位入口问题

硅光子设计(从器件到系统)

硅光子设计(从器件到系统) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号