1、Cortex-M3存储器映射

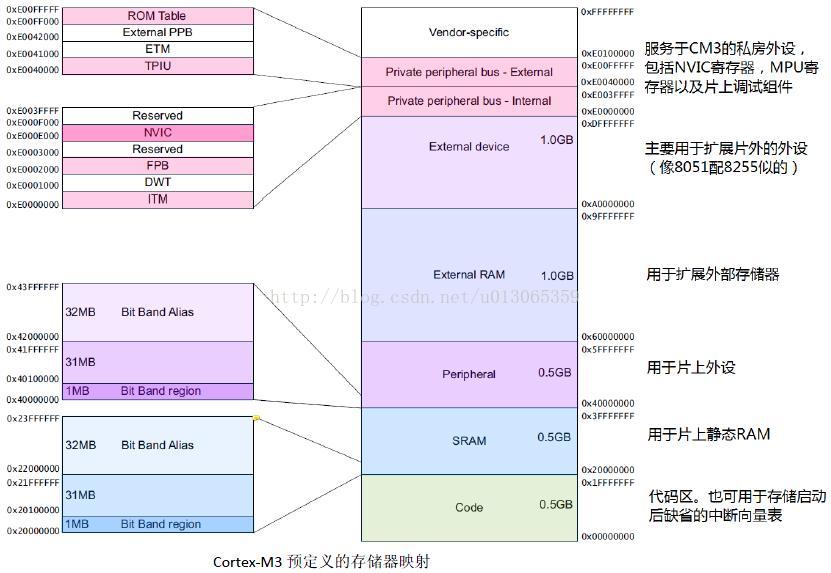

CM3的地址空间有4G,但它只对这4G空间作了预先的定义,把4G空间分成8个块,每块大小为512M,并指出各段该分给哪些设备。具体的实现由芯片厂商决定,厂商可以设计出具有自己特色的产品。下图是CM3的存储器映射图(来自CM3权威指南)。

内部SRAM 区的大小是512MB,用于让芯片制造商连接片上的SRAM,这个区通过系统总线来访问。在这个区的下部,有一个1MB 的位带区,该位带区还有一个对应的32MB 的 “位带别名(alias)区”,容纳了8M 个“位变量”(对比8051 的只有128 个位)。位带区对应的是最低的1MB 地址范围,而位带别名区里面的每个字对应位带区的一个比特。位带操作只适用于数据访问,不适用于取指。通过位带的功能,可以把多个布尔型数据打包在单一的字中,却依然可以从位带别名区中,像访问普通内存一样地使用它们。位带别名区中的访问操作是原子的,消灭了传统的“读-改-写”三步曲。

地址空间的另一个512MB 范围由片上外设(的寄存器)使用。这个区中也有一条32MB的位带别名,以便于快捷地访问外设寄存器。例如,可以方便地访问各种控制位和状态位。要注意的是,外设内不允许执行指令。

还有两个1GB 的范围,分别用于连接外部RAM 和外部设备,它们之中没有位带。两者的区别在于外部RAM 区允许执行指令,而外部设备区则不允许。

最后还剩下0.5GB 的隐秘地带,CM3 内核的闺房就在这里面,包括了系统级组件、内部私有外设总线s、外部私有外设总线s、以及由提供者定义的系统外设。私有外设总线有两条:

AHB 私有外设总线,只用于CM3 内部的AHB 外设,它们是:NVIC, FPB, DWT 和ITM。

APB 私有外设总线,既用于CM3 内部的APB 设备,也用于外部设备(这里的“外部”是对内核而言)。CM3 允许器件制造商再添加一些片上APB 外设到APB 私有总线上,它们通过ABP 接口来访问。

NVIC 所处的区域叫做“系统控制空间(SCS)”,在SCS 里的还有SysTick、MPU 以及代码调试控制所用的寄存器,如下图所示

最后,未用的提供商指定区也通过系统总线来访问,但是不允许在其中执行指令。

CM3 中的MPU 是选配的,由芯片制造商决定是否配上。

上述的存储器映射只是个粗线条的模板,半导体厂家会提供更展开的图示,来表明芯片中片上外设的具体分布,RAM 与ROM 的容量和位置信息。

2、STM32的存储器映射

从STM32 datasheet上来看,不同的型号,其存储器映射有些不同。应该是以小容量、中容量、大容量来区别的,同一个容量的不同型号,其Flash、SRAM也有所不同,FSMC也不同。下面以STM32F103xx为例分别介绍之,以下数据均来自datasheet及STM32参考手册。

2.1 小容量STM32F103x4、STM32F103x6存储器映射图

2.2 中容量STM32F103x8、STM32F103xB存储器映射图

3.3 大容量STM32F103xC、STM32F103xD、STM32F103xE存储器映射图

总结:上面三幅图中红色字标明了同种容量的芯片的SRAM和Flash大小,不同容量的芯片其外设不一样,但同一外设对应地址是一样的,如果没有相应外设,该地址则保留。拿TIM来说,大容量有TIM2-TIM7,而小容量只有TIM2和TIM3,但它们(TIM2、TIM3)映射的地址却相同,小容量中向上多出的空间则保留,因此RTC在各容量芯片上对应的起始地址都是0X4000 2800。同理SRAM和Flash也是一样。

2.4 SRAM

STM32F10xxx内置了最多为64K的SRAM,它可以以字节、半字(16位)或全字(32位)访问。SRAM的起始地址是0X2000 0000

2.5 Flash

STM32F10xxx内置了最多为512的Flash,其组织结构根据容量的不同而有所不同,如下所示:

闪存的指令和数据访问都是通过AHB总线完成的,预取模块是用于通过ICode总线读取指令的,仲裁是作用在闪存接口,并且DCode总上的数据访问优先。

对于编程和擦除,闪存编程一次可以写入16位(半字),闪存擦除操作可以按页面擦除或完全擦除(全擦除)。全擦除不影响信息块。为了确保不发生过度编程,闪存编程和擦除控制器是由一个固定的时钟控制的。写操作(编程或擦除)结束时可以触发中断,仅当闪存控制器接口时钟开启时,此中断可以用来从WFI模式退出。

小容量芯片

中容量芯片

大容量芯片

上一篇:STM32芯片命名

下一篇:STM32F1(Cortex M3内核)存储器映射

推荐阅读最新更新时间:2024-03-16 16:04

嵌入式C语言自我修养——从芯片、编译器到操作系统 带目录 文字版

嵌入式C语言自我修养——从芯片、编译器到操作系统 带目录 文字版 硬件架构艺术:数字电路的设计方法与技术

硬件架构艺术:数字电路的设计方法与技术

京公网安备 11010802033920号

京公网安备 11010802033920号