CM3内核正常工作时是按照指令顺序执行的,当发生异常或者中断时,将打断正在执行的动作,进而执行异常或中断的服务程序。

异常系统具有保障CM3工作的安全性和健壮性的作用。

1 异常类型

异常分为复位(Reset),不可屏蔽中断(NMI),硬件错误(HardFault),存储管理错误(MemManageFault),总线错误((BusFault)),用法错误(UsageFault),系统调用(SVC),可悬挂系统调用(PendSV),系统节拍(SysTick)等。

2 优先级的定义

当异常存在多个时,就会出现竞争,进而出现优先级的概念。当不同的异常发生时,究竟该响应哪一个?这是由优先级来决定的。

在 CM3 中,优先级对于异常来说很关键的,它会影响一个异常是否能被响应,以及何时可以响应。优先级的数值越小,则优先级越高。 CM3 支持中断嵌套,使得高优先级异常会抢占(preempt)低优先级异常。有 3 个系统异常:复位, NMI 以及硬 fault,它们有固定的优先级,并且它们的优先级号是负数,从而高于所有其它异常。所有其它异常的优先级则都

是可编程的(但不能编程为负数)。

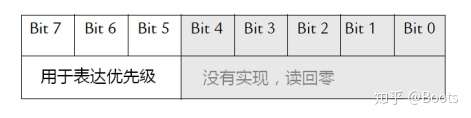

原则上,CM3可支持256级的可编程优先级,但是芯片公司考虑到成本以及精简设计,只会支持少于256的优先级,比如8,16,32等。

以下的3位(MSB高位对齐)表示,可以支持8级优先级:

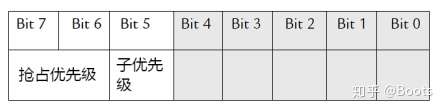

但是,优先级的规定并不是只用“抢占优先级”来定义,为了使抢占机能更加可控,CM3还把256级优先级分成高低两段,分别是抢占优先级和亚优先级。二者占的位数不同,也就是所谓的优先级分组。

抢占优先级最多有7位,所以最多128个抢占级。

在计算抢占优先级和亚优先级的有效位数时,必须先求出下列值:

1 芯片实际使用了多少位来表达优先级.

2 优先级组是如何划分的。

举个例子,如果只使用 3 个位来表达优先级([7:5]),并且优先级组的值是 5(从比特 5

处分组),则你得到 4 级抢占优先级,且在每个抢占优先级的内部有 2 个亚优先级。

通过这样的优先级机制,可以对异常或者中断进行优先级编程(手动指定优先级)。

3 向量表

当发生了异常并且要响应它时, CM3 需要定位其处理例程的入口地址(函数入口地址)。这些入口地址存储在所谓的“(异常)向量表”中。CM3 认为该表位于零地址处,且各向量占用 4 字节,因此每个表项占用 4 字节。

4 Fault类异常

有若干个系统异常专用于 fault 处理。 CM3 中的 Faults 可分为以下几类:

1 总线 faults (取指出错,POP/PUSH错误)

2 存储器管理 faults (访问MPU范围外的地址,往只读区域写数据,用户级访问特权级地址)

3 用法 faults (未定义指令,除数为0)

4 硬 faults (前三者错误的服务例程无法执行时,变为HardFault)

5 SVC和PendSV

操作系统中的任务调度,用户/内核态的上下文切换,可以通过SVC和PendSV异常来实现。

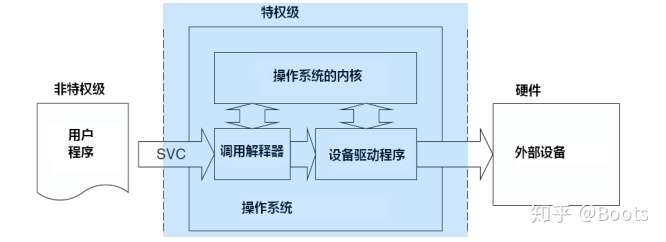

SVC(系统服务调用,亦简称系统调用)和 PendSV(可悬起系统调用),它们多用于在操作系统之上的软件开发中。 SVC 用于产生系统函数的调用请求。例如,操作系统不让用户程序直接访问硬件,而是通过提供一些系统服务函数,用户程序使用 SVC 发出对系统服务函数的呼叫请求,以这种方法调用它们来间接访问硬件。因此,当用户程序想要控制特定的硬件时,它就会产生一个 SVC 异常,然后操作系统提供的 SVC 异常服务例程得到执行,它再调用相关的操作系统函数,后者完成用户程序请求的服务。

这种“提出要求——得到满足”的方式,很好、很强大、很方便、很灵活、很能可持续发展。首先,它使用户程序从控制硬件的繁文缛节中解脱出来,而是由 OS 负责控制具体的硬件。第二, OS 的代码可以经过充分的测试,从而能使系统更加健壮和可靠。第三,它使用户程序无需在特权级下执行,用户程序无需承担因误操作而瘫痪整个系统的风险。第四,通过 SVC 的机制,还让用户程序变得与硬件无关,因此在开发应用程序时无需了解硬件的操作细节,从而简化了开发的难度和繁琐度,并且使应用程序跨硬件平台移植成为可能。开发应用程序唯一需要知道的就是操作系统提供的应用编程接口(API),并且了解各个请求代号和参数表,然后就可以使用 SVC 来提出要求。

另一个相关的异常是 PendSV(可悬起的系统调用),它和 SVC 协同使用。一方面, SVC异常是必须立即得到响应的(若因优先级不比当前正处理的高, 或是其它原因使之无法立即响应, 将上访成硬 fault——译者注), 应用程序执行 SVC 时都是希望所需的请求立即得到响应。另一方面, PendSV 则不同,它是可以像普通的中断一样被悬起的(不像 SVC 那样会上访)。 OS 可以利用它“缓期执行” 一个异常——直到其它重要的任务完成后才执行动作。 悬起 PendSV 的方法是: 手工往 NVIC 的 PendSV 悬起寄存器中写 1。 悬起后, 如果优先级不够高,则将缓期等待执行。

PendSV 的典型使用场合是在上下文切换时(在不同任务之间切换)。 例如, 一个系统中有两个就绪的任务,上下文切换被触发的场合可以是:

1 执行一个系统调用

2 系统滴答定时器(SYSTICK)中断,(轮转调度中需要)

任务中正在响应中断时(IRQ),是不能进行上下文切换的。如果 OS 检测到某 IRQ 正在活动并且被 SysTick 抢占(进行任务间的上下文切换),它将悬起一个 PendSV 异常,以便缓期执行上下文切换。

上一篇:ARM基础篇—ARM微处理器的应用领域及特点

下一篇:【ARM】Cortex-M3 存储器系统

推荐阅读最新更新时间:2024-11-13 13:51

设计资源 培训 开发板 精华推荐

- DRSSTC/SSTC并管功率桥

- 具有低噪声旁路的 LTM8057MPY 12V 反激式转换器的典型应用电路

- AD9215BRU-80EBZ,AD9215BRU-80 评估板,3 V 单电源,10 位,80 MSPS 模数转换器 (ADC)

- LTC1550LCMS8-2 -4.1V 输出 GaAs FET 偏置发生器的典型应用电路

- ADV3221-EVALZ,ADV3221 800 MHz、4:1模拟多路复用器评估板

- 带EV-VN7xxx连接器的盲点教育工具连接器板

- RSO-0512S 12V、83mA输出DC/DC转换器典型应用电路

- 基于MT3608卡片式、插件式可调升降压电源模块

- 使用 ROHM Semiconductor 的 BU4315 的参考设计

- LDFMPT-TR、0.8V/0.5A 极低压降稳压器的典型应用电路

usb_host_device_code

usb_host_device_code 嵌入式实时操作系统的多线程计算-基于ThreadX和ARM

嵌入式实时操作系统的多线程计算-基于ThreadX和ARM 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号