1. 组织结构:

存储芯片有几个重要的单位 device block page ,在这个芯片中

1 Device = 2048 block = 2k block

1 block = 64 page

1 page = (2048 + 64) Byte

其中:

块Block,是Nand Flash的擦除操作的基本/最小单位。

页Page,是Nand Flash的读写操作的基本单位/最小单位。

共256M,也就是需要28根地址线来寻址,但是文档中是29根线,因为在寻址的时候,我们必须先找到page地址然后再找到页内地址。

页地址共有: 2048 * 64 page ,也就是2的(11+6)次方 ,即17跟地址线

页内地址: 2048 + 64 ,也就是2的(11 + 1)次方 ,即 12跟地址线,注意这里的64个字节是一段特殊的区域叫做OOB,用于数据的校验,只需要一根地址线标识

2. 寄存器说明

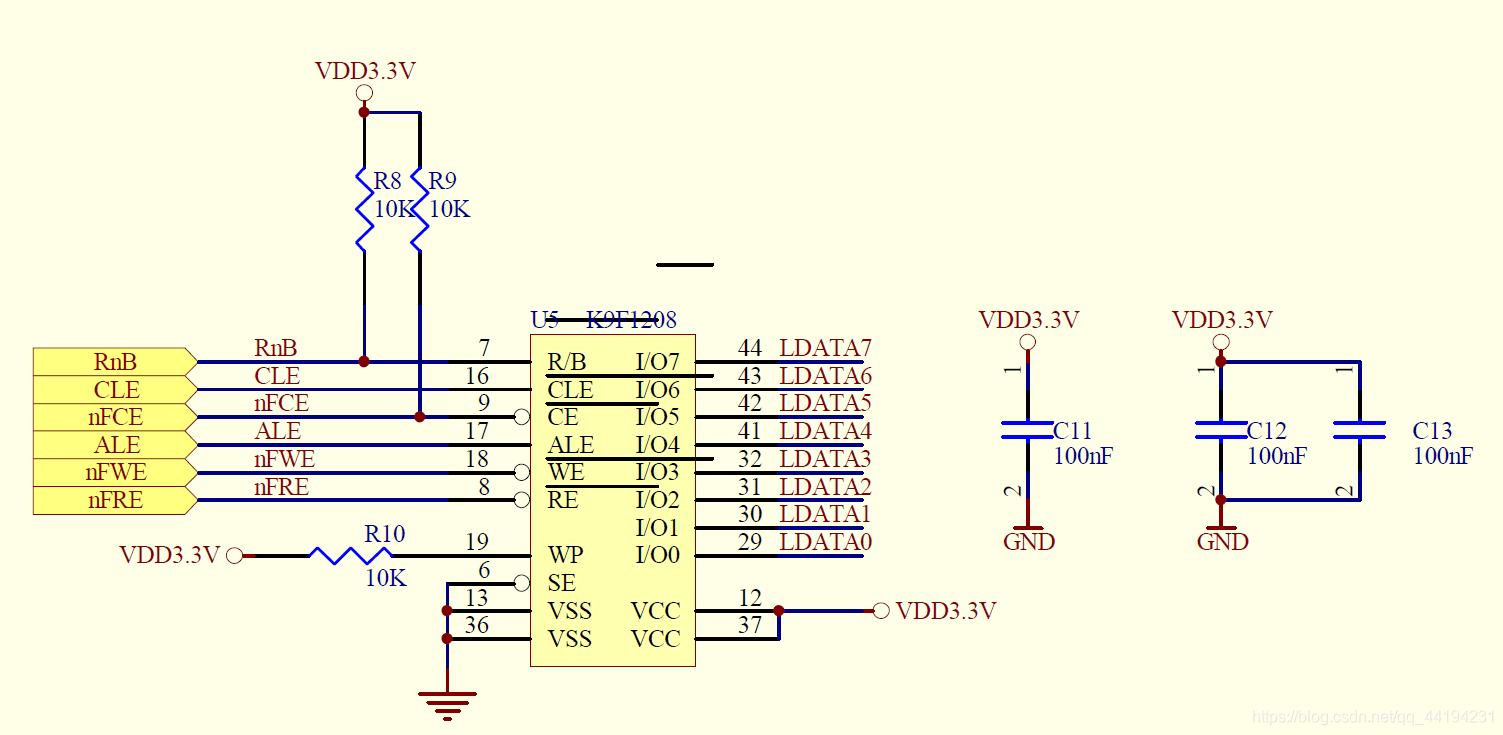

只有数据线,没有地址线

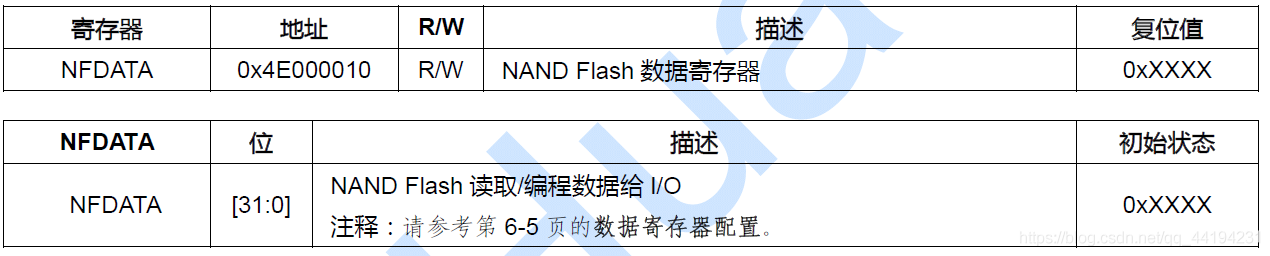

8的数据线可以传输: 数据,地址和命令(功能),通过一些引脚来控制

但是CPU并不直接与Nand Flash交互,而是通过soc内的Nand Flash控制器来间接设置Nand Flash,其中含有很多的寄存器,CPU只需直接对这些寄存器进行操作就可以了

I/O0 ~ I/O7 用于输入地址/数据/命令,输出数据

CLE 则 数据线中是 命令

ALE 则 数据线中是 地址

WE 则 数据线中是 数据 方向是输入(从存储器角度)

RE 则 数据线中是 数据 方向是输出(从存储器角度)

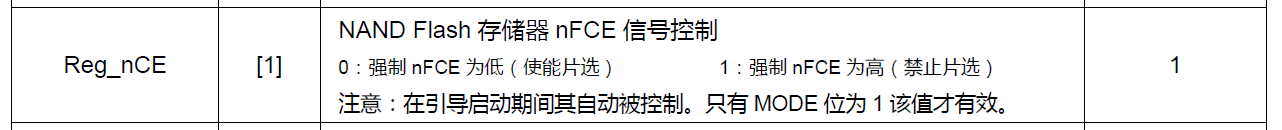

CE 片选

R/B 空闲状态或者是忙状态

WP 写保护,使能后无法写入,由电路实现

除此以外还有一个配置寄存器,用来设置脉冲宽度

3. 常见的Nand Flash操作

写入数据就是page program,因为page是写入的最小单位

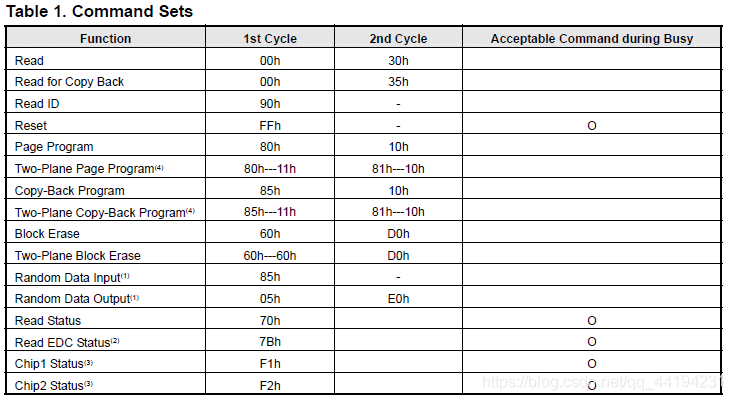

从上图可以看到,如果要实现读一个页的数据,就要发送Read的命令,而且是分两个周期(Cycle),

即分两次发送对应的命令,第一次是0x00h,第二次是0x30h,而两次命令中间,需要发送对应的你所要读取的页的地址,关于此部分详细内容,留待后表。对应地,其他常见的一些操作,比如写一个页的数据(Page Program),就是先发送0x80h,然后发生要写入的地址,再发送0x10h。

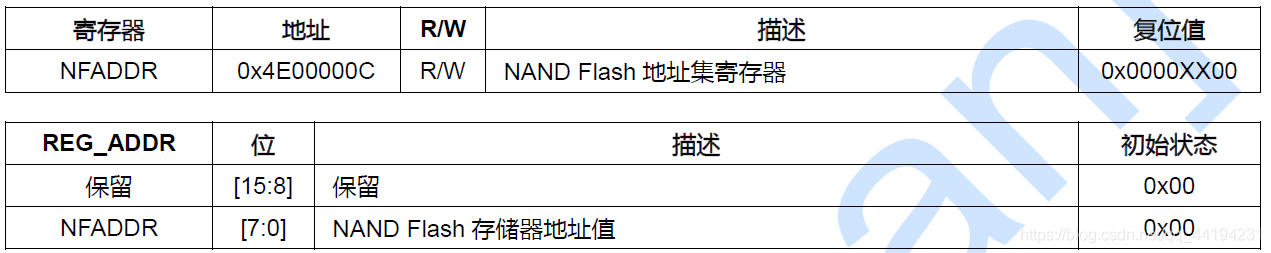

4. Nand Flash的地址

物理地址 =块大小×块号 + 页大小×页号 + 页内地址

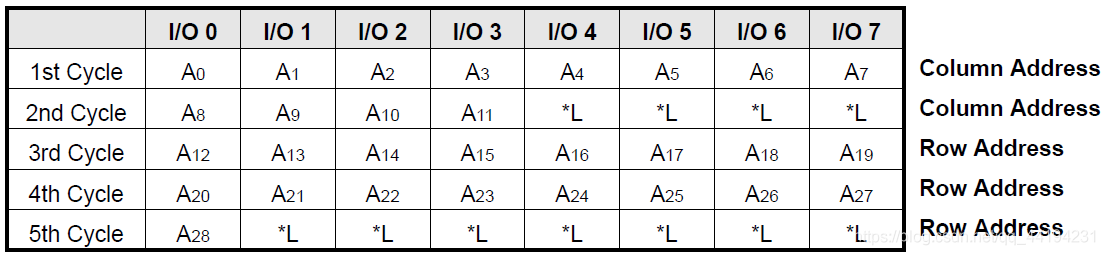

此Nand Flash地址周期共有5个,2个列(Column)周期,3个行(Row)周期。

①.每个page的大小为(2048+64)KB,对应地,列地址A0~A10,就是页内地址,地址范围是从 0 到 2047。但是为何此处多出来个A11呢?实际上,由于我们访问页内地址,可能会访问到OOB的位置,即2048-2111这64个字节的范围内,所以,此处实际上只用到了2048~2111,用于表示页内的oob区域,其大小是64字节。

②.每个block有64个page,对应地,A12~A17,称作页号,可以定位到对应的块的哪一个页

③.每个device有2048个block,对应地,A18~A28,表示对应的块号,即属于哪个块

5. Nand Flash操作过程举例

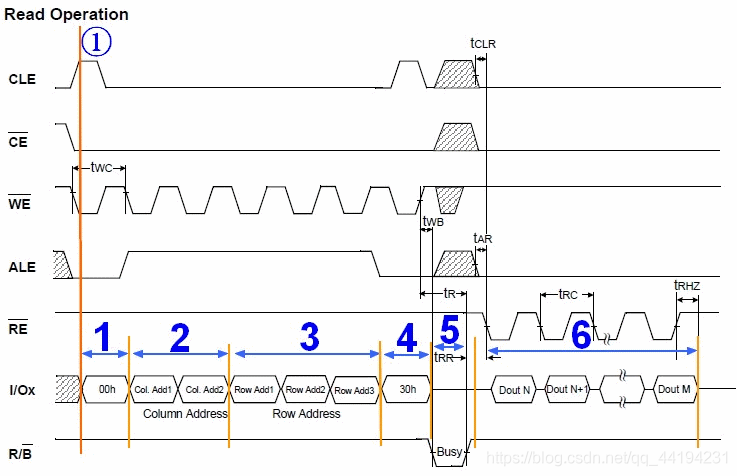

以读操作为例,先发一个图中读命令的第一个阶段的0x00,表示,让硬件先准备一下,接下来的操作是读。发送两个周期的列地址。也就是页内地址,表示,我要从一个页的什么位置开始读取数据。接下来再传入三个行地址。对应的也就是页号。然后再发一个读操作的第二个周期的命令0x30。

接下来,Nand Flash内部硬件逻辑,负责去按照你的要求,根据传入的地址,找到哪个块中的哪个页,然后把整个这一页的数据,都一点点搬运到页缓存中去。而在此期间,你所能做的事,也就只需要去读取状态寄存器,看看对应的位的值,也就是R/B#那一位,是1还是0,如果是0的话,就表示,系统是busy,仍在”忙“(着读取数据),如果是1,就说系统活干完了,忙清了,已经把整个页的数据都搬运到页缓存里去了,你可以接下来读取你要的数据了。

5.设置Nand Flash启动的过程

S3C2440的Nand Flash大小为256MB,然后硬件把前4K内容复制到片内的SRAM中,再取指令并执行。

https://www.cnblogs.com/shangdawei/archive/2013/05/14/3077018.html

上一篇:ARM裸机学习二:S3C2440的串口使用

下一篇:S3C2440的中断机制

推荐阅读最新更新时间:2024-11-11 18:06

设计资源 培训 开发板 精华推荐

- 555_无线充电

- 18650电源模块

- 送药小车

- AM2G-1218SZ 18V 2 瓦 DC/DC 转换器的典型应用

- LT1615 的典型应用 - ThinSOT 中的微功率升压型 DC/DC 转换器

- AP1501 3A PWM Buck DC/DC Converter for Fixed Type Circuit的典型应用

- DC2222A-B,基于 LTC2508-32 的演示板,具有可配置数字滤波器的 32 位过采样 ADC

- STM32F411-BOARD

- EVAL-ADuC7020MK,用于 ADuC7020 MCU 的迷你套件

- TCR2BE11、200mA、1.1V输出电压CMOS低压降稳压器在ESV中具有自动放电的典型应用(SOT-553)

- iPhone12 Pro屏幕成绩揭晓,全球第三,但输给了国产机型

- 在德国慕尼黑电子展上,欧洲半导体公司CEO们都说了啥

- 如今的手机摄像头为什么越来越多?

- iPhone 12 Pro Max拆解照解密:主板袖珍、L型电池仅3687mAh

- Caviar推Apple Watch 6限量版系列 镶嵌109颗钻石

- 人机共融时代一定会到来,智能制造也将迈上新的台阶

- 熊猫机器人:以控制系统为切入点,工业机器人领域稳步前行

- LG电子公开可支持人体下肢肌肉力量的可穿戴机器人,助力布局机器人领域

- 法国新款工业机器人Skypod:能以10英里/小时的速度进行三维移动

- “倒春寒”来临是下马威还是警醒?国产机器人什么时候才能迎来春天?

usb_host_device_code

usb_host_device_code 嵌入式实时操作系统的多线程计算-基于ThreadX和ARM

嵌入式实时操作系统的多线程计算-基于ThreadX和ARM 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号