随着微电子技术和计算机技术的飞速发展, 各种电子测量仪器在原理、功能、精度及自动化水平等方面都发生了巨大的变化, 特别是DSP技术诞生以后,电子测量技术更是迈进了一个全新的时代。近年来,DSP逐渐成为各种电子器件的基础器件,逐渐成为21世纪最具发展潜力的朝阳行业,甚至被誉为信息化数字化时代革命旗手。在电子测量技术中,频率是最基本的参数之一,它与许多电参量和非电量的测量都有着十分密切的关系。例如,许多传感器就是将一些非电量转换成频率来进行测量的,因此频率的测量就显得更为重要。数字频率计是用数字来显示被测信号频率的仪器,被测信号可以是正弦波、方波或其它周期性变化的信号。

数字频率计广泛采用了高速集成电路和大规模集成电路,使得仪器的体积更小、耗电更少、精度和可靠性更高。而传统的频率计测量误差较大,范围也较窄,因此逐渐被新型的数字频率计所代替。基于DSP的等精度频率计以其测量准确、精度高、方便、价格便宜等优势将得到广泛的应用。

我们设计的简易数字频率计在未采用任何门控器件控制的情况下,在很宽的范围内实现了等精度频率测量,0.5Hz~10MHz的范围内测量方波的最大相对误差小于2e-6,测量正弦波的最大相对误差小于3.5e-5;结果通过RS232通讯显示在计算机上,可以很方便地监测数据。

方案设计

总体介绍

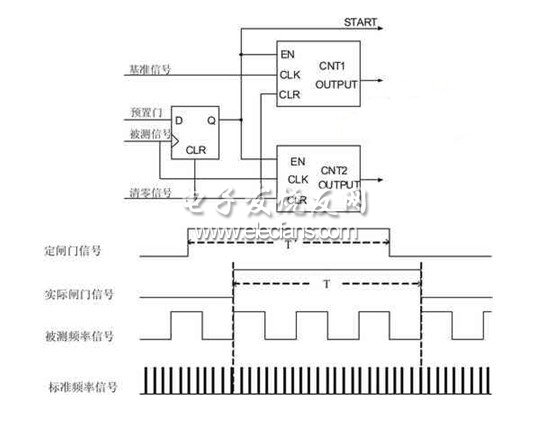

传统的等精度测频法使用门控器件产生门控信号,从而实现实际门闸信号与被测信号同步,消除对被测信号计数产生的一个脉冲的误差,其原理图如图1所示。

图1 传统的等精度测量原理

由硬件控制计数的门闸时间,当预置们信号(即定闸门信号)为高电平时,基准信号计数器CNT1和被测信号计数器CNT2并不启动,而是等被测信号的上升沿来到时才同时开始计数;当预置们信号为低电平时,两个计数器并不马上关闭,同样要等到被测信号上升沿来到后再关闭;于是,实际闸门时间就是被测信号周期的整数倍,从而实现了闸门与被测信号的同步。但是,实际的门闸时间并不固定,与被测信号的频率有关。此外,无论是采用计数器还是单片机,在实现等精度测量时总是离不开门控器件。

本设计基于DSP丰富的软件资源,经过判断和处理,完成了对被测信号频率的等精度测量。硬件上无需任何门控器件,简化了电路。系统框图如图2所示,信号处理部分以TMS320F2812 DSP芯片作为控制和测量的核心;信号调理部分主要是完成对信号的放大、整形和限幅;标准频率信号由30MHz有源晶振产生,作为高频标准填充脉冲;通过DSP的SCI模块与上位机实现通信,结果显示在上位机上。

图2 系统框图

频率/周期测量

在对被测信号频率和周期的测量中,等精度测量是基于DSP比较匹配时T1PWM引脚输出电平的跳变作为门闸信号的开启和关闭,由于比较匹配发生在被测信号的上升沿,从而实现了门闸时间与被测信号的同步。原理图如图3所示。

图3 本等精度频率测量原理

通用定时器T1时钟输入选择外部定时器时钟,此处用调理后的被测信号作为定时器T1的时钟输入,定时器T2时钟输入选择内部CPU时钟,用来产生高频标准填充脉冲。F2812片上EVA中通用定时器T1在发生比较匹配事件时,其比较输出引脚T1CMP输出信号会自动改变电平状态,产生PWM波。捕获单元CAP1设置为上升沿捕获,T1PWM输出的PWM波上升沿被CAP1捕获到,读取此时定时器T2的计数值,同理在下一次比较匹配时再次读取定时器T2的计数值。通过两次T2CNT值的相减,即可获得该门闸时间内标准填充脉冲的个数,然后求出被测信号频率。

基于DSP比较匹配时T1PWM引脚输出电平的跳变作为门闸信号的开启和关闭,由于比较匹配发生在被测信号的上升沿,从而实现了门闸时间与被测信号的同步。两个相邻的比较匹配产生的PWM波的上升沿分别作为门闸信号的开启和关闭信号,其中被测信号的个数为整数,并且是由我们自己任意设定的。定时器T2时钟输入选择内部CPU时钟,用来产生标准填充脉冲。设定捕获单元CAP1为上升沿捕获,当其捕获到上升沿时读取堆栈CAPFIFO内的值,在下一次捕获到时再读堆栈内的值,计算出标准填充脉冲的个数Ny,保证Ny的个数不小于一定的值,即可保证门闸时间大于一定的值。假设现在希望一个门闸时间内高频填充脉冲的总数不小于n,当Ny>n时,就增大定时器T1的定时周期,即增大定时器T1周期寄存器TIPR的值。存在公式T1PR+1=n/Ny,由于n/Ny不一定为整数,假a 周期测量与频率测量的基本原理完全相同,测出信号频率,根据公T=1/f即可得出被测信号的周期。 误差分析 |d|≤1/Ny 显然,测量精度仅仅与Ny有关,只要Ny值足够大,就能保证精度。 硬件设计 如图4所示,将被测信号经过高速运放OPA2690进行放大,在经过高速比较器TL3016进行整形[3],由于比较器在对低频正弦波信号进行整形时,输出波形的边沿有比较严重的抖动,影响测量。解决办法是对比较器加入正反馈,加速信号边沿,同时形成滞环,可有效消除抖动。整形后的信号经过高速施密特触发SN74LVC1G14进行限幅和进一步整形。测量部分主要使用DSP2812芯片上定时器T1的时钟输入引脚TCLKINA、定时器T1的比较输出引脚T1PWM和捕获单元CAP1的输入引脚CAP1,即可完成频率测量。通讯部分选择MAX3221作为RS-232电平转换器件,通过9芯标准RS-232口与上位机进行串行通信。主要使用了DSP的串行通信发送引脚SCIRXD和串行通信接收引脚SCITXD。 软件设计 软件设计部分主要包括以下四部分: ·初始化:对变量参数、系统时钟、PIE、EV、Flash、GPIO等进行配置。 图5为测频率、周期软件流程图,图6为定时器2的溢出中断流程图。 图5 测频率、周期流程图 图6 定时器T2溢出中断流程图 在该部分初始化时,要进行以下配置:通用定时器T1时钟输入为外部定时器时钟,通用定时器T2时钟输入为内部时钟输入,用来对标准脉冲进行计数,该标准脉冲由外部30MHz的有源晶振提供;捕获单元1设置为上升沿捕获,用来捕获T1PWM引脚输出PWM波的上升沿,在每次比较匹配时读取定时器T2的计数值T2CNT,该值保存在CAP1FIFO内。初始化时要将捕获单元1的状态寄存器中的FIFO堆栈状态设置成空堆栈;将定时器T1的定时周期设置为4个被测信号的周期长度,通过测得的定时器T1的一个定时周期内的标准脉冲的个数,计算出被测信号频率,然后对被测信号进行分段,分别为低频段(小于46.875Hz),中频段(大于46.875Hz,小于2343.75KHz),以及高频段(大于2343.75 KHz),其中分段的依据是定时器的计数饱和值为65536和计数个数应大于等于1。若信号频率为中高频段则重新配置定时器T1,定时器T2的寄存器,来改变定时周期以及每个门闸时间内的高频填充脉冲的个数。在定时器T1的下一个定时周期内计算出频率和周期。另外,定时器T2的溢出次数要在第一次发生比较匹配时清零,而是否是第一次发生比较匹配则通过设置一个标志来判断。当溢出次数清零后才开始记溢出次数,直到第二次发生比较匹配。 下一步改进意见 该方法的测量误差主要来自硬件部分,整形电路的优劣直接关系到测量精度的高低。所以我们下一步的工作就是改进整形电路的整形效果和抗干扰性能,尽最大可能减小信号整形带来的误差。 由于DSP定时器在计数时存在计数饱和的情况,因此在实现该等精度测量时存在上限,即当被测信号频率高于高频填充脉冲的频率时,该方法就不能实现等精度了。可以在该方案的基础上进行以下处理:选择定时器T1定时周期内被测信号的个数固定,可设置T1PR为65529,同时将定时器T2的时钟修改为75MHz,这样就能保证每个门闸时间内高频填充脉冲的个数,从而在对高频信号实现频率和周期测量时保证了精度。 但选择定时器T1时钟输入为外部时钟时对被测信号的输入范围存在限制,如果要进一步提高测量的信号的范围,使得范围达到上百兆或上G赫兹,可以考虑相位测量的方法,将被测信号设为360度,根据被测信号与标准信号之间的X度相位差,计算被测信号频率。

定时器T1计数的启停时间都是由该信号的上升沿触发的,在一次测量时间内对被测信号的计数无误差;在此时间内标准频率脉冲的计数个数Ny,最多相差一个脉冲,故理论误差为:

图4 硬件电路连接图

·中断模块:SCI中断和定时器T2、T3上溢中断。

·数据处理模块:分段+取算术平均值。

·输出操作模块:数据经RS-232传给上位机。

上一篇:基于ADSP-BF561的宽带信息终端设计

下一篇:基于EDA技术的FPGA设计计算机应用

推荐阅读最新更新时间:2023-10-12 20:48

电子技术综合实验指导书 (华北电力大学电子技术课程组)

电子技术综合实验指导书 (华北电力大学电子技术课程组)

京公网安备 11010802033920号

京公网安备 11010802033920号