μC/OS-II是一种代码公开、可裁剪的嵌入式实时多任务操作系统。该内核通过实现抢占式任务调度算法和多任务间通信等功能,使之具有执行效率高、实时性能优良等特点。另外,其占用空间非常小(最小可裁剪至2KB)并且具有高度可移植性,因此被广泛的应用于微处理器和微控制器上。

晶心科技 (Andes)作为亚洲首家原创性32位微处理器IP与系统芯片平台设计公司,推出的AndesCore™ N10系列产品N1033A-S, 搭配应用广泛的嵌入式实时操作系统μC/OS-II以及相关的软硬件开发资源,有效的帮助客户降低现有成本、提升系统效能、减少系统功耗,并缩短产品开发上市时程。本文将介绍如何将μC/OS-II移植到AndesCore™ N1033A-S处理器上。

1. 开发环境及处理器介绍

1.1 软/硬件开发环境

本移植过程使用的软件环境是AndeSight? v1.4集成开发套件,它是晶心科技最新推出的针对各种AndesCore?的软件集成开发环境,包括编译器、调试器、分析器以及强大的ESL工具。硬件平台采用晶心科技的FPGA评估板ADP-XC5,该评估板采用AndesCore? N1033A-S作为处理器内核,并具有丰富的片上资源。

AndesCore™ N1033A-S介绍

AndesCore™ N10系列产品N1033A-S是一款哈弗结构的32位RISC处理器内核,具有5级流水线(pipeline)及动态分支预测(Dynamic branch prediction)架构。N1033A-S新加入了最新AndeStar™ V2 指令集,把CPU效能推至1.66DMIPS/Mhz之上。同时还实现完整的Audio指令集,达到完全整合CPU与DSP功能的目标。N1033A-S还支持向量中断模式以及2D 直接内存访问(DMA)功能,更为实时信号处理添增效能。

2. μC/OS-II在N1033A-S上的可移植性分析

μC/OS-II具有高度可移植性,目前已经移植到近40多种处理器体系上,涵盖从8位到64位的各种CPU(包括DSP)。

μC/OS-II的正常运行需要处理器平台满足以下要求: 1)处理器的C编译器能产生可重入代码;2)用C语言就可以打开和关闭中断;3)处理器支持中断,并且能产生定时中断;4)处理器支持能够容纳一定量数据的硬件堆栈;5)处理器有将堆栈指针和其它CPU寄存器读出和存储到堆栈或内存中的指令。

AndesCore? N1033A-S内部提供了32个通用寄存器,其中R31被用来做专门的堆栈指针。32根地址线最多可访问4GB存储单元,因此只要系统RAM空间允许,堆栈空间理论不会产生限制。N1033A-S处理器提供的AndeStar? V2指令集包含了丰富且十分高效的对堆栈进行操作的指令。例如指令SMW(store multiple word)可实现仅使用一条指令将多个寄存器的值存储到堆栈中并同时更新堆栈指针位置,而且还能很好的处理地址非对齐字的存取。N1033A-S支持中断并能产生定时器中断,处理器中的PSW(Processor Status Word)寄存器中包含一个全局中断禁止位GIE,控制它便可实现打开和关闭中断。此外,AndeSight?集成开发环境中内置的编译器可以产生可重入代码,并且支持内联汇编,C环境中可以任意进行开关中断的操作。综上所述,μC/OS-II完全可以移植到N1033A-S上运行。

3. 移植步骤

为了方便移植,大部分的μC/OS-II代码是用C语言写的,用户只需要用C语言和汇编语言写一些与处理器相关的代码就可以实现移植。这部分工作的内容包括:一个完成基本设置的头文件os_cpu.h、一个与处理器相关的汇编文件os_cpu_a.S 和一个与操作系统相关的C代码文件os_cpu_c.c.

3.1在os_cpu.h中完成基本的配置和定义

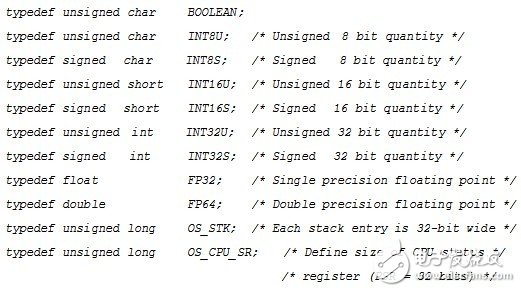

3.1.1. 定义与处理器相关的数据类型

为保证可移植性,μC/OS-II没有直接使用C语言中的short、int和long等数据类型的定义,因为不同的处理器有不同的字长。对于N1033A-S这样的32位处理器,其数据类型定义实现如下:

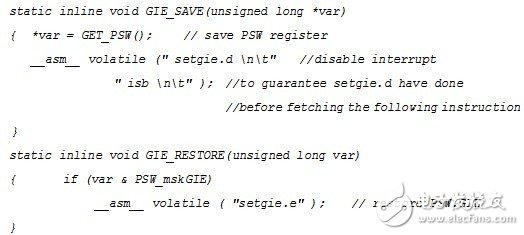

3.1.2. 定义中断禁止/允许宏

做为实时内核,μC/OS-II需要先禁止中断再访问代码临界区,并且在访问完毕后重新允许中断。 μC/OS-II定义了两个宏来禁止和允许中断:OS_ENTER_CRITICAL()和OS_EXIT_CRITICAL()。在N1033A-S处理器上的实现代码如下

![]()

GIE_SAVE 和GIE_RESTORE的实现如下:

中断禁止时间是判断系统实时性的重要指标之一。中断禁止时间能否达到最短,不仅与操作系统的设计有关,还依赖于处理器结构和编译器产生的代码质量。从上面的实现代码看到,由于Andes处理器提供了setgie.d和setgie.e两条直接控制中断的开关的指令,整个禁止/允许中断的过程经过编译器产生的机器码只有3/2条,最大限度地减小了中断禁止时间。

3.1.3. 定义栈增长方向

μC/OS-II使用结构常量OS_STK_GROWTH来指定堆栈的增长方式,设置为0表示堆栈从下往上增长,设置为1表示从上往下增长。这里我们定义成后者,即堆栈的增长方向是从内存高地址向低地址方向递减并且堆栈指针总是指向栈顶数据:

![]()

3.1.4.定义OS_TASK_SW()宏

OS_TASK_SW()是一个宏,它在μC/OS-Ⅱ从低优先级任务切换到最高优先级任务时被调用的。任务切换只是简单的将处理器寄存器保存到将被挂起的任务的堆栈中,并且将更高优先级的任务从堆栈中恢复出来。可采用两种方式定义这个宏,使用软中断将中断向量指向OSCtxSW()函数;或者直接调用OSCtxSW()函数,这里我们采用后者(OSCtxSW()函数的实现将在后面介绍):

![]()

3.2处理器相关部分汇编实现

μC/OS-Ⅱ的移植需要用户编写三个最基本的汇编语言函数:OSStartHighRdy(),OSCtxSw(),OSIntCtxSw()。它们会共用一些代码,为了方便阅读将它们写在同一个汇编文件os_cpu_a.S中。

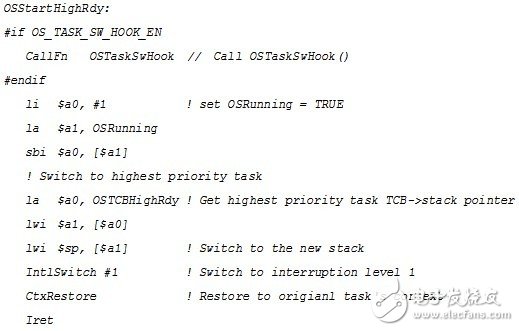

3.2.1 OSStartHighRdy():运行优先级最高的就绪任务。

OSStartHighRdy()函数是在OSStart()多任务启动之后,负责从最高优先级任务的TCB控制块中获得该任务的堆栈指针SP,并通过SP恢复CPU现场以启动最高优先级的任务执行。另外OSStartHighRdy()还必须在最高优先级任务恢复之前和调用OSTaskSwHook()之后设置OSRunning为TRUE.其实现代码如下:

3.2.2 OSCtxSw()和OSIntCtxSw()

OSCtxSw()是任务优先级切换函数,它的作用是先将当前任务的CPU现场保存到该任务的堆栈中,然后获得最高优先级任务的堆栈指针,并从该堆栈中恢复此任务的CPU现场,使之继续执行,该函数就完成了一次任务切换。

OSIntCtxSw()是中断级的任务切换函数。由于中断可能会使更高优先级的任务进入就绪态,因此为了让更高优先级的任务能立即运行,在中断服务子程序最后会调用OSIntCtxSw()做任务切换。这样做能够尽快的让高优先级的任务得到相应的处理,保证系统的实时性能。

OSCtxSw()和OSIntCtxSw()都是用于任务切换的函数,其区别在于,在 OSIntCtxSw()中无需再保存处理器寄存器,因为在OSIntCtxSw()之前已发生中断,所以可以保证所有的处理器寄存器都被正确地保存到了被中断的任务的堆栈之中。OSCtxSw()和OSIntCtxSw()实现代码如下:

N1033A-S处理器定义了四级(0-3)中断,在各级中断的转换时需要保存当前中断层级的寄存器。调用OSCtxSw()时,中断将由0级(即没有中断)转到1级,所以需要将第0级的寄存器PSW和PC保存到第1级的寄存器IPSW和IPC中。 CtxSave和CtxRestore两个宏用来保存和恢复任务上下文。需要保存或恢复的寄存器包括32个通用寄存器(R0-R31)的值、程序计数器(PC)的值以及处理器状态字寄存器(PSW)的值。宏IntlSwitch n通过修改PSW.INIT的值来切换中断层级。CtxSave和IntlSwitch的汇编实现如下(由于CtxRestore与CtxSave过程类似,这里不做赘述):

3.3 移植C语言编写的几个与操作系统相关的函数

μC/OS-Ⅱ有六个与CPU相关的函数:OSTaskStkInit()、 OSTaskCreateHook()、OSTaskDelHook()、OSTaskSwHook()、OSTaskStatHook()、 OSTimeTickHook(),它们被定义在ucos_ii.h中。其中唯一必须移植的函数是任务堆栈初始化函数OSTaskStkInit(),其它五个函数必须得声明但没必要包含代码。因此这里我们只介绍OSTaskStkInit(),其代码的实现如下:

OSTaskStkInit()在任务创建时被调用,负责初始化任务的堆栈结构并返回新堆栈的指针,使得堆栈看起来就像刚发生过中断并将所有的寄存器保存到堆栈中的情形一样。除了要保存任务的地址、变量的指针以及处理器状态字的值外,Andes N1033A-S处理器还要求用户保存所有32个通用寄存器(R0-R31)、四个用户寄存器(d0.hi, d0.lo, d1.hi, d1.lo)。还有一点需要注意,在N1033A-S处理器中,堆栈指针的地址必须满足8Byte对齐,程序最后一段逻辑即将堆栈指针调整到正确的位置,这一点在编写其他代码例如在宏CtxSave中同样需要注意。

4. 结语

基于AndesStar?架构的优势,可以很容易的实现μC/OS-Ⅱ在N1033A-S处理器上的移植。不仅μC/OS-Ⅱ,其它嵌入式操作系统也可以很方便地移植到AndesCore?相应的处理器上,例如Nuclues、FreeRTOS以及Contiki。

晶心科技利用 AndesCore? N1033A-S高效能的 Audio ISA 和 FPGA开发平台弹性的设计架构,基于各种RTOS,为客户提供了的丰富的软件资源(中间件、优化的函数库、应用实例等)以及完整的多媒体语音解决方案,从而帮助客户更快地在Andes平台上进行产品开发。

上一篇:基于MCF52235 的RFID 通用开发平台设计

下一篇:MCU典型应用设计:STM32-F2在工厂自动化中的应用

推荐阅读最新更新时间:2023-10-12 20:49

- MPS EMI 知识充电节盛大开启!赚积分赢好礼!

- 下载有礼|西北模电王《新概念模拟电路》全五册

- Microchip 有奖直播|满足汽车电池管理系统 (BMS) 不断发展的安全标准

- 直播已结束|TI 嵌入式直播周带您直击工业应用

- Microchip 有奖直播|满足汽车电池管理系统 (BMS) 不断发展的安全标准

- 电阻哪个强?看Vishay演示视频 抢楼发言赢好礼

- ADI有奖直播:储能系统助力电动汽车快充站的建设 8月31日上午10:00-11:30 为您揭晓!

- 零起点入门,带你动手做AVR开发板

- ADI学霸型讲师又来了,探讨MEMS传感器和工业设备的故障监测

- 赞一赞我国的青年:专访TI杯2019年国赛9支优秀队伍

【用户手册】带+STM32MP157+MPU+的评估板

【用户手册】带+STM32MP157+MPU+的评估板 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号