四十多年来,PLC已成为实现工业控制的中坚力量。它的功能不断完善,应用领域不断扩大,对于工业控制技术的进步与社会发展所发挥的作用无可估量。PLC以它的高可靠性和易操作性,主导了工控行业数十年。PLC虽然有着它固有的优势,但面对客户需求的不断变化,PLC要想生存,就必须突破传统模式,积极求新求变以适应新的市场发展。而具有低成本优势的嵌入式PLC,正好能够满足这一需求。所谓嵌入式PLC 是指采用SoC嵌入式片上系统芯片和嵌入式实时操作系统实现PLC功能,并能用IEC61131-3的标准编程语言编程的PLC.随着高性能的ARM 嵌入式微处理器的发展,笔者设计了新一代微型嵌入式PLC.本文介绍了嵌入式PLC的体系结构,包含其硬件设计和软件设计方案。

1 嵌入式PLC的硬件结构设计

1.1 微控制器芯片的选取

CPU是PLC的核心,它能够识别用户按照特定的格式输入的各种指令,并按照指令的规定,根据当前的现场I/O信号的状态,发出相应的控制指令,完成预定的控制任务。本设计选用的是Philips公司生产的LPC2294微控制器。LPC2294是一款基于32位ARM7TDMI-S,并支持实时仿真和跟踪的CPU芯片,它带有256kB嵌入的高速Flash存储器,16kB 片内SRAM.LPC2294采用144脚封装、具有极低的功耗以及多达112个通用I/O 口,9个边沿或电平触发的外部中断引脚,最大为60MHz的工作晶振,多个32位定时器,PWM 单元,实时时钟和看门狗,转换时间低至2.44μs的8通道10位ADC、4 路高级CAN 接口, 另外具有2 路UART(16C550),高速I2 C (400kbit/s)及2路SPI总线。LPC2294丰富的硬件资源和完善的功能使这款微控制器特别适用于汽车、工业控制应用以及医疗系统和容错维护总线等场合。

1.2 硬件系统的整体结构

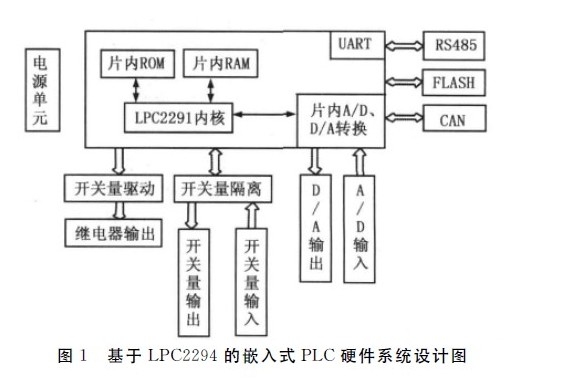

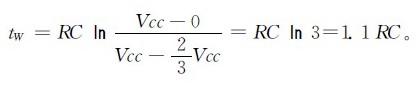

本系统以ARM 芯片LPC2294为CPU,设计为14路PNP型输入、10路继电器输出的基本模式。硬件总体结构包括:

电源及复位模块、ARM 微控制器、Flash存储器扩展模块、开关量输入输出模块、模拟量输入输出模块、RS485接口及CAN接口通信模块等。系统的结构如图1所示。

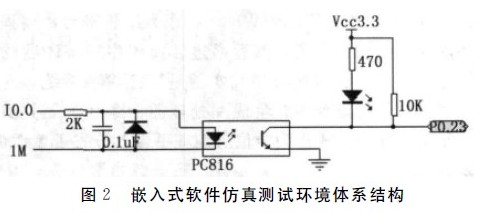

1.2.1 开关量输入输出接口电路

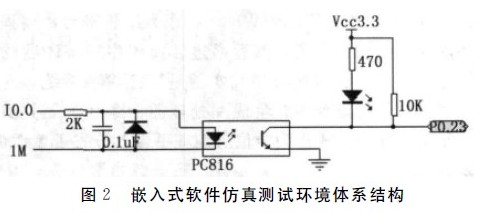

图2所示为一路开关量输入图。此部分电路前端为R、C组成的一阶滤波电路,防止外部干扰信号进入系统中。输入端外接的输入控制开关信号(直流24V)通过输入点10.0经限流电阻输入到光电耦合器(PC816)的输入端,M 为输入点10.0~10.7的公共输入端。因P0.23口被设置为输入模式且口线内部无上拉电阻,所以需要外接上拉电阻,防止口线悬空。当10.0输入端为24V时,光电耦合器中的光敏二极管导通,光敏晶体管输出端被拉为低电平,指示该路输入状态的LED被点亮,P0.23被置为低电平。当CPU访问该路信号时,将该输入点对应的输入过程映像寄存器的值置为 1.10.0输入端为0V时,P0.23为高电平,当CPU访问该路信号时,则将该输入点对应的输入过程映像寄存器的值置为0.其余各个输入点所对应的电路及工作原理均相同。

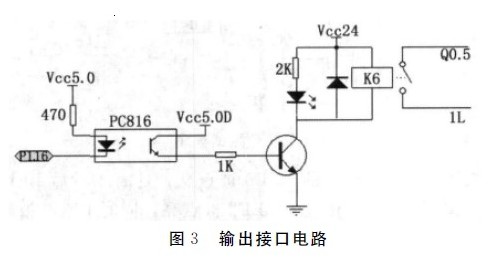

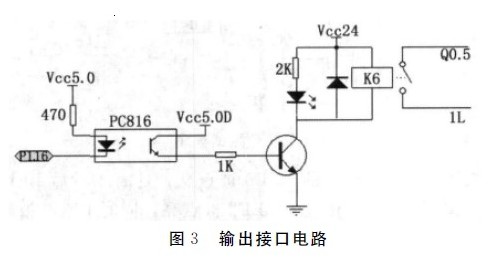

图3所示为继电器输出模块图,图中并联在继电器线圈两端的二极管这里起续流作用。该模块的工作原理如下:当内部输出过程映像寄存器为1时,LPC2294端口P1.16输出0,光敏晶体管导通,继电器线圈得电,输出点接通;反之当内部输出过程映像寄存器为0时,端口P1.16输出1,继电器线圈失电,输出点断开。

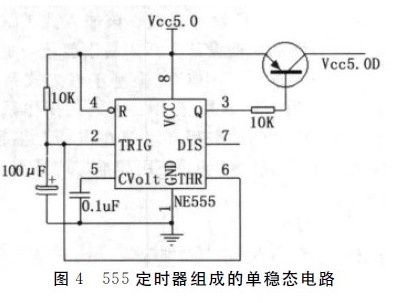

需要注意的是,当LPC2294的GPIO 口初上电时,其输出端口(如本图中的P1.16)的电压不稳定,这样易导致外部继电器误动作而引起外部设备工作不稳定。为此,我们设计了图4电路用来提高继电器输出的稳定性。

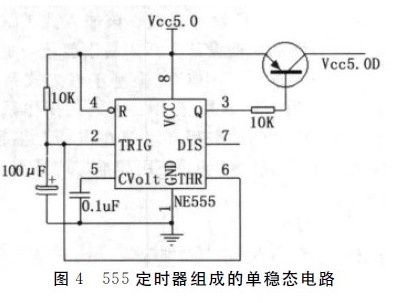

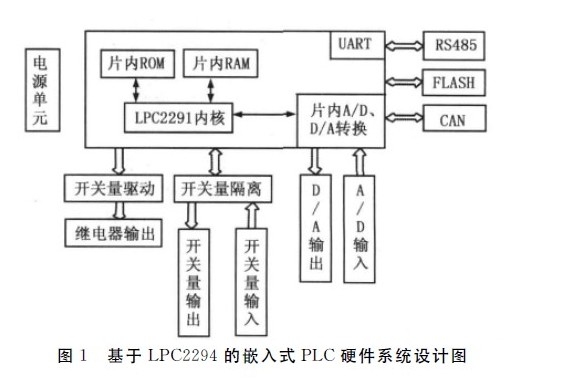

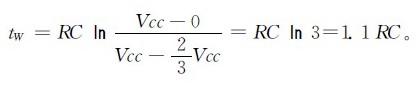

这是一个由NE555 定时器组成的单稳态电路,其中VCC5.0D端接图3中光电耦合器的集电极。其工作原理为:系统上电初始,2、6管脚电平不能突变,保持为低电平。分析 NE555的内部电路可知,此时输出端3管脚输出高电平,电路开始对R、C电路进行充电,随着时间的推移,管脚2、6的电平不断升高,当升至23VCC 时,输出端3管脚将翻转至低电平,使三极管导通,VCC5.0D输出5V.这样,系统上电后经过一段时间,I/O口的电平稳定下来之后,光电耦合器才得电开始工作。暂稳态的持续时间tW取决于外接电阻R 和电容C的大小。tW等于电容电压在充电过程中从0上升到23VCC所需要的时间,即

1.2.2 模拟量输入电路设计

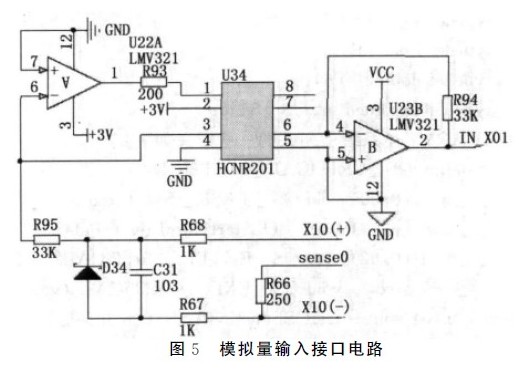

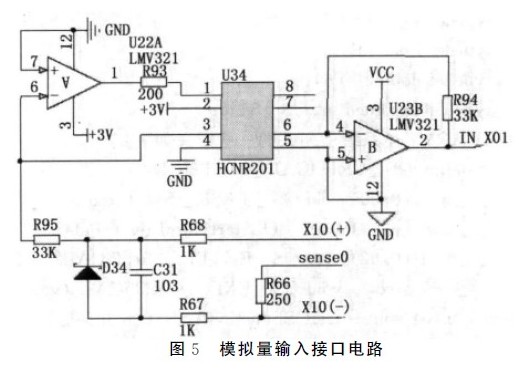

先通过电阻R66,将现场传感器输出的电流信号转换为0~5V电压信号进行采集。考虑到抗干扰及对微处理器电路的保护,在转换电路的输出端加了线性光耦HCNR201.硬件电路如图5所示。

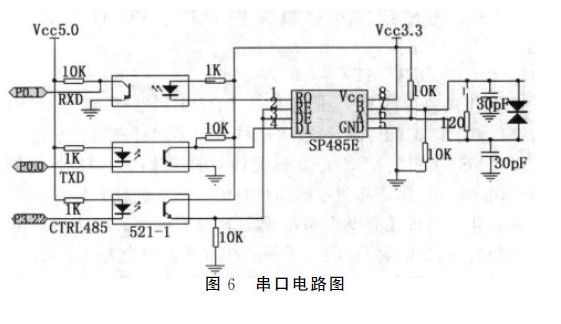

1.2.3 串行通讯接口电路设计

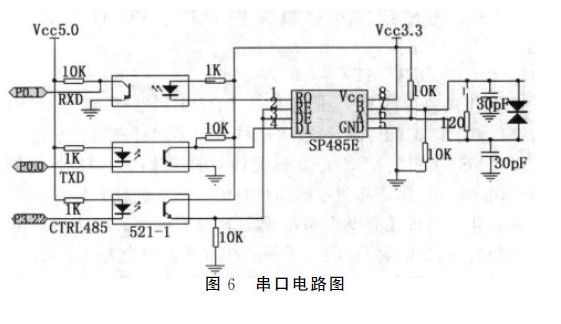

为了能与其它工业控制产品兼容,我们设计时采用了RS-485接口标准。为了将TTL电平转换成 RS485电平,选用了SP485E 收发器。SP485E 芯片的数据传输速率可高达10Mbps,其最大的特点是在为发送器输出和接收器输入管脚提供了ESD保护电路。接口电路如图6所示。

关键字:LPC2294 处理器 嵌入式 PLC

编辑:神话 引用地址:基于LPC2294处理器的嵌入式PLC的设计(一)

推荐阅读最新更新时间:2023-10-12 20:49

博通推出业界首款28nm异构知识型处理器

博通( Broadcom )公司近日推出28nm异构处理器,产品系列为 NLA12000 ,目前以提供样片。新系列的处理器为异构 “知识型处理器( Knowledge-based processor ,简称 KBP )”可满足 3G/4G 移动基础设施、数据中心及企业环境对扩展性和效率的要求,与同类解决方案相比,性能提高多达 24 倍。

托管式服务持续加速增长以及软件定义网络( SDN )、 OpenFlow 等新趋势的出现,导致需要在网络中增强分类、转发及安全处理能力。此外,随着移动互联网的发展,路由协议正在从 IPv4 向 IPv6 迁移,因此面向第二层至第四层处理的知识型处理器的协议表项增加了 4 倍。总之,这些因素推

[网络通信]

ARM王骏超: 64位处理器是高阶手机的下一波趋势

随着苹果手机iphone5s开始采用64位架构处理器,有关64位处理器的讨论日趋激烈,其他厂商也纷纷跟进,难道手机处理器多 核发展趋势走错了道路?作为大赢家的ARM公司如何看待手机处理器未来发展趋势?近日,有媒体采访了ARM中国区移动市场经理王骏超,他就大家关注的问题 进行了答复。 问:目前ARM 64位处理器已经有多少家厂商获得授权?都是哪些厂商? 王骏超:目前获得64位处理器授权(包括V8架构授权)的厂商包括AMD,Applied Micro,Broadcom,Calxeda,CAVIUM,Freescale,HiSilicon/Huawei,LG,Marvell,Nvidia,Qualcomm,S

[手机便携]

C&D的VRM模块满足AMD K8处理器电源规范

C&D Technologies公司日前发布新款系列稳压模块(VRM),该产品具有高效、大电流及快速瞬态负载响应等特性,符合AMD64处理器的电源规范。

其中80A的VRK81B080CS和VRK81B080CU高度分别为2U和1U,100A的VRK81B100TH可水平安装,高度为0.415英寸。这三种模块的效率均在85%以上,并能够通过降低功耗简化系统的温度管理。

以上产品均符合RoHS标准,可为最新的AMD Opteron处理器供电,适合于专业数字媒体等高计算强度的应用。Opteron处理器要求VRM模块能够满足快速负载瞬态的需求(100A/μs),并提供多种集成监控和保护性能,如电源正常指示器、过流闭锁、短路保

[新品]

SIGMA 1400 万像素的新型SD14数码相机将采用ADI BLACKFIN处理器

——Blackfin处理器将为从传感器到存储卡的图像流水线的每幅图像的每个像素进行200次计算

中国,北京—— 美国模拟器件公司(纽约证券交易所:ADI)今天宣布:Sigma公司SD14数码单镜反光(SLR)相机将采用ADI公司的 Blackfin处理器。SD14相机充分利用Foveon X3传感器独一无二的直接成像技术以及ADSP-BF561 Blackfin处理器的高性能,可以逐级重现高清晰度图像,因为SD14能够为图像中的每一个像素直接捕获100%红、绿、蓝 (RGB)三原色光,让原色彩无一遗漏全面显现。

“SD14相机通过捕获每个像素的真实色彩,可以告诉每幅图像的‘全部真相’,” Sigma公司首席运营官Kaz

[焦点新闻]

7nm处理器产能现在成为问题了吗

今天下午, AMD 在北京举行了主题为“万众一芯 出7制胜”的第二届大中华区合作伙伴峰会。在发布会之后,AMD全球副总裁、服务器业务总经理Scott Aylor接受了媒体采访。 在采访中,快科技提了两个问题,一个是有关AMD 7nm Zen2架构处理器频率的,在32nm SOI工艺下AMD曾经实现了 5G Hz的高频,目前7nm工艺下频率还有所不如,AMD是如何平衡频率与核心的设计呢? Scott Aylor表示AMD承认处理器单核性能非常重要,这也是AMD处理器追求的目标之一,但不能单纯比较频率变化,多年来AMD的处理器一直在提升架构性能,比如设计了全新的缓存系统,分支预测单元等等,单核性能是不断提升的。 第二个问题与台积

[半导体设计/制造]

8核手机处理器技术评析

核心数的增加,不代表运算效能也线性增加,而是逐渐趋缓的走势,在相同时脉、相同制程、相同微架构的电路设计等前提下,若单核芯片的效能为100%,则双核芯片的效能不会是200%,而是低于200%,原因在于2个核心必须对运算工作进行沟通协调,协调即会造成效能损耗。 若要减少核心间的协调耗损,则需要传输量大、路由绕径智能化的芯片内汇流排(On-Chip Bus),好的汇流排设计可以减少损耗,如双核可达170%效能,协调耗损为30%,差的汇流排则高损耗,双核仅有140%效能。 随着芯片内核数的增加,每增加1个核所能带来的边际效能将递减,假若单核为100%效能,追加第2核可再加70%效能,但再追加第3核恐仅再加60%,第4核更只有50%,

[手机便携]

看得懂电气图、却看不懂PLC梯形图?

很多人说PLC难,就算有电工基础,想学会也很难!但是真的如此吗?有电工基础又该如何快速学会PLC呢?今天咱们一起来看看电工图如何快速转化成PLC梯形图,以三相感应电动机故障警报控制电路为例子说明: 传统电工图 (1)当电源正常时,仅绿灯gl亮,电动机不动作。 (2)当按下启动按钮pb1,电磁接触器mc动作,电动机立即运转,指示灯rl亮,绿灯gl熄。 (3)当按下停止按钮pb2,电磁接触器mc断电,电动机停止运转,指示灯rl熄,绿灯gl亮。 PLC梯形图 那么如何从传统电工图转换为梯形图呢?一起来看看吧: (1)将电工图中控制电路直接转成对应阶梯图。首先重新绘制电工图,将图中接点与输出线圈位置适度变更,以符合PLC阶梯图的

[嵌入式]

嵌入式C编程与Atmel AVR_(美国)

嵌入式C编程与Atmel AVR_(美国) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号