一些法规或标准适用于现代化飞机中的几乎每个螺栓、面板和电线。一些最严苛的法规与电气线路互连系统 (EWIS) 有关。如果在飞机设计项目开始时未能预测到这些一致性要求,那么可能会对成本产生很大的影响。通过在项目初期将 EWIS 法规纳入考虑范围并以此做出英明的设计决策,可以避免后期的大部分设计修改工作。推迟一致性检查可能意味着需要做出代价最高昂的更改。

EWIS现在是《联邦航空条例》(FAR) 第25部规定的一部分,也因此成为所有新商用飞机的一项认证条件。“EWIS 思维”已经延伸到旋翼机和防卫平台等其他工业。我们不妨来研究一些主要的关注点,并探讨商用现货 (COTS) 电子设计自动化工具帮助设计师实现 EWIS 一致性的方式。

命名规范

FAR 25.1711 描述了 EWIS 组件必须带有的认证和信息类型,包括组件的功能、冗余考虑事项、隔离要求和唯一性。在飞机中,每个组件都有且只有一个相应的标识,在飞机的整个生命周期都必须遵守这项规则。

举例来说,假设电线名称由线束标识、隔离类别、该线束特定的计数和电线规格组成,那么电线编号为 W238- FC1-101-22。按照唯一性要求,线束或车辆其它地方不能出现另一根编号为 W238-FC1-101-22 的电线。如今,飞机中众多的 EWIS 组件、不同的飞机配置和生命周期变更管理挑战使这项工作变得十分困难且容易出错。这就需要系统化和自动化程度更高的方法。

一个简单的解决办法是在设计周期的不同阶段以电子方式检查组件名称是否重复。但这可能使错误的漪涟通过流程扩散并影响飞机其它地方的连接或者归档。。

与之不同的是,先进的 COTS 工具采用“正确构建”法。该软件从源头上杜绝错误的发生,而不是等用户出错后依靠后续检查来找出问题所在。当设计人员创建设计数据时,COTS 工具运用电线命名规则确保达到 EWIS 目标,从而自动符合 FAR 25.1711 的要求。

安全问题

FAR Part 25.1709 侧重于 EWIS 系统的安全性。这些要求确保灾难性的失效几乎是不可能的,也不会由一个小的失效而导致,同时每种可能的发生危险故障的概率也几近为零。

失效树分析法 (FTA) 及失效模式与影响分析法 (FMEA) 对这里会用到的虚拟建模功能进行了说明。进行这类分析的软件工具需要运用到电流的设计数据,而根据变化随时拿出应对之策也是一个巨大挑战。电气设计师要严格遵守交付时间,尽量让这些数据更加完善,因为安全工程师没有时间在进行每项分析时都重新输入新的数据。

解决这一难题的最好方法就是采用整套符合设计环境需求的安全分析工具。这样便于重复使用信息,并将设计数据运用到服务于更大项目的应用中。理想的情况是,安全分析工具不仅提供了有关安全实施的“数据”,还提供了一种快速评估分析效果并帮助设计工程师有??效进行更改的方法。

最近,大多数分析工具已经给出了文本形式的分析结果,安全工程师要根据这些结果找出最关键的问题。但现代的 COTS 设计和分析工具集已经与一个无缝的环境形成了整体。最新的电气设计数据可重复用于多种用途,包括以设计数据的当前状态为对象的 EWIS 安全一致性分析。此外这些数据还能以图形化的方式指出问题可能出在哪。

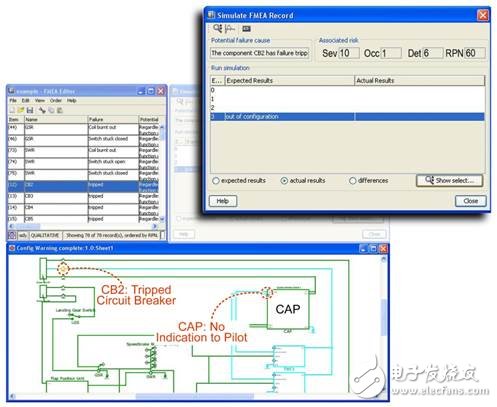

图1显示出明导 Capital Design 套件的若干相关分析窗口,标有对图形显示能力的注解。

图1 - FMEA 结果的图形显示

这个例子显示出按风险系数 (RPN) 排列的各种故障。RPN 值为60,表示这个错误要引起注意;故障会导致示警面板 (CAP) 无法显示驾驶舱内的信息。

从这张示意图的高亮部分可以直接看到设计中的错误在哪,以及所带来的影响。电路中的绿线表示通电,而蓝线表示电路中断。工程师可以很容易地看到,断路器故障导致为特定设备供电的电流中断。

执行规则

EWIS 规定包括一系列能够表达要求的规则。例如。每个组件必须“…在种类和设计上符合其基本功能”;“独立电源绝不能共用接地线。”这类指令可在 COTS 工具集内通过捕捉类似设计规则和约束的核心要求进行满足。

设计工具可强制执行规则和约束从而协助和自动化大部分决策。这种方法具有很明显的优势:

工具集可以迅速、自动做出决策

在很多类似决策点都能给出一致的结果

对于每个决策,都能很容易评估相应的跨域影响

促成做出决策的每个因素都具备固有的可追溯性,可以知道某个决策是如何得出的。

数字辅助决策过程的基本构件是约束的概念。约束决定了简单的结构;例如,“IF 《signal = AC》, THEN 《do not route with flight controls》。”这个例子就限制了携带信号的电线被布线到附近,因为这可能会造成危险的相互影响。

基本上,约束会以能够在算法上决定的形式捕捉设计和/或法规意图。使用约束可以大幅缩短获得已定义设计信息的核心集所需的时间。

规则,也称为约束规则集,只是为了某个特定目的而组合到一起的约束集。在线束构建早期阶段,设计人员会在 3D 模型成熟前构建一个预期线束的拓扑路线图,然后定义必要的规则集和约束。约束可确保电气组件能够自动分布在合适的区域,同时恰当地布置线路和焊接点。

这个数字化模型随后将用来评估权衡方案和尽早定义实物 EWIS 部分的特点。图2描述的是显示两个规则集和三个约束的拓扑图。

图2 -- 评估布线约束的影响

EWIS 规定不执行任何具体的解决方案,因此设计人员可以根据分析数据自由应用其判断。设计人员可探索创新的设计替代方案,前提是确保满足相关要求。

设计“域”

EWIS 规则不适用于有特定用途的解决方案,因为这些规则过于宽泛,不够具体,因此设计人员很难用这些很宽泛的规则来处理小细节。以 FAR 25.1703(4) 来看:

“安装在飞机任何部位的所有 EWIS 部件的设计和安装方式都必须遵循最小化机械牵张力的原则。”

像诸多 EWIS 规定一样,FAR 25.1703(4) 是一项跨域要求。它可能会出现与域的设计、验证和安装等——所有这些都是相关联且同步的——相关的结果。

确定线束是否符合 EWIS 要求,需对众多因素有所了解,不仅仅是知道它是个线束这么简单。假设 MCAD 设计人员过分简单地将线束设计成直径为一定长度的管子。理论上说,这样就可以定位和布线,但却没有任何信息来指导设计人员做出有关松弛和后壳进入条件等方面的正确决策。了解线束的要素详情至关重要。

一个整体的跨域设计环境是应对这一问题的解决方案。图3是一个整体的工具集中的一部分。左边的原理图与右边的 MCAD 三维视图共用数据,这样查找原理图的特定电线时,三维图片和插入表格页也会同时突出显示。

图3:交叉查找:选中 ECAD 域的一个目标时,相应的 MCAD 等值也会突出显示。

ECAD 和 MCAD 设计领域之间的集成数据互通可将某一域的变化与所有域的“连锁反应”自动关联,大大简化设计人员的工作。

总结

EWIS 规定不仅仅针对安装和维护。如今,设计阶段也包括在内。一个完整的 COTS 设计解决方案可提供诸多功能,如跨域关联,并且有助于尽快高效地了解 EWIS 要求,从而持续应用在整个项目周期之中。

上一篇:参数不能说明一切 音频设备参数解析

下一篇:基于PIC单片机的智能化逆变电源控制系统

推荐阅读最新更新时间:2023-10-12 20:49

电路理论 (李智)

电路理论 (李智) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号