在Matlab/Simulink环境下,采用DSP Builder模块搭建FIR模型,根据FDATool工具对FIR滤波器进行了设计,然后进行系统级仿真和ModelSim功能仿真,其仿真结果表明其数字滤波器的滤波效果良好。通过SignalCompiler把模型转换成VHDL语言加入到FPGA的硬件设计中,从QuartusⅡ软件中的虚拟逻辑分析工具SignalTapⅡ中得到数字滤波器实时的结果波形图,结果符合预期。

0 引言

在信息信号处理过程中,数字滤波器是信号处理中使用最广泛的一种方法。通过滤波运算,将一组输入数据序列转变为另一组输出数据序列,从而实现时域或频域中信号属性的改变。常用的数字滤波器可分为有限脉冲响应(FIR)滤波器和无限脉冲响应(IIR)滤波器两种。其中,FIR数字滤波器具有严格的线性相位,而且非递归结构也保证了运算的稳定性。在实时性要求比较高的应用场合,采用可编程芯片FPGA加以实现,相比于DSP芯片或专用芯片的实现方法,具有高速、高精度、高灵活性的优点。本文在采取了一种基于FPGA和DSP Builder的方法设计FIR数字滤波器时,采用了层次化、模块化的设计思想,遵循DSP Builder的设计开发流程,在Matlab/Simulink 中建立模型并进行系统级仿真,再进行Verilog语言转换,ModelSim仿真验证无误后实现了FIR数字滤波器的实时测试。

1 FIR 数字滤波器的基本原理及结构

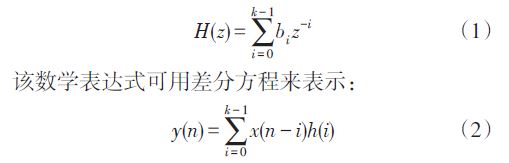

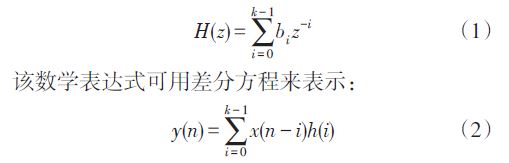

对于一个FIR滤波器系统,它的冲击响应总是有限长的,其系统函数可以记为:

式中:x(n) 是输入采样序列;h(i) 是滤波器系数;k 是滤波器阶数;y(n) 表示滤波器的输出序列。

图1为k 阶FIR数字滤波器的结构框图。

2 FIR 数字滤波器的设计流程

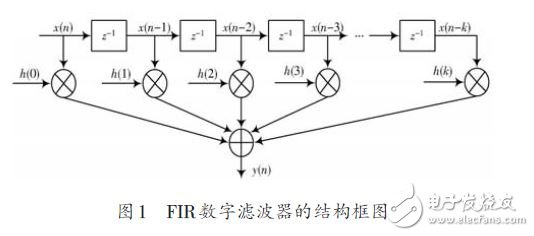

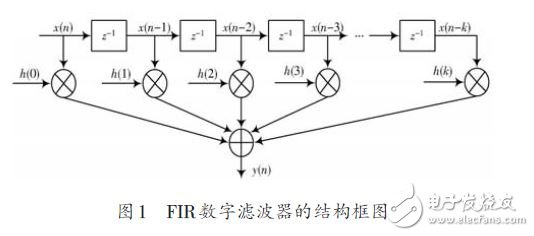

该设计流程主要涉及到Matlab/Simulink、DSPBuilder和Quartus Ⅱ等工具软件的开发设计。整个设计流程,包括从系统描述直至硬件实现,可以在一个完整的设计环境中完成,如图2所示。

(1)Matlab/Simulink 中设计输入,即在Matlab 的Simulink环境中建立一个扩展名为mdl的模型文件,用图形方式调用Altera DSP Builder 和其他Simulink库中的图形模块(Block),构成系统级或算法级设计框图(或称Simulink设计模型)。

(2)利用Simulink的图形化仿真、分析功能,分析此设计模型的正确性,完成模型仿真,也叫系统级仿真。

(3)DSP Builder设计实现的关键一步,通过Signal-Compiler把Simulink的模型文件转化成通用的硬件描述语言Verilog文件。

(4)转换好的Verilog源代码用ModelSim软件进行功能仿真,验证Verilog文件的正确性。接下来的几个步骤是对以上设计产生的Verilog的RTL代码和仿真文件在Quartus Ⅱ工具软件中进行综合、编译适配,生成扩展名为。sof的文件加载到FPGA硬件系统中。

3 FIR 数字滤波器的详细设计

3.1 FIR数字滤波器模块设计与系统级仿真

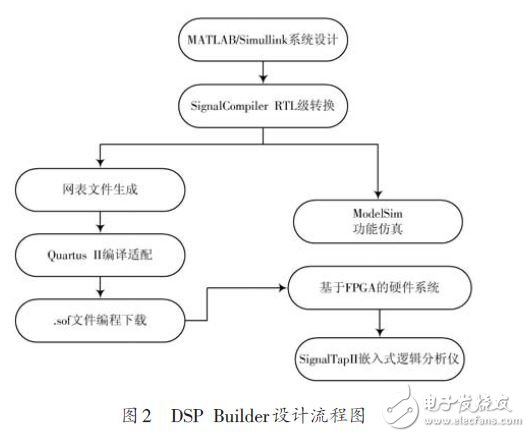

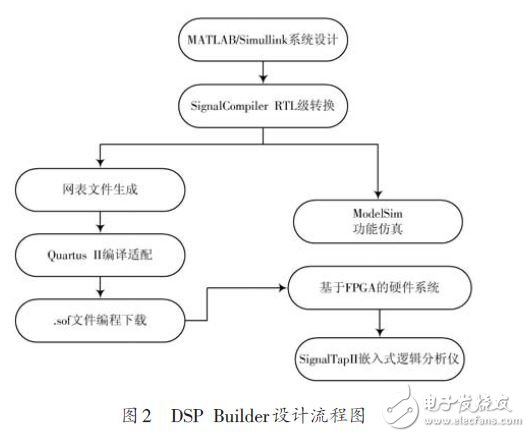

根据FIR数字滤波器的原理,在Simulink环境下搭建16阶的FIR数字滤波器结构,如图3所示。

在模型的搭建过程中,使用了两个8位的Shift Taps移位寄存器模块对输入信号进行分解,然后根据数字滤波器的原理进行算法计算。

关键字:FPGA FIR 数字滤波器

编辑:神话 引用地址:基于FPGA的FIR数字滤波器设计方案(一)

推荐阅读最新更新时间:2023-10-12 20:50

电液伺服系统控制器设计研究

0 引言 随着电液伺服控制理论的发展, 很多先进的控制策略被应用于电液伺服控制领域中。如: 文献 阐述了基本运算为不完全微分PID的滤波型二自由度控制算法, 针对飞行仿真转台用液压伺服系统的特点进行了仿真研究。文献 研究了基于RBFNN 的PID控制在电液位置伺服系统中的应用。文献 对电液位置伺服系统采用滑模变结构控制, 用最优控制理论设计滑模平面, 均取得了良好效果。但大量文献均是理论与仿真研究, 大多的工业应用仍然以模拟电路实现PID控制算法为主, 主要原因是实现这些先进的控制算法的方法目前都是由负责控制的下位机用程序实现的, 而计算机易出现死机、掉电等情况, 这使液压系统可靠性和安全性都降低。 笔者介绍了一种用基于FPGA的

[嵌入式]

XtremeDSP视频入门套件(VSK)加速FPGA上的视频

随着下一代视频压缩标准问世,行业从基本视频处理向更复杂的集成处理解决方案转移,这使得系统的要求超越了独立DSP力所能及的视频性能。FPGA以不到30美元的价格提供20GMACs以上的DSP性能,从而为成本敏感型军事、汽车、医疗、消费、工业和安全应用填补了这一空白。只有FPGA能够为整套端对端视频解决方案提供逻辑、嵌入式处理、OS支持和驱动器。

妨碍开发人员将FPGA用于视频应用的因素并非他们缺乏对FPGA性能优势的了解,而是缺乏使用其设计流程的经验,对于那些习惯于用C语言编程的传统DSP程序开发人员来说尤为如此。

开发人员可以利用FPGA的灵活性来配置针对特定应用而优化的硬件架构,以此发挥该器件的性能优势。这种灵

[模拟电子]

基于ARM平台实现数字滤波器系统的设计

引言 数字滤波器作为语音与图象处理、模式识别、雷达信号处理、频谱分析等应用中最基本的处理部件,现已成为最常用的工具之一。它既能满足滤波器对幅度和相位特性的严格要求,又能避免模拟滤波器所无法克服的电压漂移、温度漂移和噪声等问题。而对于具有线性相位特性的滤波问题,设计时一般都选择FIR滤波器。 相对于窗函数法和频率设计法,在将理想频率响应和实际频率响应之间的加权逼近误差均匀地分散到滤波器的整个通带和阻带最小化和最大误差这个意义上来说,Chebyshev逼近法可以被视为最佳的设计准则。 1设计原理 1.1 FIR数字滤波器 对于长度为N、输入为x(n)、输出为y(n)的FIR滤波器,其输出函数可用差分方程表示为: 事实上,具

[单片机]

基于FPGA和DSP的高速瞬态信号检测系统

引 言

目前国内急需一种能够对电火工品的发火过程进行实时无损耗监测的方法和手段,并根据监测结果对火工品的可靠性进行准确的判决和认证,解决科研和生产过程中的具体问题。本系统采用感应式线圈作为非接触式启爆电流的启爆装置,并采用高速A/D、FPGA、DSP等先进的集成电路实现了电火工品的无损耗检测。其主要目的是:第一,解决电火工品可靠性试验中微秒级瞬态信号的检测、处理和存储技术;第二,为可靠性试验提供一种在线的无损耗实时检测系统,以便对电火工品的发火全过程进行监测;第三,为电火工品的发火可靠性认证和评估提供真实的评价依据,减少或杜绝因拒收产品而出现经济方面的风险,同时也可减少或杜绝因错误地接收产品而出现武器装备质量方面的

[测试测量]

逻辑器件FPGA的永磁无刷直流电机控制电路

主要介绍基于现场可编程门阵列(Field Programmable Gate Array,FP-GA)及EDA方法学的永磁无刷直流电机控制系统的电子电路设计。 FPGA 是一种高密度可编程逻辑器件,其逻辑功能的实现是通过把设计生成的数据文件配置进芯片内部的静态配置数据存储器(SRAM)来完成的,具有可重复编程性,可以灵活实现各种逻辑功能。 与ASIC不同的是,PCA本身只是标准的单元阵列,没有一般IC所具有的功能,但用户可以根据需要,通过专门的布局布线工具对其内部进行重新编程,在最短的时间内设计出自己专用的集成电路,从而大大提高了产品的竞争力。由于它以纯硬件的方式进行并行处理,而且不占用CPU资源,所以可以使系统达到很高的性能。这

[电源管理]

FPGA攻城拔寨,引领视频监控应用潮流

通信领域历来是FPGA应用的传统主流市场,也是业界领先FPGA厂商倾力争夺的大市场。FPGA产业发展方兴未艾,已经由当初的与或阵列发展到多系统集成的SoC。从2009年开始,随着百万像素高清标准(720p及1080p)在视频监控领域从小众走向主流,FPGA应用迎来了又一个广阔的市场空间。

FPGA产业方兴未艾

在当前的半导体工业中,摩尔定律仍然表现出其特有的规律,厂商不断推出高制程的器件,为客户带来较高性能和成本利益。

解决与子系统衔接问题:厂商要解决FPGA与各个子系统的衔接问题。在满足了客户大规模应用FPGA的需求之后,国内厂商要考虑如何降低成本、实现差异化应用等问题。我们为客户提供了满

[模拟电子]

英特尔分拆FPGA业务,国产发展几何?

10月4日,正值假日期间,一则消息引爆了芯片圈,英特尔在其官网宣布,将剥离其可编程解决方案部门(PSG),预计将于2024年1月1日开始作为独立业务运营,预计将在发布2024年第一季度财务报告时将PSG作为一个独立的业务部门报告。在未来两到三年内,英特尔打算为PSG进一步IPO,并可能与私人投资者一起探索机会,以加速业务的增长,英特尔保留多数股权。 英特尔执行总裁Sandra Rivera将担任PSG的新任首席执行官,目前他是英特尔数据中心和人工智能集团(DCAI)的总经理。在此期间,Rivera 还将继续担任 DCAI 的职务,直到英特尔找到替代人选。 回顾2015年,英特尔斥资167亿美元收购了当时的Altera公司,

[嵌入式]

FPGA快速系统原型设计权威指南_(美国)

FPGA快速系统原型设计权威指南_(美国) 嵌入式网络那些事:LwIP协议深度剖析与实战演练

嵌入式网络那些事:LwIP协议深度剖析与实战演练

京公网安备 11010802033920号

京公网安备 11010802033920号