东芝电子元件及存储装置株式会社(“东芝”)及其制造子公司、日本半导体株式会社(“日本半导体”)的新技术是抑制热载流子注入[2]所引起的LDMOS时间衰减,从而提高了用于0.13μm模拟电源IC的N通道LDMOS[1]的可靠性。该项技术使LDMOS的寿命提高了5倍,因此大大提高了模拟电源IC[3]的寿命。

有关这一成就的细节已在5月16日于芝加哥举行的2018年功率半导体器件和IC国际研讨会(ISPSD 2018)上进行了详细报告,该研讨会是由IEEE主办的功率半导体国际会议。

物联网和电动汽车的持续发展渗透离不开低电压模拟电源IC。此外,由于车辆和工业机械都需要很长的运行时间,所以车载和工业用IC必须保持高的可靠性。目前许多半导体公司正在开发的N通道LDMOS提供了低的RON特性和高可靠性,将有望应用于电机控制IC和电源管理IC。

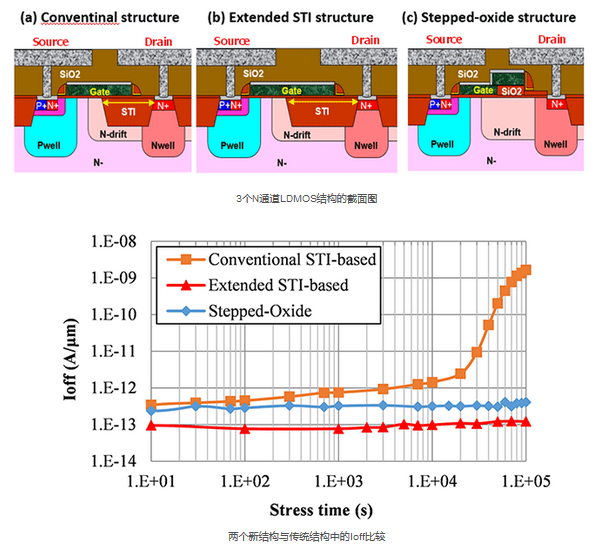

但根据东芝研究发现,N通道LDMOS有一个负面特性,即其关断状态的泄漏电流(“Ioff”)因长时间使用而急剧增加[4]。增加的IOFF将导致电路运行故障,且增加待机功耗。若能提出抑制Ioff的解决方案,将对进一步改进N沟道LDMOS至关重要。

东芝和日本半导体利用TCAD仿真和实验数据,分析了Ioff的机理,并确定了两种可抑制Ioff增加、具有卓越容差的结构。它们分别是具有扩展STI[5]的结构和阶梯式氧化物结构[6]。

第一种结构适合于LDMOS只占芯片总面积一小部分的模拟电路,比如电机控制IC,因为它不需要附加的工艺步骤但Ron仍会增加。而阶梯式氧化物结构更适用于LDMOS占芯片总面积较大部分的模拟电路,比如电机驱动器IC和DC-DC转换器,因为它即便采用附加的工艺步骤仍具有较低的Ron且具有成本效益。因此,可以在芯片设计或应用中选择合适的LDMOS结构。

这些解决方案的提出得益于东芝在晶体管设计方面的专有知识以及日本半导体在车载模拟IC业务中所积累的工艺技术。这些能力也允许公司得以确认,其通过TCAD仿真的阶梯式氧化物结构设计优化将使得LDMOS比传统LDMOS更有效地降低Ron。两家公司将继续研究Ron和可靠性,并计划在明年将这项技术引入模拟电源IC。

东芝电子元件及存储装置株式会社和日本半导体株式会社将致力于持续研发半导体工艺,提供具有高可靠性和低待机功耗的高附加值半导体。

说明

[1]LDMOS:横向双扩散MOS

[2]热载流子注入:当高能载流子注入到用于绝缘晶体管的栅极氧化膜中时所导致的晶体管特性退化,这种退化效果将因源极和漏极间电场而加速。

[3]两家公司对于寿命的定义是指“初始状态直到Ioff达到初始状态10倍时的时间长度”。

[4]东芝电子元件及存储装置株式会社通过一篇题为“热载流子引起基于STI的N通道LDMOS中关断状态泄漏电流严重退化”的论文阐述了这一现象,该论文发表于2017年国际固态器件材料会议(SSDM 2017)。

[5]STI:浅沟槽隔离,通过将绝缘子膜嵌入到浅沟槽中来隔离元件或电极。

[6]阶梯式氧化物结构:一种LDMOS结构,其中将逐步形成氧化膜。

上一篇: 美高森美和SiFive推出HiFive Unleashed扩展板 助力Linux软件和固件

下一篇:交直流混合微电网中的安全性

推荐阅读最新更新时间:2023-10-16 11:33

芯片战争 余盛 著

芯片战争 余盛 著 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号