1 引言

随着便携式消费电子需求的日益增长,低压、低功耗设计已经成为集成电路设计的研究热点之一。趋势表明[1],电压的降低给模拟电路设计带来很大挑战。就低压运放设计而言,一般传统采用互补差分对输入级以实现满幅度输入范围,然而,当电源电压低于Vt.NMOS+|Vt.PMOS|+VDS,PMOS-|VDS,PMOS|时,差分对会出现截止区,导致最小电源电压要高于2个阈值电压与2个过饱和电压之和。0.35μm工艺下Vt,NMOS的典型值为0.52V,Vt,PMOS的典型值为-0.75V,则传统结构的最小工作电压只能在1.4V左右。为了避免采用复杂工艺实现电源电压低于1V的运算放大器而增加产品成本。见文献[2-4]的电路结构采用共模电平偏移的电路结构,箝位共模电平,在标准CMOS工艺下简单地实现了低电压运算放大器。

已有文献[2]采用PMOS差分对来实现电源电压为1V的运算放大器,但由于Vt,PMOS的典型值为-0.75V,使得前置反馈电路的工作电平范围为1-0.15V,几乎涵盖整个共模电平范围,运算放大器的稳定性降低,另外,该结构下的折叠式共源共栅结构也会受体效应的影响,影响增益的恒定性。本文采用NMOS差分对结构,还对前置反馈电平偏移电路进行相应的改进,使电源电压降为0.9V的同时,提高了增益的恒定性。

2 设计的基本思路

基于前置反馈的电平偏移电路的设计如图1,Vi+,Vi-的共模电平Vi,cm低于Vref时,通过反馈电路控制电流源获得适当的电流I,Vin+,Vin-的共模电平Vin,cm提升到Vref,同时电阻传递完整的差模信号,再由Vin+,Vin-连接NMOS差分对来实现整体电路,如图1所示。

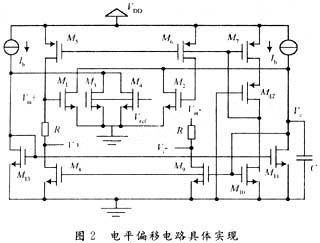

3 运算放大器的具体实现

反馈电路的实现如图2所示,其反馈过程如下:Vi+,Vi-的共模电平Vi,cm降低时,Vin+,Vin-的共模电Vin,cm降低,此时IDM1减小,IDM11增大,Vx点的电位升高,IDM8增大,电阻的端电压增大,Vin,cm升高。若Vref过高,由于Ib的大小和电流镜工作电压的限制,Vin,cm不会上升到Vtel的电平。为了M5与M6,M7的漏源电压近似相等,引入M12增强电流镜的匹配。

下面对反馈环路的稳定性进行分析,运放A的开环增益为:

由式(5)可以看出,电路工作时,需要保持M8漏源电压较小,则宽长较大,在相同的漏源电流下,Gm8不可能很小。所以在电路设计时,运放A的跨导Gm1应该可能小,补偿电容C应该较大,同时在版图设计中应该注意减小寄生电容Cp,以增强反馈的稳定性。

采用NMOS差分对的低压运算放大器,结构如图3所示,其两级直流增益可以分别为:

Av1=gmt1[rot8//gmt6rot6+1]rot4] (6)

Av2=gmt9(rot9//rot10) (7)

其中,gmt1,gmt6,gmt9分别为MT1,MT6,MT9的跨导,rot4,rot6,rot9,rot10分别为对应MOS管的输出电阻。

在设计电路过程中,MOS管应较大宽长比,保持漏源电压较小的同时,偏置电流也应适当减小,此时输出电阻较大,随共模电平波动也小,有助于低压下获得较大且稳定的增益。

4 模拟结果

在0.9V电源电压下,为使M3,M4工作在放大区,Vret可在0.62-1V之间取任意值,图4结果显示,在0-0.9V的共模电平范围内,当输入端共模电平Vi,cm<0.62V时,此时反馈电路使得M1,M2工作在放大区,内部共模电平Vin,cm保持0.62V恒定;Vi,cm>0.62V时,Vx电位降低,反馈电路停止工作,Vin,cm随Vi,cm增大而增大。

在10pF外接负载情况下,交流特性如图5所示。

在满幅度范围内,运算放大器的滞留增益,单位增益带宽和相位裕度相当稳定,具体参数如表1所示。

5 结论

本文基于标准CMOS工艺,设计了电源电压低至0.9V的运算放大器。模拟结果显示,在整个满幅度范围内,该运算放大器增益波动仅为0.01%,可用于低压低功耗的 SOC设计中。

关键字:功耗 低压 CMOS

编辑: 引用地址:低压CMOS满幅度恒定增益运算放大器设计

推荐阅读最新更新时间:2023-10-12 20:12

STM32—进入STOP模式后功耗下不去问题

背景: 最近调试板子进入STOP模式后发现电流为mA级别,功耗降不下去,最终发现是ADC开启后,忘记关闭了,导致有1.45mA的电流消耗。 内容: 利用HAL_PWR_EnterSTOPMode(PWR_MAINREGULATOR_ON, PWR_STOPENTRY_WFI)函数使板子进入STOP模式后,电流一直降不下去。之后调了好久,才发现调用ADC采集后,忘记把ADC关掉了,真是蛋疼啊。代码如下: HAL_ADC_Start(&hadc); //开启ADC HAL_ADC_PollForConversion(&hadc,10);//进行ADC 转换,然后对转换后数据进行换算。关键的一步

[单片机]

TigerSHARC结构的ADSP-TSl01及其应用

引 言 ADSP-TSl01是AD公司新一代TigerSHARC结构的数字信号处理器,具有多指令流多数据流(MIMD)结构;有两个计算单元,每个单元包括算术逻辑单元(ALU)、移位寄存器(shift)、乘法器(mult)、寄存器组(register files)。ADSP-TSl01性能比ADSP21160有显著提高,且与之兼容,使得以ADSP21160开发的产品升级快速、简捷。ADSP-TSl01是64位处理器,工作在250 MHz时钟下,可进行32位定点和32位或40位浮点运算,提供最高1500 MFLOPS(Millions of floating-pointoperations per second,每秒执行百万次浮点

[应用]

基于单片机CMOS汽车电子调节器

基于单片机CMOS汽车电子调节器引言

汽车电子化程度现已成为国际衡量汽车先进水平的重要标准,也正是由于这个原因推动和刺激当前汽车电子这一行业不断向前发展,各国都竞相发展,不断应用高新技术,提高汽车电气化性能,以获求更大市场。

目前汽车电压调节器通病就是稳定性差、寿命短、调节器的不稳定会导致发电机输入电压不稳定,从而影响整车用电设备的电源电压存在很大的波动,影响整车电路正常工作同时也会降低用电设备寿命,调节器的寿命短不仅会带来经济负担,对发电机输出电压的稳定也是不利的

如今单片式CM0S汽车电子调节器的出现,,从而减小了调节器的体积,使其可以和交流发电机制作在一起。就是将电压调节器设计成单片CMOS集成电路,这样既

[单片机]

日立试制出1Gbit/秒仅0.98mW的SerDes电路

日立制作所试制出了进行12.5Gbit/秒双向通信时的功耗仅为12.3mW的SerDes电路。换算成1Gbit/秒的功耗,仅为0.98mW,低于1mW。定位为削减以2010年6月为目标推进“IEEE802.3ba”标准化的100Gbit/秒以太网功耗的基础技术。据介绍,以 12.5bit/秒进行传输时的比特误码率为10-12,满足了数据传输速度为100Gbit/秒的以太网(Ethernet)标准。

此次主要通过两项电路技术的导入,大幅削减了功耗。分别是削减恒定电流的电路技术,以及将原来SerDes电路中需要的双系统时钟削减至单系统的电路技术。前者在维持输出信号水平时以电压模式驱动,在改变输出信号水平时以电流模式驱动。

[网络通信]

蓝牙低功耗市场战火热 众大厂争推SoC方案

蓝牙低功耗(Bluetooth Low Energy)芯片市场战况日益激烈。看好智能配件(Appcessory)市场成长商机,包括博通(Broadcom)、ROHM集团旗下的LAPIS 半导体、意法半导体(ST)、赛普拉斯(Cypress),以及戴乐格(Dialog)半导体等业者,皆竞相于今年推出蓝牙低功耗系统单芯片(SoC)解决方案,让市场竞争战火急遽升温。

Nordic产品管理总监Thomas Embla Bonnerud强调,nRF51系列蓝牙低功耗SoC 具备创新的硬体与软体架构,为该公司拓展智能配件市场的重要利器。

Nordic产品管理总监Thomas Embla Bonnerud表示,愈来愈

[模拟电子]

MCU低功耗设计(三)产品

引言:

能耗对电池供电的产品来说是一个重大问题,一旦电能耗尽设备将 罢工 。在《MCU低功耗设计(一)理论》中,我们介绍了节能的原理;在《MCU低功耗设计(二)实践》中,实测了STM8L151C8的低功耗值。

本文介绍无线通信产品的低功耗设计,首先实测MCU与射频芯片I/O设置的功耗,然后测试射频芯片不同模式下功耗,其次使用Contiki系统的energest模块实时跟踪能耗值,最后总结低功耗设计和展望无线组网中低功耗特征。Let sgo!

一、 无线通信产品简介

iWL881A无线通信模块是 长沙市锐米通信科技有限公司(www.rimelink.com) 的LoRa长距离低功耗产品(如下图),它

[单片机]

玩转DSP性能与功耗之间的“零和游戏”

“因为DSP牵扯到高速运算,所以功耗不会降到很低,”提及DSP的低功耗,一个工程师朋友小丁如是说。而德州仪器的16位单片机MSP430似乎成了其“低功耗”的代名词。

然而,近几年来,无论规模大小,处理器的客户都只单纯希望供应商专注于提高器件性能,但差不多从2007年开始,人们的想法发生了变化。开发人员现在首先要面对的问题是“我的设计在功耗方面有一定的限制,德州仪器如何在这方面帮我更多?”TI 首席科学家方进 (Gene Frantz) 在提及客户的反馈时说。

自然,处理器的低功耗问题也逐渐浮出水面,并有望成为下一个兵家的必争之地。工程师在探索新一代医疗、音频、工业以及新兴应用的设计方案时,发现如何在处理器的

[嵌入式]

μC/O-SII内核扩展接口的低功耗模式

引 言

随着消费类电子产品的功能日益复杂,在其中移植或固化实时操作系统已不是新鲜事了,如手机、PDA等等。对于该类产品,低功耗特性往往占有举足轻重的地位。如何在操作系统层面上,尽量降低系统功耗,是一个值得探讨的问题。一般来说,嵌入式CPU都具有低功耗的工作模式,如果在任务调度的空闲时间,使CPU进入这种模式,就能大幅度降低系统功耗。

本文以嵌入式实时操作系统μC/OS-II在飞思卡尔8位单片机HCS08GT60上的移植为例,详细讨论如何利用μC/OS-II给出的内核扩展接口,实现一个低功耗的嵌入式实时系统;进一步分析如何选择一种合适的低功耗模式。μC/OS-II是一种可移植、可固化、可裁剪的可剥夺型多任务内核。由于其源

[应用]

电气控制与PLC_第2版

电气控制与PLC_第2版 控制系统计算机辅助设计 — MATLAB语言与应用

控制系统计算机辅助设计 — MATLAB语言与应用

京公网安备 11010802033920号

京公网安备 11010802033920号