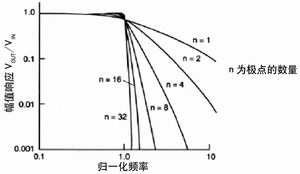

图1 几个低通滤波器的幅值响应与归一化频率的关系曲线。如果滤波器传递函数有多个极点(或阶数),则频率越高,衰减越快。

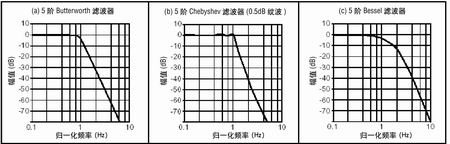

图2 Butterworth (a)、Chebyshev (b)和Bessel (c)低通5阶滤波器的频率响应

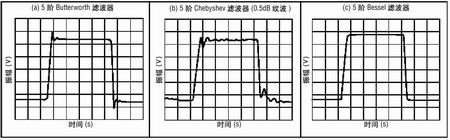

图3 Butterworth (a)、Chebyshev (b)和Bessel (c) 低通5阶滤波器的时间响应

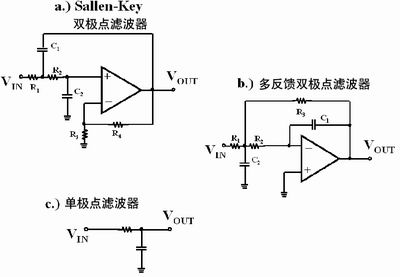

图4 Sallen-Key (a)和多反馈 (b)滤波器都是2阶,都有2个极点。单极点滤波器(c)是1阶滤波器。这些模块可以级联,以生成高阶滤波器。

ADC前必须使用滤波器

数据采集系统中,低通滤波器直接用于ADC之前,以降低高频噪声。关于数据采集系统中使用低通滤波器的合理性有两种错误的观点。第一种误解是:转换直流或低频信号时不需要低通滤波器。因为这些低频信号根本没有噪声,因此,设计人员认为不需要低通滤波器。假设有一个在低频状态下运行的系统,但有源/无源模拟器件会将高频噪声引入信号路径。电阻是一种常见的会产生噪声的无源器件。无论有没有电压或电流激励,每个电阻自身都会产生热电压噪声。在频率达到电阻的寄生电容(~0.5pF)开始衰减噪声的频率之前,这种噪声的幅值为常数。

运算放大器是有源器件,会在内部产生噪声。放大器的噪声主要是由前端差分输入对造成的。频率越低,噪声越高。此外,其它有源器件也会产生噪声,如电源内的开关动作。最后,噪声可以从外部信号辐射进入信号路径。

另外一个误解是:ADC的输入级会过滤掉高于采样频率的信号,或者采样频率会限制所转换的信号频率范围。这两点都是错误的,因为ADC是采样系统,所以无论信号的频率如何,它只是给信号拍一个“快照”。转换器根据所采集的各时间点的快照,在1/2采样频率的范围内给出信号的数字表示。这就是所谓的混叠。

综上所述,在设计含有ADC的系统时,必须在转换器前使用一个低通滤波器。如果ADC采样时信号路径中有不需要的信号,这些信号也会被转换并混叠在数字输出信号中。这样,就不可能在数字代码中区分好的信号和不好的信号。

确定滤波器阶数

如果想从信号中去除不需要的高频噪声,“砖墙式”滤波器似乎是理想的解决方案,但如前所述,设计一款“砖墙式”低通滤波器是不可行的。“砖墙式”滤波器极其不稳定,而且实现起来耗资不菲。下面会讨论一些标准滤波器技术,这里应注意,二阶低通有源滤波器需要1个运算放大器、2个电容和至少2个电阻。图1是二阶滤波器的频率响应与归一化滤波器频率的关系曲线。图1中滤波器的最高阶数是32阶。这尚未达到“砖墙式”滤波器的要求,但已经很难实现稳定的解决方案,而且需要16个运算放大器、32个电容和至少32个电阻。

滤波器的阶数应取决于应用的条件。必须考虑三个参数:信号的最大频率、噪声的预期幅值和转换器的最低有效位(LSB)大小。最后,ADC的采样频率必须达到系统的要求。

信号的最大频率是由应用需求决定的。当转换几赫兹的信号(或直流信号)时,可以将滤波器的转角频率调低,这样能提高系统的精度。其它情况下,通过模拟路径的信号会高达几千赫兹甚至几兆赫兹。

一旦确定了信号的最大频率,就该确定带外噪声的幅值了。噪声的幅值可以是几微伏、几毫伏,也可以高达模拟路径中的满幅。例如,通过增益为+200V/V的仪表放大器,经过放大的电阻噪声和放大噪声可以高达几百毫伏(峰-峰值)。

最后,必须确定ADC的LSB大小。优秀可靠的设计可以在转换器采样频率的1/2处将噪声衰减至LSB大小的1/4。如果噪声值还是太高,应该提高滤波器阶数,或者降低转角频率。

理解并估算了这三个参数后,就可以确定滤波器的阶数了。如果ADC是逐次逼近型(SAR)拓扑结构,数据采集系统应优先考虑采用4阶、5阶或6阶滤波器。使用Δ-Σ转换器和R/C时,单极点滤波器足矣。通常来讲,生产商提供这些器件的同时,会在产品数据手册中列出一些电阻和电容的值供使用者参考。

3种滤波器逼近类型的比较

最常用的滤波器逼近类型有Butterworth、Bessel和Chebyshev。图2和图3描述了每种滤波器设计的特点。还有几种滤波器本文不作讨论,包括Inverse Chebyshev、Elliptic和 Cauer 等。

Butterworth滤波器是目前最常用的电路设计。如图2a所示,幅频特性曲线在通带中幅值响应的平坦度最好。Butterworth滤波器转换频带的衰减率好于Bessel, 但是不如Chebyshev滤波器,阻带没有振荡。 图3a是Butterworth的阶跃响应曲线。这种滤波器在时域上有过冲和振荡,但小于Chebyshev滤波器。

Chebyshev低通滤波器转换频带的衰减率比Butterworth和Bessel滤波器的走势要陡(见图2b)。例如,5阶Butterworth的响应才能达到 3阶Chebyshev的转换带宽。尽管这种滤波器通带中有振荡,阻带中却没有。阶跃响应(见图3b)有一定程度的过冲和振荡。

Bessel滤波器通带中有平坦幅度响应(见图2c)。过了通带后,转换频带的衰减率比Butterworth或者Chebyshev滤波器的低,且阻带中没有振荡。这种滤波器的阶跃响应是上述所有滤波器中最好的,过冲和振荡都极小(见图3c)。

模拟电路拓扑

如图4所示,这些滤波器都可以利用放大器拓扑结构实现。双极点压控电压源常以Sallen-Key滤波器实现(见图4a),这种滤波器的直流增益为正值。在Sallen-Key滤波器中,直流增益可能大于1,滤波器的阶数为2。这些滤波器的阶数由电阻值和电容值R1、R2、C1 和C2决定。

图4b是2阶低通滤波器的双极点多反馈实现。这 种滤波器也可以简称为多反馈滤波器。该滤波器的直流增益将信号反相,等于R1和R2的比值。极点数由R1、R3、C1和C2的值决定。图4c是单极点有源滤波器。这些滤波器可以级联,以实现高阶滤波器。例如,单极点滤波器加上2个Sallen-Key滤波器,就是5阶滤波器。

这些滤波器的设计方程式可以在参考资料中找到。并可以通过诸如Microchip公司的FilterLab模拟滤波软件工具进行设计。该滤波器程序可以描述所需滤波器的频率响应,提供易于实现的电路图和用于模拟的SPICE 宏模型。

结语

模拟滤波器是数据采集系统的关键组成部分。如果没有模拟滤波器,频率超出ADC采样带宽一半的信号会混叠进信号路径。一旦信号在数字化的过程中被混叠,就不可能区分带内和带外噪声频率。

上一篇:集成运算放大器输出过流保护电路

下一篇:CMOS多频段低噪声放大器设计

推荐阅读最新更新时间:2023-10-12 20:12

电子电路识图、应用与检测 (韩雪涛)

电子电路识图、应用与检测 (韩雪涛) Verilog HDL数字集成电路设计原理与应用

Verilog HDL数字集成电路设计原理与应用

京公网安备 11010802033920号

京公网安备 11010802033920号