分段DAC

当我们需要设计一个具有特定性能的DAC时,很可能没有任何一种架构是理想的。这种情况下,可以将两个或更多DAC组合成一个更高分辨率的DAC,以获得所需的性能。这些DAC可以是同一类型,也可以是不同类型,各DAC的分辨率无需相同。

原则上,一个DAC处理MSB,另一个DAC处理LSB,其输出以某种方式相加。这一过程称为“分段”,这些更复杂的结构称为“分段DAC”。有许多不同类型的分段DAC,本指南不可能逐一说明,但会介绍其中的几种。

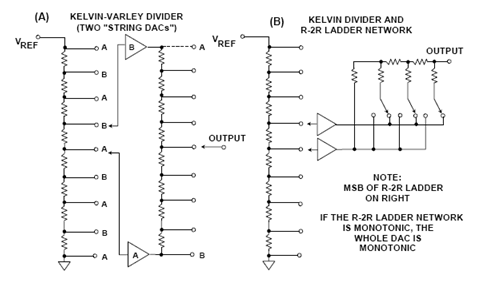

图1显示了两类分段电压输出DAC。图1A中的架构有时称为Kelvin-Varley分压器,由两个或更多“串DAC”组成。第一级与第二级之间存在缓冲器,因此第二个串DAC不会加载第一个串DAC,该串中的电阻值无需与另一个串中的电阻值相同。然而,各串中的所有电阻必须彼此相等,否则DAC将不是线性的。示例的第一级和第二级均为3位,但为了具有普遍意义,我们称第一(MSB)级的分辨率为M位,第二(LSB)级的分辨率为K位,总分辨率为N = M + K位。MSB DAC具有2M个等值电阻,LSB DAC具有2K个等值电阻。

图1:分段式电压-输出DAC

当然,缓冲放大器具有失调,这可能会在缓冲分段串DAC中造成非单调性。在缓冲Kelvin-Varley分压器缓冲器的更简单配置中(图1A),缓冲器A总是“低于”(电位低于)缓冲器B,LSB串DAC上标“A”的额外抽头是不必要的。数据解码电路仅为两个优先级编码器。然而,在此配置中,缓冲器失调可能会造成非单调性。

但是,如果将MSB串DAC的解码电路做得更复杂一点,使得缓冲器A只能连接到MSB串DAC标“A”的抽头,缓冲器B只能连接到标“B”的抽头,则缓冲器失调将无法造成非单调性。当然,LSB串DAC解码必须改变方向, 缓冲器需要跳跃连接到另一端,LSB串DAC的抽头A和B不需要交替,但这需要略微复杂一点的逻辑,而性能的提高证明这样做是值得的。

也可以不使用第二个电阻串,而是使用一个二进制DAC来产生三个LSB,如图1B所示。制造极高分辨率的R-2R梯形电阻网络非常困难,更确切地说,很难将其调整为单调性。因此,常见的情况是LSB使用由梯形电阻网络,2到5个MSB则使用其它结构来合成高分辨率DAC。图1B所示的电压输出DAC由一个3位串DAC和一个3位缓冲电压模式梯形电阻网络组成。

图2:分段无缓冲串DAC使用专利架构

无缓冲的分段串DAC架构如图2所示。在原理上,这种形式更巧妙,并且可以通过CMOS工艺制造(它能制造电阻和开关,但不能制造放大器),因此也更便宜。这种架构本身即具备单调性。

本例中,两个串中的电阻必须等值,唯一的例外是MSB串中的顶端电阻必须较小(其它电阻值的1/2K),此外LSB串具有2K – 1个电阻,而不是2K个。由于没有缓冲器,LSB串看起来像是与它切换并加载的MSB串中的电阻并联,这就使得该MSB电阻上的电压降低LSB串 DAC的1 LSB,而这正是所需要的结果。由于无缓冲,此DAC的输出阻抗随着数字代码的改变而变化。

为了更好地了解这一巧妙的原理,对于图2所示的由两个3位串DAC组成的6位分段DAC,我们计算并标示出了各抽头的实际电压。建议读者将第二个串DAC连接到第一个串DAC中的任何其它电阻两端,完成这一简单的分析过程并验证结果。关于无缓冲分段串DAC的详细数学分析,请参阅ADI公司的Dennis Dempsey和Christopher Gorman于1997年申请的相关专利(参考文献1)。

适合视频、通信和其它高频重构应用的极高速DAC常常采用完全解码电流源阵列来构建,两或三个LSB可以使用二进制加权电流源。此类DAC在高频时的失真非常低,这一点极其重要,而且设计中还有几个重要问题需要考虑。

首先,电流不是接通或关闭,而是被导向一个地方或另一个地方。在高速运行时,关闭电流常常会引起感性尖峰,由于电容充电,它一般需要比电流导向更长的时间。

其次,芯片上开关电流所需的电压变化应尽可能小。电压变化会导致更多电荷流入杂散电容,电荷耦合的毛刺也会更大。

最后,解码必须在新数据应用到DAC之前完成,使得所有数据均已就绪,可以同时应用到DAC中的所有开关。其实现方式一般是对一个完全解码阵列中的各个开关使用独立的并联锁存器。如果所有开关瞬间同时改变状态,就不会有偏斜毛刺。只要精心设计芯片周围的传播延迟以及开关电阻和杂散电容的时间常数,就能非常好地实现更新同步机制,因而毛刺相关的失真将非常小。

图3显示了分段电流输出DAC结构的两个例子。图3A所示为利用电阻方法实现7位DAC,其中3个MSB通过完全解码获得,4个LSB来自一个R-2R网络。图3B所示为使用电流源的类似实现方案。对于当今的高速重构DAC,电流源方案是目前最受欢迎的实现方法。

图3:分段电流输出DAC: (A)电阻方案;(B)电流源方案

此外,常常也需要利用多个完全解码DAC来构成整个DAC。图4所示的6位DAC由两个完全解码3位DAC构成。如前所述,为使输出毛刺最小,必须利用并联锁存器同时驱动这些电流开关。

图4:基于两个3位温度计DAC的6位电流输出分段DAC

AD977514位160 MSPS(输入)/400 MSPS(输出)TxDAC®使用三段,如图5所示。AD977x系列的其它产品和AD985x系列也使用同样的基本内核。

图5:AD9775TxDAC®14位CMOS DAC内核

前5位(MSB)为完全解码型,驱动31个同等权重的电流开关,各开关提供512 LSB的电流。后续4位解码为15条线,驱动15个电流开关,各开关提供32 LSB的电流。最后5个LSB位被锁存,并驱动一个传统二进制加权DAC,该DAC针对每个输出电平提供1 LSB。为了实现这种超低毛刺架构,总共需要51个电流开关和锁存器。

TxDAC系列中的基本电流开关单元由图6所示的差分PMOS晶体管对组成。这些差分对通过低电平逻辑驱动,以便最大程度地降低开关瞬变和时间偏斜。DAC输出为对称的差分电流,有助于减少偶数阶失真产物(特别是驱动变压器或运放差分电流电压转换器等差分输出时)。

AD977x TxDAC®系列和AD985x-DDS系列的总体架构实现了功耗与性能的出色平衡,通过标准CMOS工艺就可以实现完整的DAC功能,无需薄膜电阻。

图6:PMOS晶体管电流开关

参考文献:

1. Dennis Dempsey and Christopher Gorman, "Digital-to-Analog Converter," U.S. Patent 5,969,657, filed July 27, 1997, issued October 19, 1999.(描述一款出色的分段无缓冲串DAC解决方案)。

2. John A. Schoeff, "An Inherently Monotonic 12 Bit DAC," IEEE Journal of Solid State Circuits, Vol. SC-14, No. 6, December 1979, pp. 904-911.(描述首个使用分段的一款单调DAC)。

3. Walt Kester, Analog-Digital Conversion, Analog Devices, 2004, ISBN 0-916550-27-3, Chapter 3.另见The Data Conversion Handbook,Elsevier/Newnes, 2005, ISBN 0-7506-7841-0, Chapter 3.

上一篇:SAR ADC的隔离

下一篇:提高迟滞,实现平稳的欠压和过压闭锁

推荐阅读最新更新时间:2024-11-11 22:04

- 安森美推出业界领先的模拟和混合信号平台

- 贸泽开售用于快速开发精密数据采集系统的 Analog Devices ADAQ7767-1 μModule DAQ解决方案

- 国产高精度、高速率ADC芯片,正在崛起

- 集Hi-Fi、智能和USB多通道等特征于一体的微控制器——迎接数字音频新时代

- 采用电容型PGA,纳芯微推出高精密多通道24/16位Δ-Σ型ADC

- 全差分放大器为精密数据采集信号链提供高压低噪声信号

- 意法半导体推出灵活、节省空间的车载音频 D类放大器,新增针对汽车应用优化的诊断功能

- ADALM2000实验:变压器

- 【TE Connectivity】泰科电池组端子上新|10,000次插配次数,寿命值Up!

- 一种基于洞洞板的面包板

- LTC1666 的典型应用 - 12 位 50Msps DAC

- NSI45090JDT4G可调电流LED串并联CCR的典型应用

- SI7051-A20-IM_DK

- 具有低压逻辑接口的 LTC4419CMSE 备用电池的典型应用电路

- 具有最大功率点跟踪功能的 LTC4162IUFD-FAD 太阳能供电 3 节 3.2A 充电器的典型应用

- LTC3886IUKG 具有检测电阻器的高效率、250kHz、3 相、2.5V Plus、1 相 5V 降压转换器的典型应用电路

- 使用 RP40-2412DFR DC/DC 转换器并根据 EN55022 A 类(单输出)进行 EMC 滤波的典型应用

- 使用 Infineon Technologies AG 的 IRPT1057A 的参考设计

- [实测成功]XL4501搭配IP2163的快充电路

【Follow me第二季第2期】Arduion UR4 作业提交代码

【Follow me第二季第2期】Arduion UR4 作业提交代码 单片机C语言编程与Proteus仿真技术 (徐爱钧)

单片机C语言编程与Proteus仿真技术 (徐爱钧) CADENCE高速电路板设计与仿真:原理图与PCB设计

CADENCE高速电路板设计与仿真:原理图与PCB设计

京公网安备 11010802033920号

京公网安备 11010802033920号