引言

ADS8361 是一款采样速率为 500kSPS 的 16 位双路模数转换器 (ADC),该转换器具有 4 个全差分输入通道,两两一对,以实现同步高速信号采集。采样保持放大器的输入端是全差分的,此外, ADC 的输入端也保持为全差分。这使该 ADC 具有卓越的共模抑制能力:在 50kHz 时为 80dB,这在高噪声环境下非常重要。

新型 MSP430F2013 等 MSP430 器件具有通用串行接口(USI),因而可用于非常简单直接的接口,该接口不需要“粘接逻辑”且需要的软件开销也很少。有的应用要求对同步数据采集的通道实现精确定时,这时我们就能用这种接口来获取所需的系统结果。

硬件

ADS8361EVM

ADS8361 是德州仪器 (TI) 推出的串行 ADC 电机控制产品系列产品。EVM 提供了相关平台,以演示配合不同 TI DSP 与微控制器时ADS8361 ADC 的功能,并针对定制的最终用户应用提供了方便地存取所有模拟与数字信号的功能。

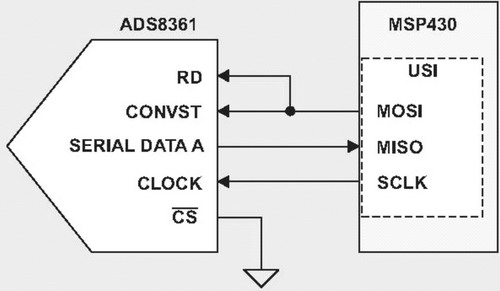

图1 硬件接口结构图

eZ430-F2013 开发工具

eZ430-F2013 是完整的 MSP430 开发工具,包括评估 MSP430F2013 所需的全部软硬件。我们用可便利的 USB 存储棒提供该硬件。eZ430-F2013 采用 IAR 嵌入式工作台集成开发环境 (IDE),以提供完整的仿真功能,该器件提供独立系统设计与可拆卸目标板两种选项,以便于集成至现有设计中。更多详情,敬请访问:www.ti.com/ez430。

硬件接口

连接 eZ430-F2013 与 ADS8361EVM 的最低要求是采用简单的三线接口(见表 1)。硬件连接如图 1 所示。ADS8361 的 CLOCK、(RD + CONVST) 与 Serial Data A 引脚分别连接至 USI 端口的 SCLK、MOSI 与 MISO 引脚。chip select (CS) 引脚接地,因为端口上只放置一个 ADC。如果总线上挂接多个器件,那么芯片选择引脚应由 MSP430 器件上可用的 GPIO 控制。

软件接口

MSP430 的所有软件都采用 IAR 嵌入式工作台 (Kickstart 版本) 编写编译。该软件是 IDE 的免费版,并可在 www.ti.com/ez430 网站的工具支持 (TOOL SUPPORT) 部分下载。您也可请求获得示例中使用的代码。

USI 设置

USI 模块提供支持同步串行通信方案的基本功能。USI 具有内置硬件功能,从而简化了 SPI 通信的实施。此外,USI 模块还具有中断功能,能进一步降低软件的开销。

图2 完整的单通道转换周期

USI 控制寄存器 0 和 1(USICTL0 和 USICTL1)设置串行接口的基本操作。通过在 USICTL0 中设置 3, 5, 6 和 7 位,可在 SPI 主模式下配置端口。此外,还可在 USICTL1 中设置 USI 计数器中断,从而以最小的软件开销有效地实现 SPI 通信。

串行时钟的极性、信号源及速度都可通过设置 USI 时钟控制寄存器 (USICKCTL) 得到控制。就本文而言,时钟极性设为零(保持为低),时钟源为 SMCLK,分频系数为一。

位时钟和移位寄存器配置在 USI 端口中实现控制,由 USI 位计数寄存器 (USICNT) 的位设置决定。USICNT 寄存器有 5 位,每次可提供多达 32 个 SCLK 周期。如果 USICNT 设为 0×13,MSP430 将在每个转换周期向 ADS8361 发送 19 个串行时钟。将 USICNT 寄存器的 USI16B 位置 1,可使移位寄存器发挥 16 位发送/接收缓存的作用。所发送的数据根据 MSB 排列,以首个 SCLK 周期开始。

开始转换

我们将 USI 端口的 MOSI 输出连接到 ADS8361 上的 RD 和 CONVST 输入上,就能开始转换周期,转换结果提供给该器件的串行数据输出引脚。

ADS8361 将在第四个 SCLK? 周期开始输出转换结果(先是 MSB)。由于移位寄存器保留最后 16 位的接收数据,因此我们采集全部 16 位转换结果,用于进一步的处理。图 2 中的时序图显示了整个过程。

ADS8361 工作模式

ADS8361 有四种由 M0 及 M1 引脚控制的工作模式。ADS8361EVM 提供的跳线可静态设置工作模式。在 MSP430 上采用 GPIO 输出后,还能通过微控制器来控制工作模式。

就双通道工作而言,EVM 应在模式 I 和 II 中配置。根据所采用 MSP430 器件的不同,用户在决定如何接收转换结果时有着若干选择。具有多个串行端口的器件可同时从 ADS8361 的 Serial Data A 与 Serial Data B 输出引脚接收数据。这种方法将设置一个端口作为 SPI 主设备而另一个端口为 SPI 从设备。主 SPI 端口将与从端口共享 SCLK,两个串行输出引脚将被连接至 MISO 与 MOSI。

双通道同步采样就 eZ430-F2013 而言,由于只有一个串行端口,也就是说,ADS8361 必须在 Mode II 中设置,才能从同步采样的两个输入通道接收转换结果。该模式将两个转换结果都提供给 Serial Data A 输出引脚(见图 3 )。

图3 完整的双通道转换周期

ADS8361 通道 ID 位

ADS8361 的串行输出流还包括双通道 ID 位,这样控制器就能用软件方法来破译所接收的通道信息。首个 ID 位确定了通道对 A 或 B。第二个 ID 位决定了采样通道 0 或 1。在 Mode II 工作模式下,两个输入通道被转换,输出数据流中包含一个 ID 位。

在该模式中,我们不使用 A/B 通道 ID 位,因为输入采样对取决于 ADS8361 的 A0 输入控制引脚。当 A0 为低电平时,对通道 A0/B0 输入对进行采样。当 A0 为高电平,对通道 A1/B1 输入对进行采样。

ADS8361EVM 的跳线可通过 A0 引脚静态设置输入对。如果需要的话,我们也可通过 MSP430 上的 GPIO来控制上述工作,这样用户就能实现四通道工作,即两对同步采样输入通道。

四通道采样

Mode III 及 IV 能帮助用户实现 ADS8361 的四通道工作。Mode III 提供 Serial Data A 与 Serial Data B 输出的数据。在此模式下,接收所有四个转换的数据要求将两个串行端口如前所述配置为主从关系。

Mode IV 可使一个串行端口通过 Serial Data A 输出引脚来接收所有四个转换结果。在此模式下,A/B 和 0/1 通道 ID 位都可传递转换结果。这种情况下,如果配合使用 eZ430-F2013 器件,那么移位寄存器会丢失 ID 位,从而导致问题发生。我们可通过软件恢复 ID 位,但这会增加软件开销,并扩大不必要的复杂性。

在四通道顺序工作模式下,我们可通过特定方法来对 ADS8361 进行初始化,这样就能保证通道的完整性,而根本无需破译 ID 位。如果使用 GPIO,我们可在程序开始处用简单的软件循环 (software loop)来完成上述工作,从而灵活地对 A0、M0 与 M1 输入的状态进行操控。此外,我们也可以完全忽视第一组转换结果。默认状态下,ADS8361 启动 Mode I;如果启动时 M0 和 M1 固定为 VCC ,那么器件在第二次转换周期会进入 Mode IV 工作模式,这使第三次 SPI 传输开始提供 A0 通道的数据,随后顺序提供 B0、A1 和 B1 通道的数据。

结语

与 MSP430 处理器的 USI 端口配合使用高性能 ADS8361,这是一项相对简单而直接的工作,几乎不会造成什么软件开销,也不需要像前代 MSP430 产品中老式的 UART 端口那样采用简单的 8 位 SPI 接口来移动或连接转换结果。本文介绍的接口方式为那些要求多通道同时进行数据采集的 MSP430 应用带来了更高的灵活性。

上一篇:AD7705在电子秤中的应用

下一篇:数字电位器的应用

推荐阅读最新更新时间:2023-10-12 20:12

西电-印刷电路板(PCB)设计指南_1-99

西电-印刷电路板(PCB)设计指南_1-99 blinker_app_control_the_led_on_the_feather_border.

blinker_app_control_the_led_on_the_feather_border. 零基础学电子与Arduino:给编程新手的开发板入门指南

零基础学电子与Arduino:给编程新手的开发板入门指南

京公网安备 11010802033920号

京公网安备 11010802033920号